1. 前言

最近在做以太網相關的東西,其中一個其中想要使用MAC通過光電轉換模塊來完成數據的收發。在Artix7系列FPGA當中,有GTP這個高速收發器。我手上的板子上的核心芯片是ZYNQ7015,這是一個帶一個QUAD的ZYNQ FPGA,上面的收發器是GTP。對于其他稍微高端一點的ZYNQ上帶有收發器應該是GTH/GTX的。但是,只是實現一個千兆網,使用GTP應該是足夠了。因此需要了解收發器的使用。

??

2. UG482

2.1 整體結構

因為手上的ZYNQ芯片帶有的收發器是GTP,因此需要參考的手冊是ug482,對于GTH/GTX則需要參考ug476。其實GTP和GTX/GTH還是比較相似的,GTP內部的結構和GTX/GTH稍有不同。

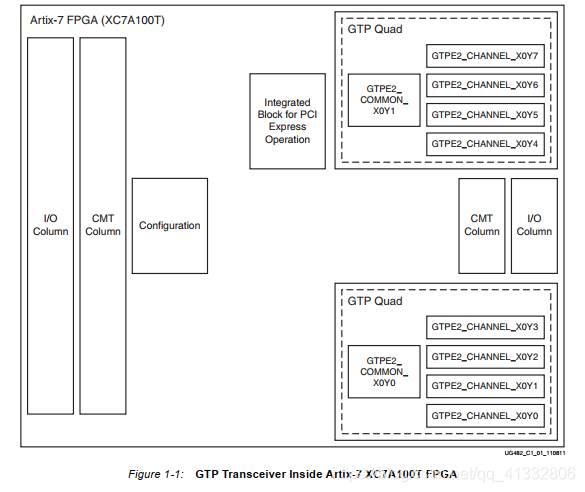

上面的圖是手冊上給出的100T內部的收發器分布圖,可以看到對于Artix7系列FPGA的收發器,其是分布在上下兩側的,這與GTX/GTH單列放置是一個區別。

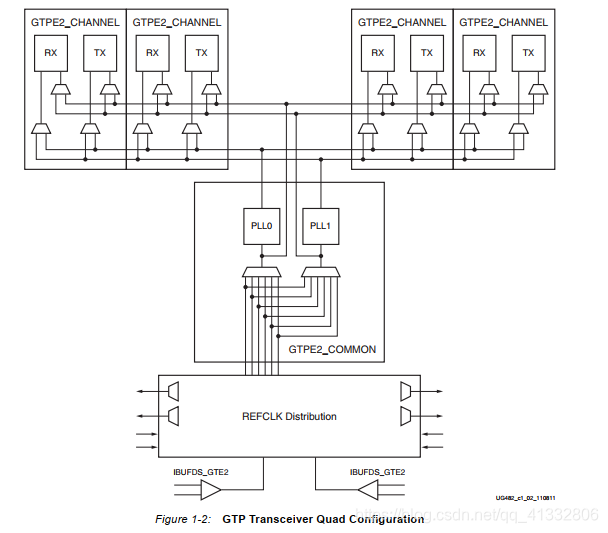

下圖是每個QUAD內部的結構:一個QUAD中包含4個channel和一個COMMON。GTPE2_COMMON 中包含兩個PLL(PLL0/PLL1),使用到收發器時,COMMON原語必須被例化。每個CHANNEL中都包含一個接收器和一個發送器。

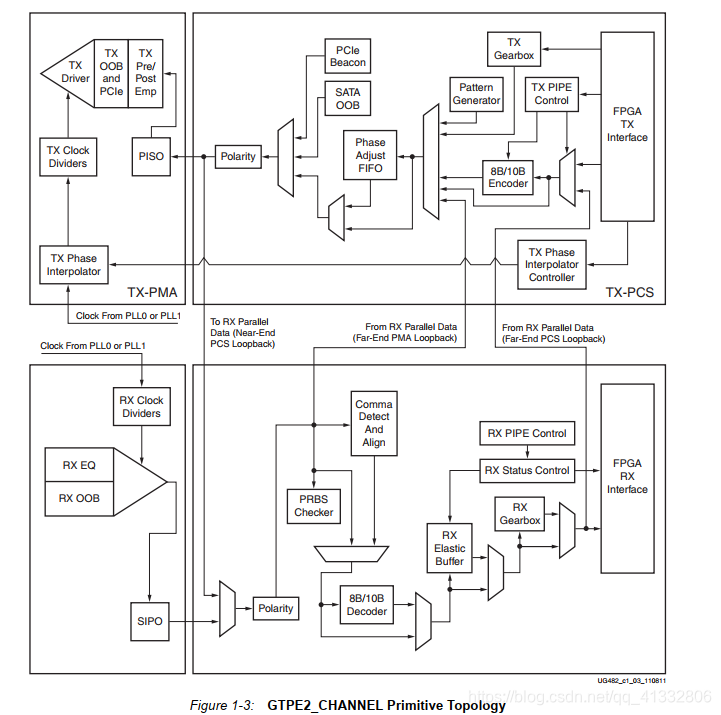

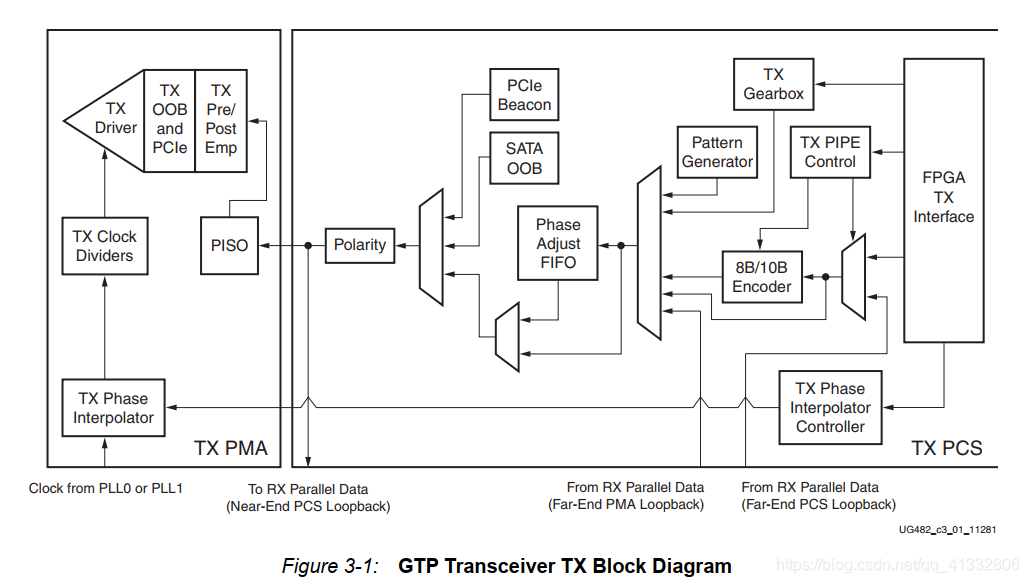

??下圖是收發器每個CHANNEL中的結構:TX/RX都包含兩部分,其中PCS是物理編碼層,PMA是物理媒介層。

2.2參考時鐘

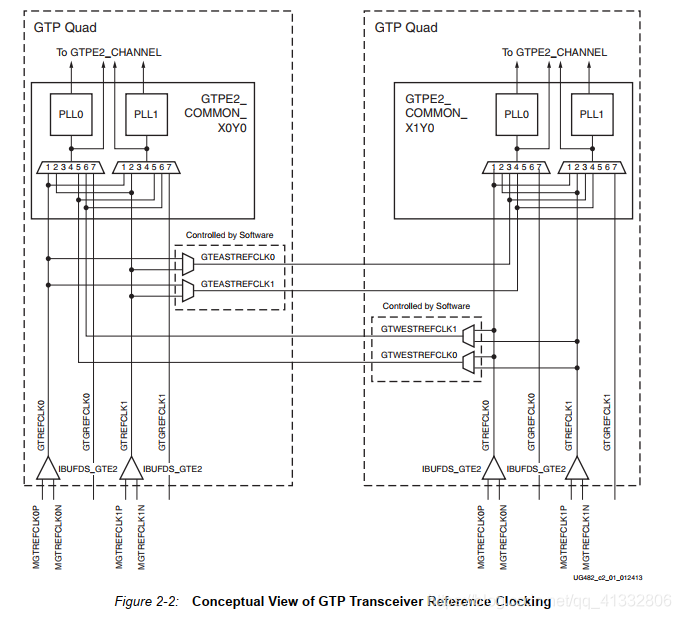

GTP中的參考時鐘選項和GTX/GTH中略有不同,在GTH/GTX中,支持南北方向的時鐘路由,在GTP當中支持東西方向的時鐘路由。

??一個QUAD中包含4個GTPE2_CHANNEL原語,一個GTPE2_COMMON 原語,兩個外部參考時鐘引腳以及專用參考時鐘的路由。

??在A7系列FPGA當中,位于上半部分的收發器可以進行時鐘的共享,位于下半部分的收發器可以進行時鐘的共享。

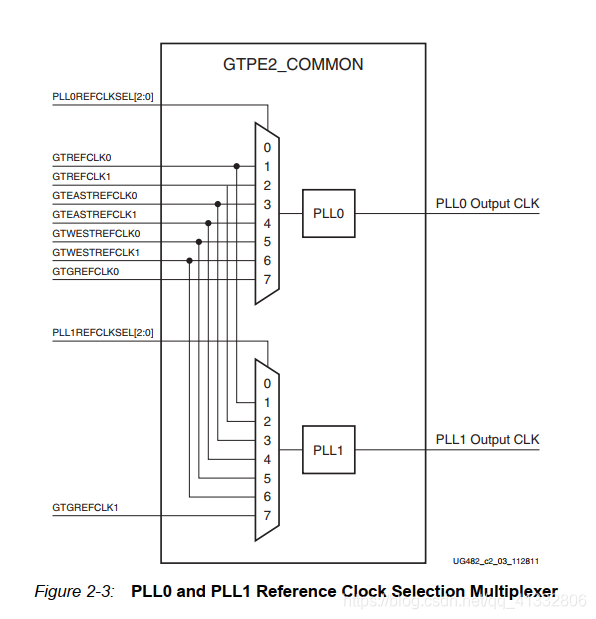

在下圖中,COMMON原語的時鐘輸入可以有以下幾種:兩個參考時鐘,來自另一個QUAD的參考時鐘

2.2.1COMMON參考時鐘

GTP COMMON中時鐘的選擇:common中的每一個PLL時鐘來源都包含7個分別為:一個用于測試的時鐘,兩個外部參考時鐘,兩個東向參考時鐘,兩個西向參考時鐘,通過PLL0/1REFCLKSEL 來選擇具體使用到的時鐘參考源。

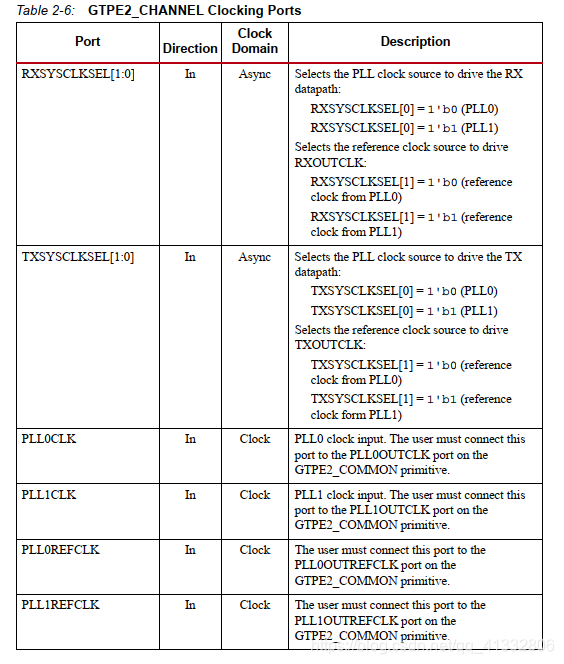

2.2.2 CHANNEL 參考時鐘

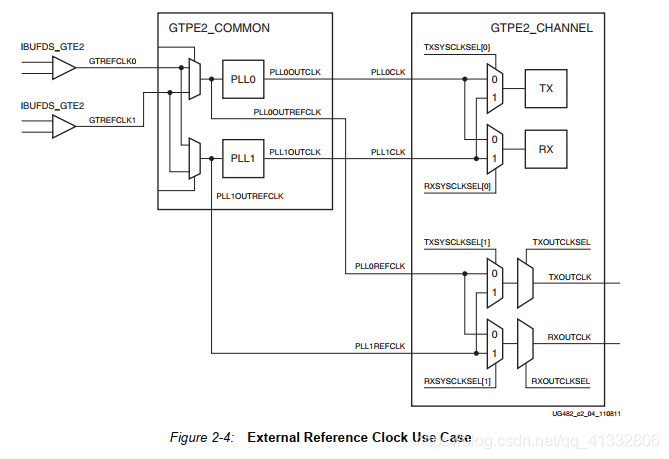

GTP CHANNEL的端口具體可以分為,用于選擇RX/TX的參考時鐘和數據的參考時鐘,參考時鐘可以來自PLL,也可以來自PLL的參考時鐘。

??下圖是包含了各種情況的時鐘路由方式

??值得說明的是,這些端口和選項,在GTP的向導這個IP中,都不用可以去記,在向導里面只需設置就可以,IP會自動生成這些邏輯。

3 發送器TX

3.1 TX interface

&esmp;TX interface 簡單來說,就是位于FPGA邏輯側和收發器發送這一側的端口。從這里開始收發器會將FPGA中想要發送的數據進行發送。這里是收發器發送數據的第一步。TX Interface 是與用于邏輯聯系最緊密的一個模塊,該模塊決定了FPGA側數據的位寬和收發器傳輸的線速率,并且該模塊還與數據的編碼有關。

3.1.1 數據位寬

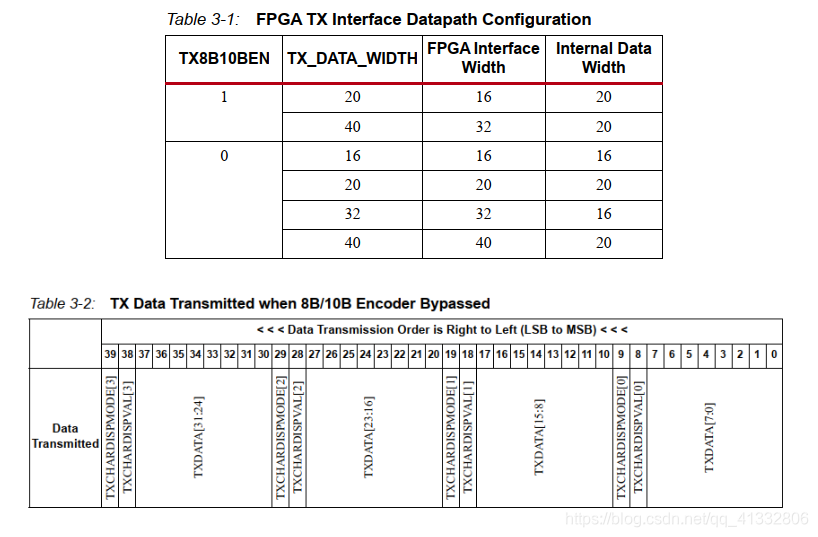

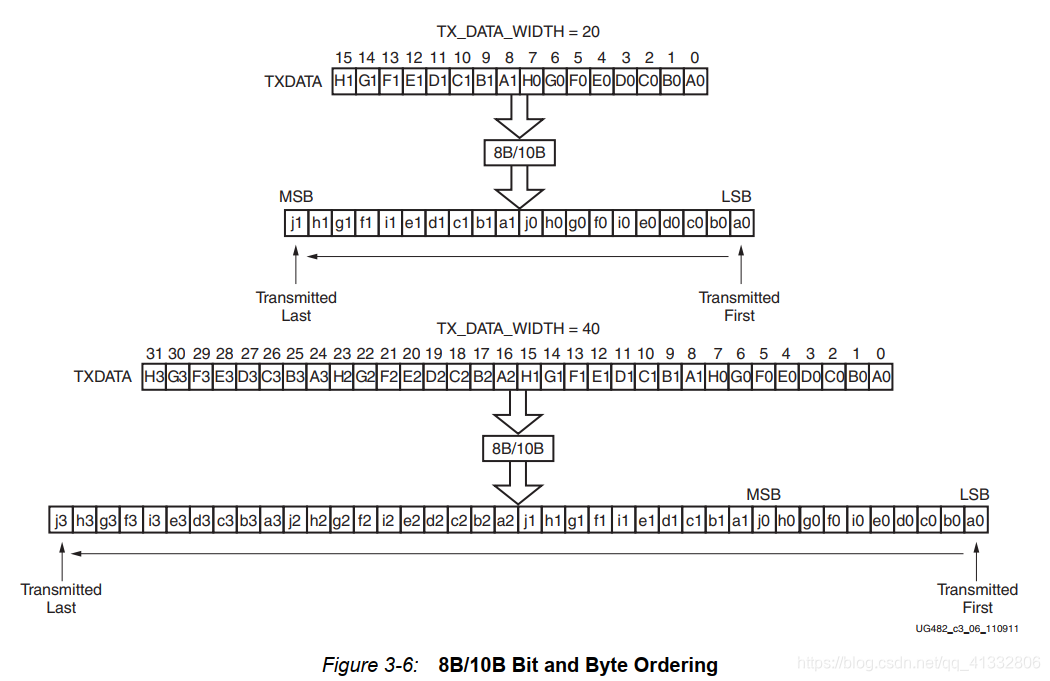

GTP包含2字節的內部數據通道,TX 部分的Interface 的數據位寬通過TX_DATA_WIDTH 屬性來配置。當8B/10B編碼被使能的時候,TX_DATA_WIDTH必須被配置為20bit/bit。當不使能8B/10B編碼的時候,TX_DATA_WIDTH 可以被配置為16,20,32,40。

??當不使用8B/10B編碼的時候,必須使用TXCHARDISPMODE & TXCHARDISPVAL 來對位寬進行擴充,擴充位寬的方法是每1byte用戶數據需要1bit 的TXCHARDISPMODE和 1bit 的TXCHARDISPVAL來對數據進行擴充。如圖中的Table 3-2 所示。

3.1.2 用戶時鐘

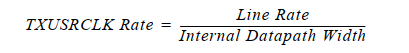

FPGA TX接口包含兩個并行時鐘:TXUSRCLK和TXUSRCLK2。TXUSRCLK是GTP內部PCS部分的內部時鐘,TXUSRCLK所需要的速率取決于GTPE2_CHANNEL原語內部的數據路徑寬度和TX 的線速率。

??TXUSRCLK2是所有進入到GTP TX接口的信號的主要的同步時鐘。進入到TXUSRCLK的大多數數據在TXUSRCLK的上升沿進行采樣。TXUSRCLK2和TXUSRCLK具有固定的頻率關系。根據TX_DATA_WIDTH的值來確定:

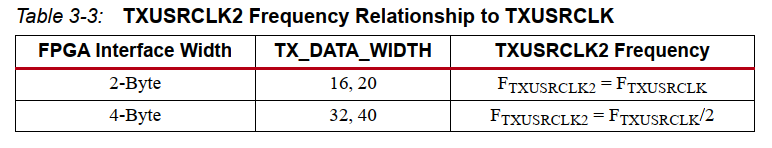

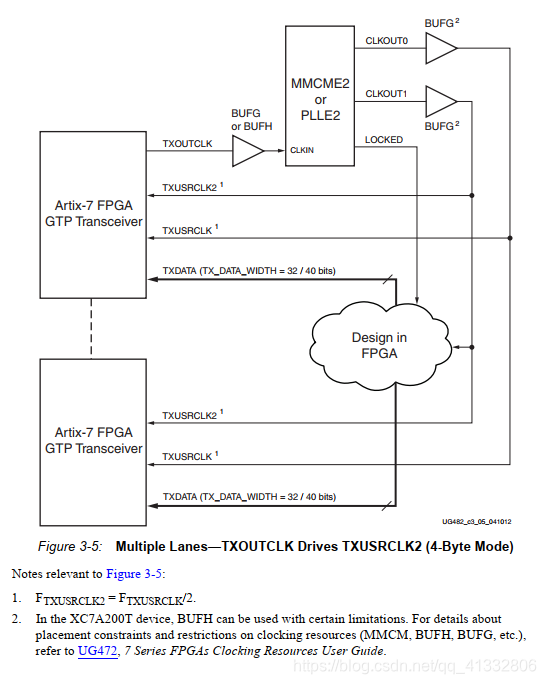

??從上面的圖中可以看出,TXUSRCLK2的時鐘頻率在不同的模式下可以為TXUSRCLK或者TXUSRCLK的一半,TXUSRCLK 和TXUSRCLK2一般都是由TX接口上的TXOUTCLK來生成的。下面的兩幅圖中,可以看到TXUSRCLK和TXUSRCLK在不同模式下的生成的示意圖。

??在這之中,TXUSRCLK2一般都是給到用戶側邏輯來使用的,也就是說,用戶在使用GTP發送數據時,一般都使用TXUSRCLK2來進行發送。

3.1.3 具體例子

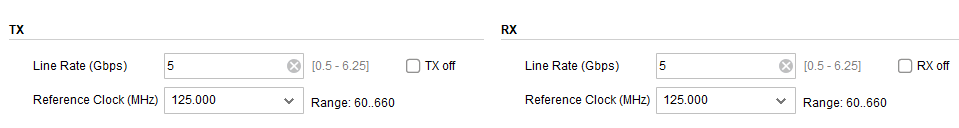

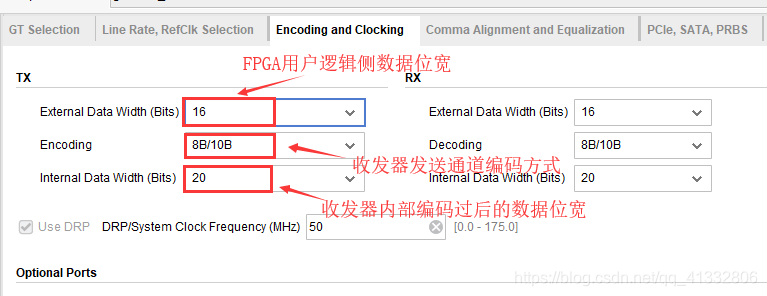

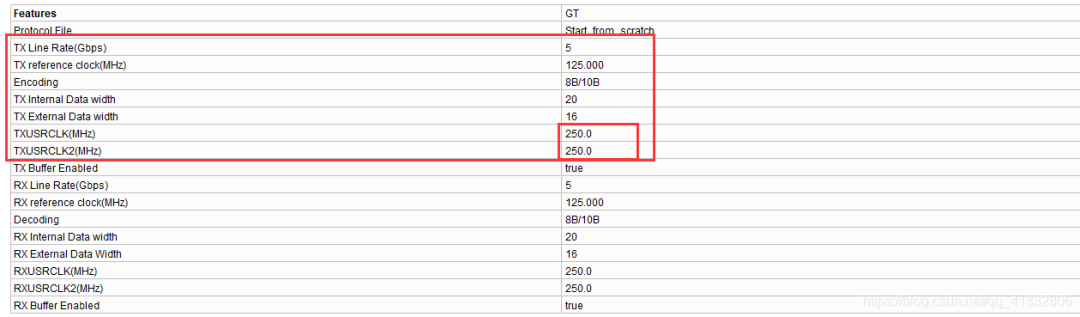

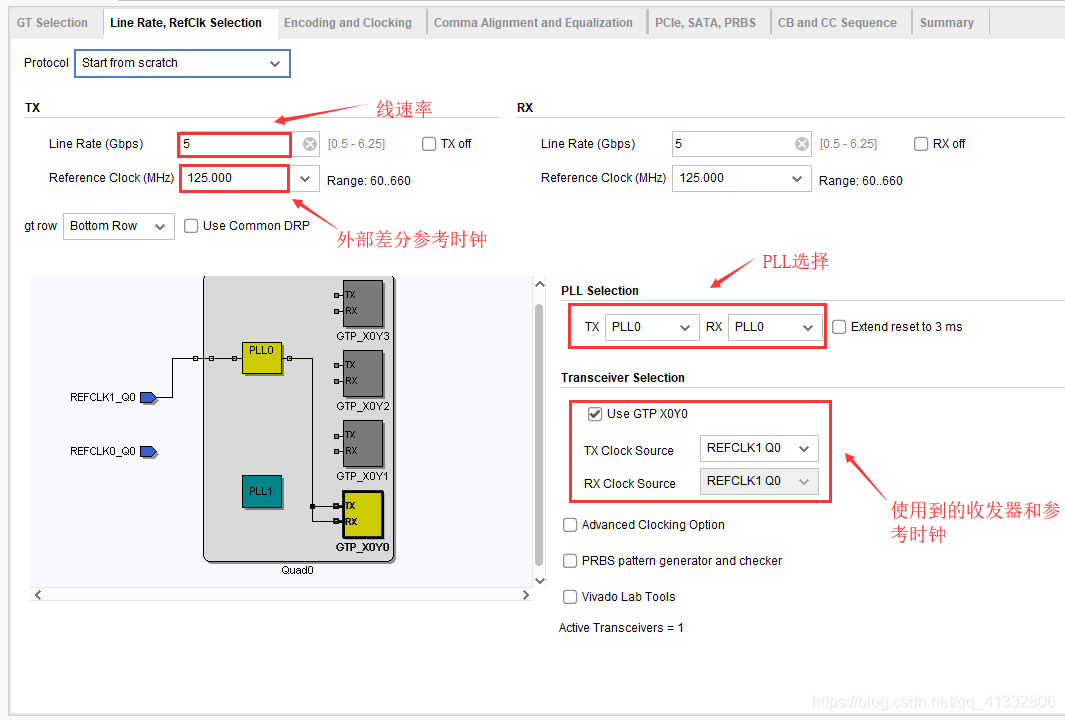

下圖中設置了線速率為5GT,參考時鐘時根據開發板上的參考時鐘來指定的。

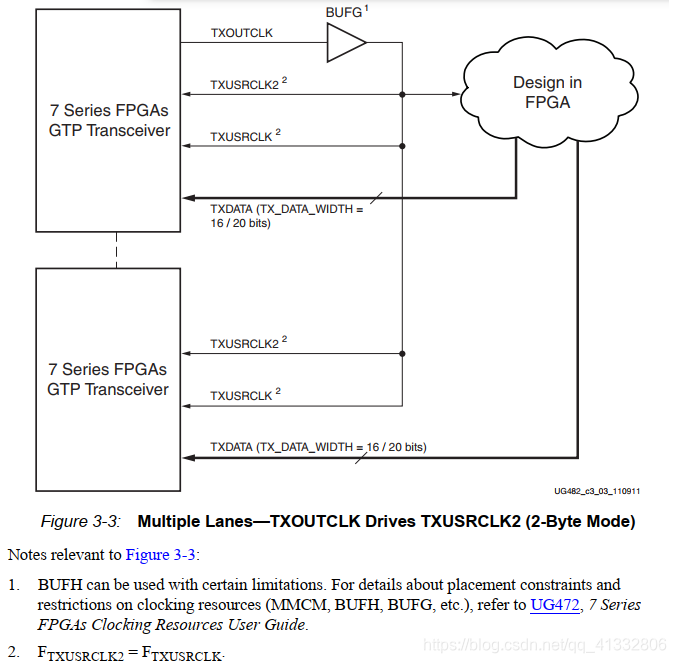

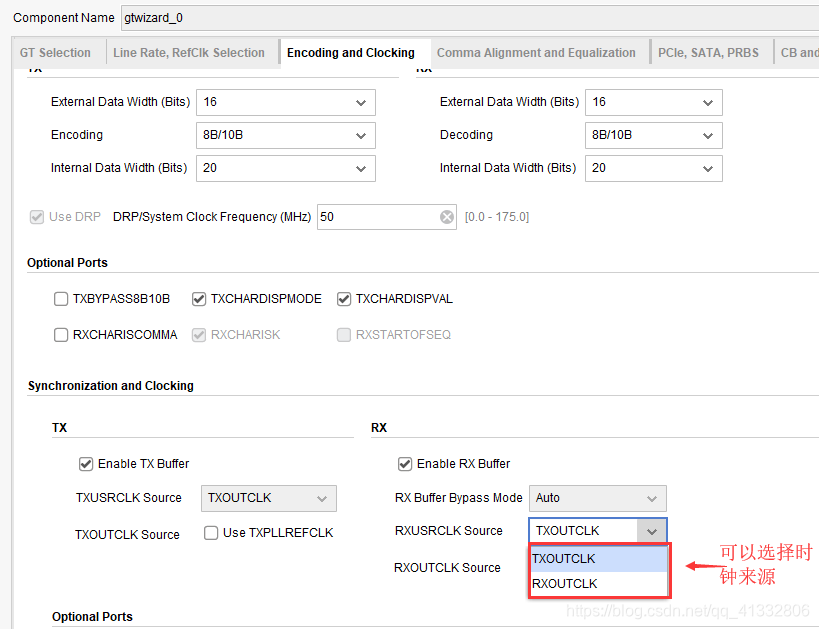

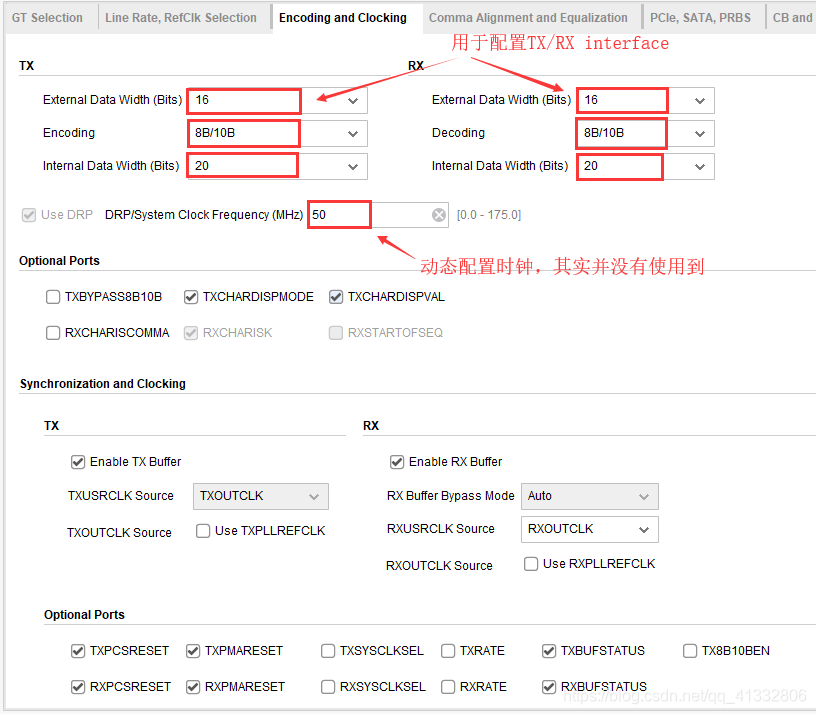

在使用IP來配置端口將數據位寬設置為16bit,收發器發送通道內部的數據位寬為20bit。可以由線速率計算出發送時鐘TXUSRCLK = 5Gbps/20bit = 250MHz。因為用戶數據位寬為16bit,是2byte mode,因此TXUSRCLK2 的頻率也為250MHz

3.2 8B/10B編碼器

8B/10B編碼器也是我認位在TX 通道中比較重要的一個模塊。因為在該模塊下,有一個比較重要的概念叫做

K Characters(K 字符),由于這些字符的添加,使得在數據傳輸的過程中,進行數據對齊提供了便利。

??在8B/10B編碼器當中,還需要注意的是字節排序的順序。當然如果使能了8B/10B編碼,那么這個順序就不用太關系,但是沒有使用8B/10B編碼也就是使用了8B/10B bypass這個模式,需要注意填充的字符1bit 的TXCHARDISPMODE和 1bit 的TXCHARDISPVAL在一個10bit數據中的位置。

?? 對于K 字符,在發送通道中是使用TXCHARISK[3:0]這個信號來指示的,通過拉高對應的bit位,來表示內部數據的哪一bit是K字符,不拉高的就是用戶數據。

3.3 TX其他模塊

??TX的其他模塊,離用戶邏輯較遠,我在實驗的時候沒有太關心。簡單來說:

| 模塊 | 作用 |

|---|---|

| Gearbox |

傳輸速率控制,GTP支持不同類型的編碼 (8B/10B, 64B/66B, 64B/67B) 使用這些編碼的時候,由于在用戶數據中插入數據后,數據需要在多個周期才能完整地傳輸。 因此需要速率控制來達到調節地作用 |

| TxBuffer | 根據字面意思,就是一個Buffer,用于進行時鐘域轉換的,保證數據和時鐘的對齊關系 |

| TxbufferBypass | 不經過buffer也能使數據和時鐘對齊,通過直接對時鐘進行相位校正的方式 |

| TX Pattern Generator | 產生偽隨機數,來對收發器進行測試驗證時使用 |

| TX Polarity Control | 收發對的極性控制,感覺就是方便PCB布線,極性反了還可以補救 |

| TX Fabric Clock Output Control | 收發器TX內部也能產生時鐘,前面介紹的TXOUCLK就是在收發器內部產生的 |

剩下的還有PCIE和SATA使用的一些資源,可以通過使用這些端口來完成PCIE和SATA協議的實現。

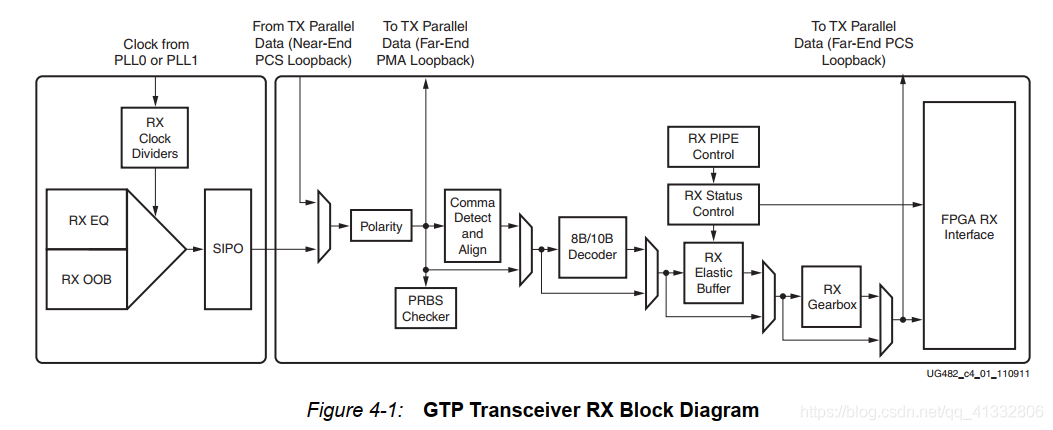

4 接收器RX

RX 與 TX就像是一個逆過程,RX實現的功能與TX基本相反,也就是RX完成數據接收,負責串行轉并行并對串行數據進行解碼,得到用戶數據。我也只介紹其中我覺得比較重要的模塊。

4.1 CDR模塊

高速串行接口在傳輸數據時,高速數據中包含了時鐘信息,因此可以通過一定的方式,將時鐘信息從串行數據中恢復出來。CDR模塊所完成的功能就是恢復出串行時鐘。在最終的用戶接收模塊中,可以看到接收模塊用戶側時鐘來源可以是TX模塊,也可以是由CDR模塊恢復出來的時鐘。

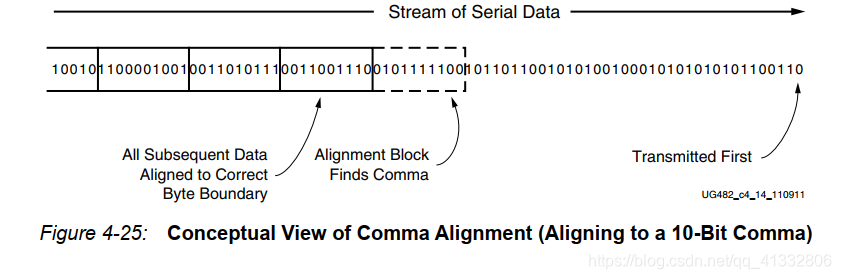

4.2 字節對齊模塊

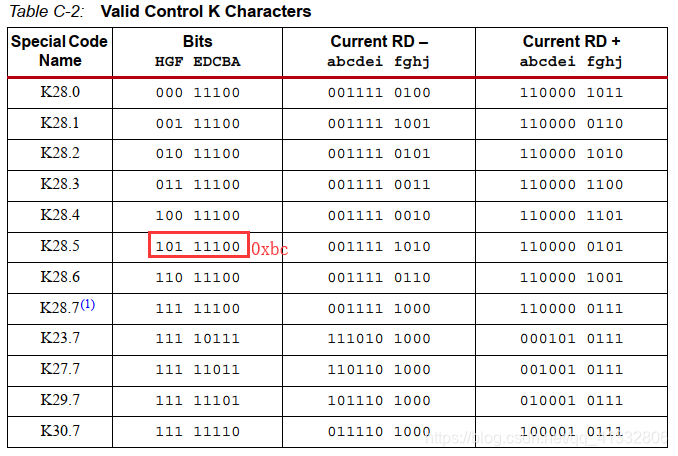

串行數據必須經過對齊后才能轉換成并行數據給用戶使用。為了能夠識別這些編解,就需要使用到前面在TX模塊中介紹到的K Characters(K 字符),這些字符也被叫做comma。接收器在輸入數據中搜索comma。當找到comma時,它將comma移至字節邊界,以便接收到的并行字與發送的并行字匹配。

??只有接收到了comma后,數據才會被對齊,然后就可以按照10bit,10bit來排列數據,供解碼模塊使用,最終得到用戶數據。

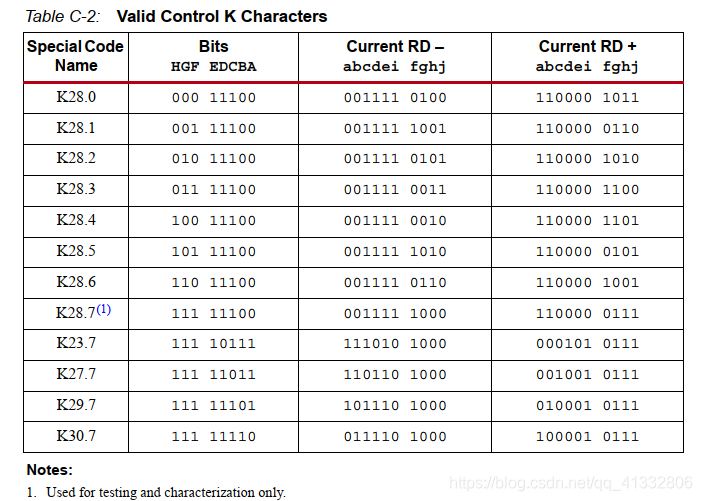

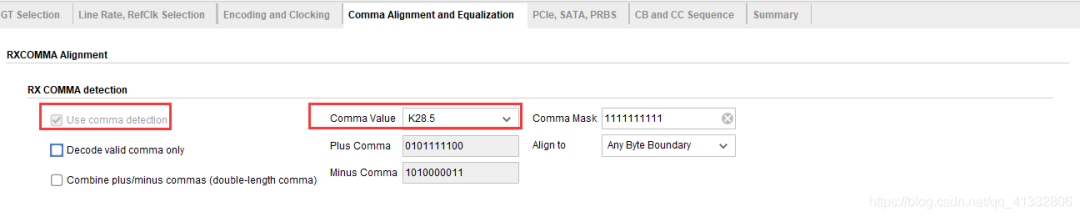

??在字節對齊模塊,常用的用于對齊的字符有K28.3,K28.5。在UG482的附錄里面也給出了K字符表。在設置IP的時候,就可以選擇comma來確定用于對齊的comma。

??其他模塊基本就是TX模塊的逆過程。

4 官方demo驗證

4.1 示例IP配置

接下來就使用官方的demo來驗證以下 收發器向導IP的功能。

首先配置出一個IP:

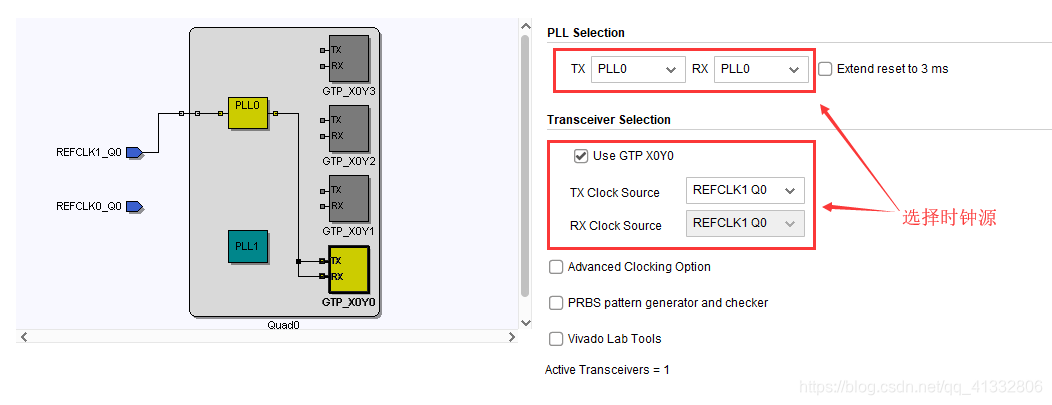

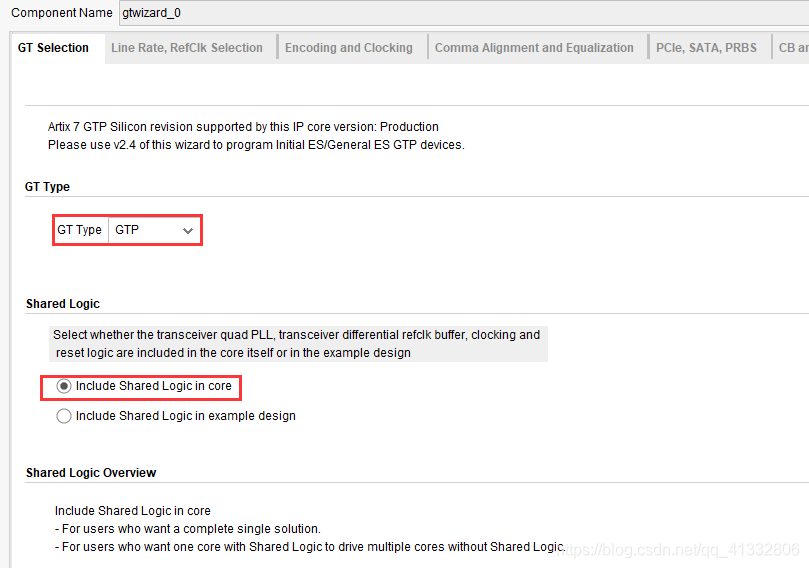

GT Selection

選擇收發器類型,選擇GTP,包含共享邏輯到IP中,這樣用戶就不用去考慮收發器的復位初始化和參數配置這些事情了。

LineRate Refclk選擇

編解碼和用戶時鐘

其他選項默認即可。

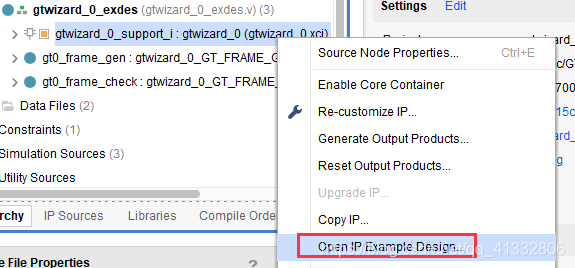

4.2 打開示例工程

點擊open IP example design就可以打開示例工程。

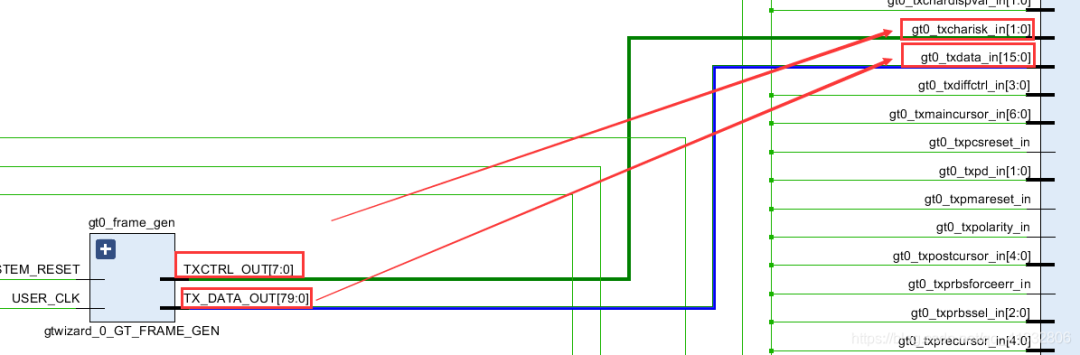

4.2.1 發送模塊

可以看到示例工程比較簡單,一個產生數據的模塊用于從ROM中讀出數據,ROM中的數據是包含碼字的遞增數。

其實這個示例工程中的ROM的數據一開始難以理解,弄個80bit位寬的的rom,最后實際上有用的只有16bit數據加上2bit的comma指示信號。

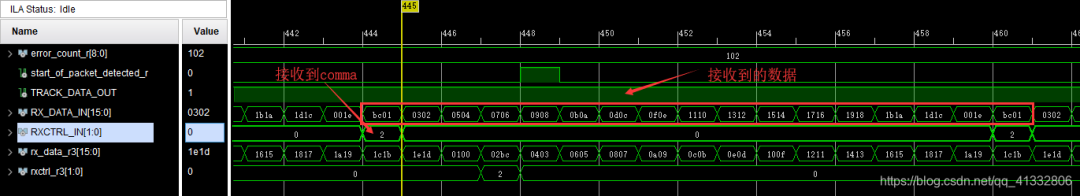

4.2.2 接收校驗模塊

接收校驗模塊主要是實現,對數據的接收和進行校驗,在該模塊中需要去檢測comma,通過comma來完成數據的對齊。

4.2.3 下載驗證

對示例工程進行簡單的更改后,綜合,然后下載到FPGA當中,通過ila來觀察得到的結果。由于手上沒有光纖,因此使用兩個板子來進行驗證,一個板子發給另一個板子。

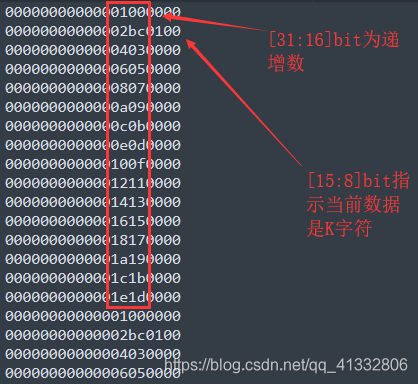

發送模塊

?可以看到,在發送模塊,進行數據的發送,其中發送的數據是00~1e的遞增數據,需要注意的是第二個數據0x02bc,其中0xbc是一個K28.5 comma

4.2.4 接收模塊

接收模塊中負責接收數據,接收到0xbc的時候,說明檢測到K28.5,之后就要進行數據的對齊。

可以看到使用K28.5 能夠實現數據收發的對齊,那么在自己實現一個小協議的時候,就可以根據使用K28.5來進行突發的數據傳輸。

原文鏈接:

https://tencentcloud.csdn.net/678a26e4edd0904849a68949.html

-

收發器

+關注

關注

10文章

3673瀏覽量

108001 -

高速接口

+關注

關注

1文章

58瀏覽量

14995

原文標題:高速接口----7系列收發器GTP

文章出處:【微信號:gh_9d70b445f494,微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

谷泰微GT74LVCXTX45系列雙電源總線收發器產品介紹

高速接口7系列收發器GTP介紹

高速接口7系列收發器GTP介紹

評論