前言

想用FPGA去控制一個(gè)器件,首先要學(xué)會(huì)閱讀器件的數(shù)據(jù)手冊(cè),去了解器件的功能和使用方法。下面就來(lái)梳理一下IS42R16320D的數(shù)據(jù)手冊(cè)里面本案例會(huì)用到的部分。

IS42R16320D時(shí)鐘支持最高200M,也就是其讀寫(xiě)速度不能超過(guò)200M,案例里面我們選擇100M時(shí)鐘進(jìn)行讀寫(xiě)操作。

IS42R16320D在時(shí)鐘上升沿進(jìn)行數(shù)據(jù)捕獲。

SDRAM容量

DE2-115配備2片IS42S16320器件

2片* 210列* 213行* 4 bank * 16bit=2 * 32M * 16bit=2 * 64MB=128MB

DE10-Standard配備1片IS42S16320器件

210列 * 213行 * 4 bank * 16bit=32M * 16bit=64MB

DE1-SOC配備1片IS42S16320器件

210列 * 213行*4 bank * 16bit=32M * 16bit=64MB

注:16bit代表每個(gè)存儲(chǔ)單元位寬是16bit。

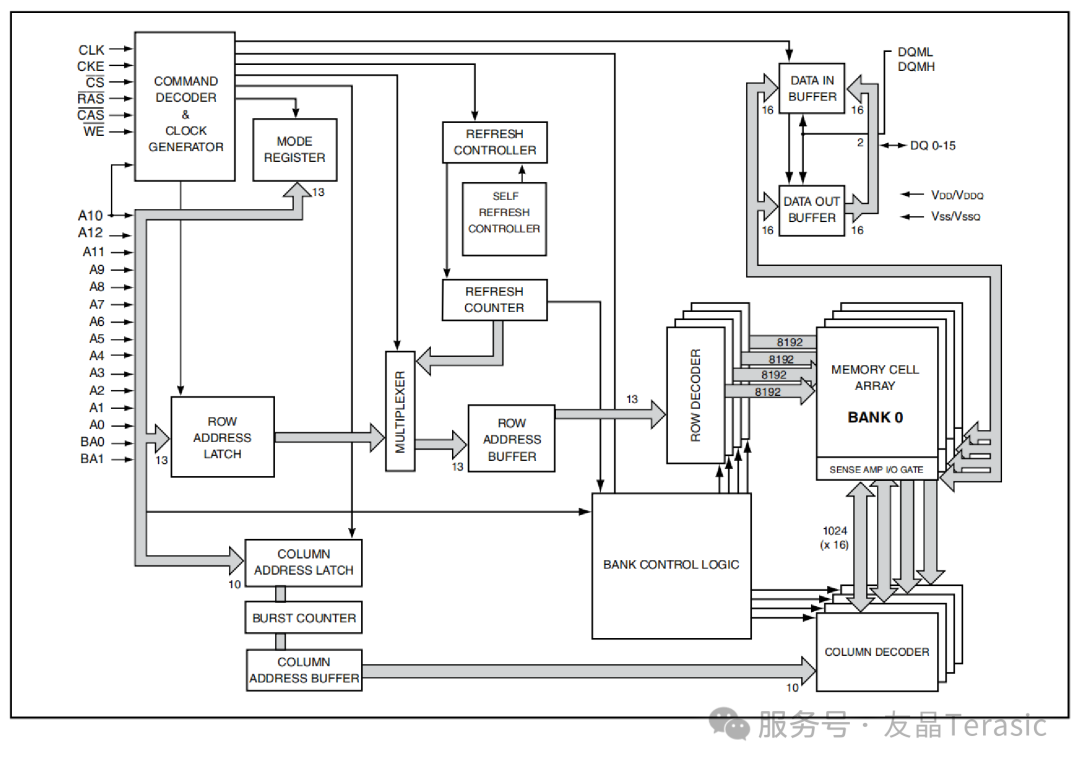

IS42R16320D功能框圖

IS42R16320D的引腳功能描述:

備注:

RASCASWE組合起來(lái)作為命令控制SDRAM的具體操作。

DQML和DQMH是數(shù)據(jù)輸入輸出掩碼,IS42R16320D數(shù)據(jù)輸入輸出一次是16bit,有的時(shí)候只需要取高字節(jié)8位或者低字節(jié)8位的時(shí)候,就可以通過(guò)這兩個(gè)信號(hào)線來(lái)控制哪個(gè)字節(jié)有效。注意DQM在寫(xiě)操作時(shí)是立即生效,DQM在讀操作時(shí)是2個(gè)時(shí)鐘周期后生效。

SDRAM的命令控制

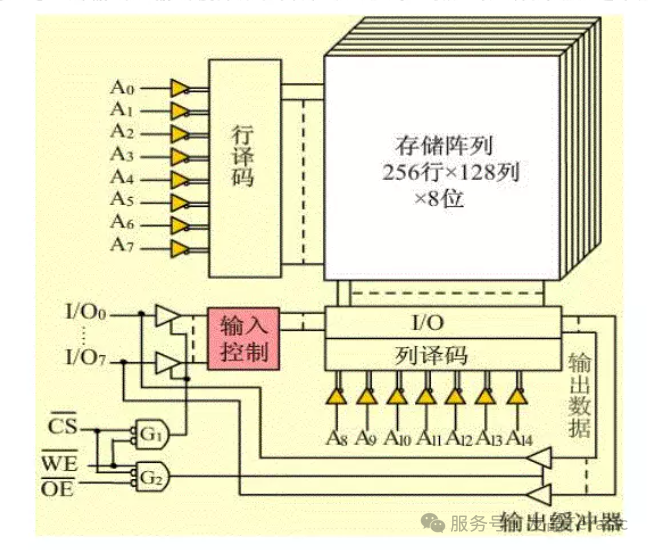

在了解IS42R16320D命令控制之前可以先參考普通SRAM讀寫(xiě)控制原理:

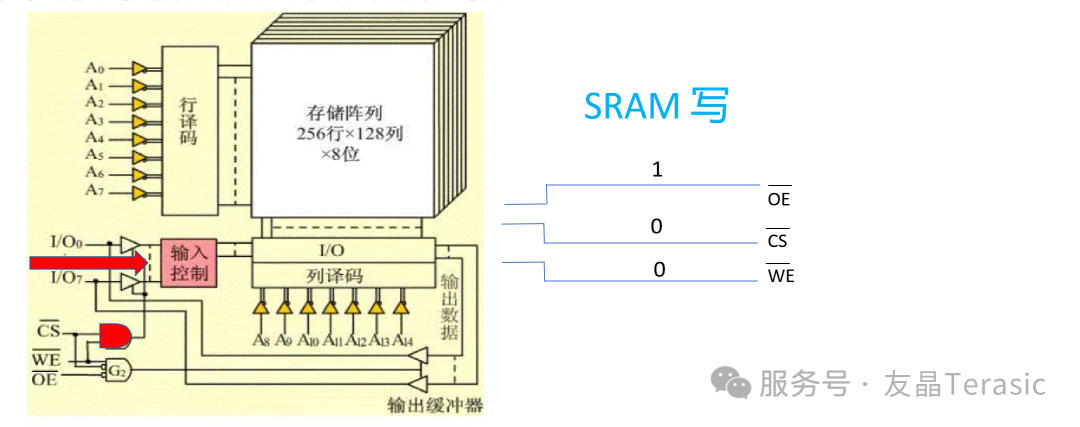

下圖為32KByte容量的SRAM結(jié)構(gòu)示意圖,該SRAM有8位行地址,譯碼后生成 256根(2的8次方)行地址線,列地址線為7位,譯碼后生成128根(2的7次方)列地址線。

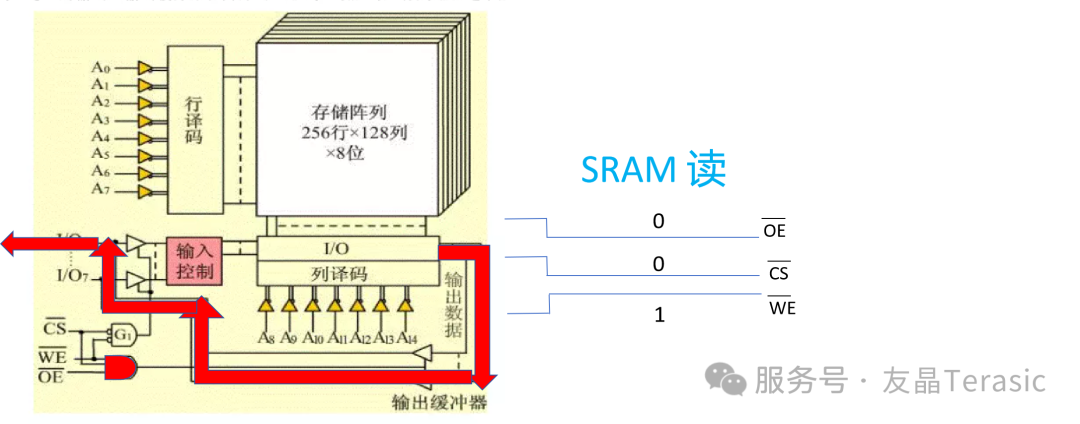

對(duì)SRAM進(jìn)行讀操作時(shí),0E#和CS#為低電平,WE#為高電平,G1輸出低電平將輸入控緩沖器關(guān)閉,G2輸出高電平將輸出緩沖器打開(kāi),通過(guò)行列地址線選中的存儲(chǔ)單元數(shù)據(jù)經(jīng)I/0和輸出緩沖器,最后從I/0[0:7]輸出,如下圖:

對(duì)SRAM進(jìn)行寫(xiě)操作時(shí),WE#和CS#為低電平,0E#為高電平,G1輸出高電平將輸入緩沖器打開(kāi),G2輸出低電平將輸出緩沖器關(guān)閉,I/0[0:7]上的輸出經(jīng)輸出緩沖器和內(nèi)部I/0總線,最后寫(xiě)入行列地址選中的存儲(chǔ)空間中。

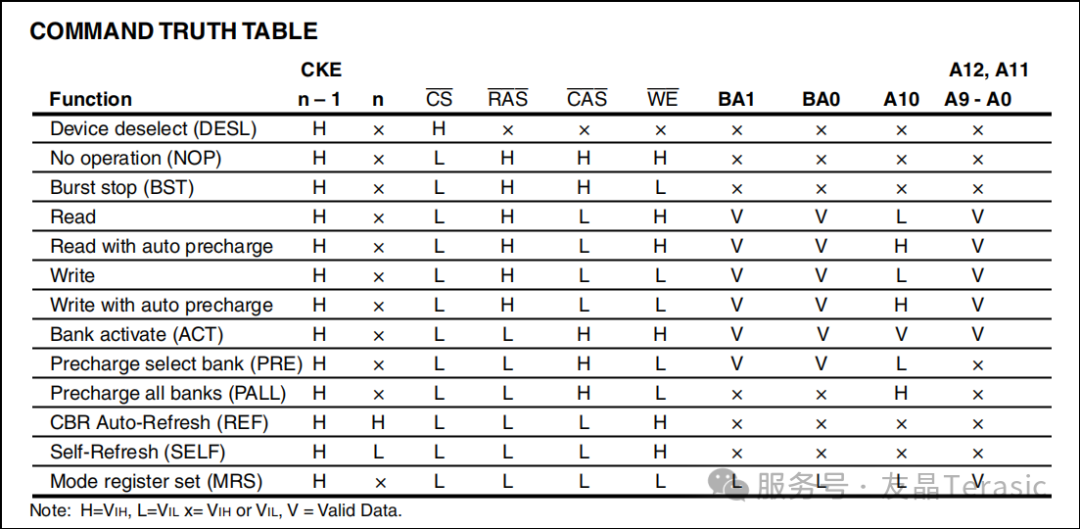

SDRAM的讀寫(xiě)控制跟SRAM讀寫(xiě)控制類(lèi)似,但是因?yàn)镾DRAM行列地址復(fù)用,支持突發(fā)讀寫(xiě)等等,SDRAM的讀寫(xiě)控制會(huì)更復(fù)雜一些,它主要由RASCASWE等信號(hào)組合起來(lái)作為命令控制SDRAM完成各項(xiàng)操作。

控制SDRAM的常用命令有:

以上表格參考IS42R16320D數(shù)據(jù)手冊(cè)第9頁(yè):

下面結(jié)合IS42R16320D數(shù)據(jù)手冊(cè)給出的命令發(fā)送時(shí)序圖詳細(xì)介紹SDRAM 的各項(xiàng)常見(jiàn)操作。

上電后SDRAM器件要先初始化之后才能正常工作。不同型號(hào)的SDRAM器件其初始化要求可能不同,詳細(xì)要看對(duì)應(yīng)的 datasheet。

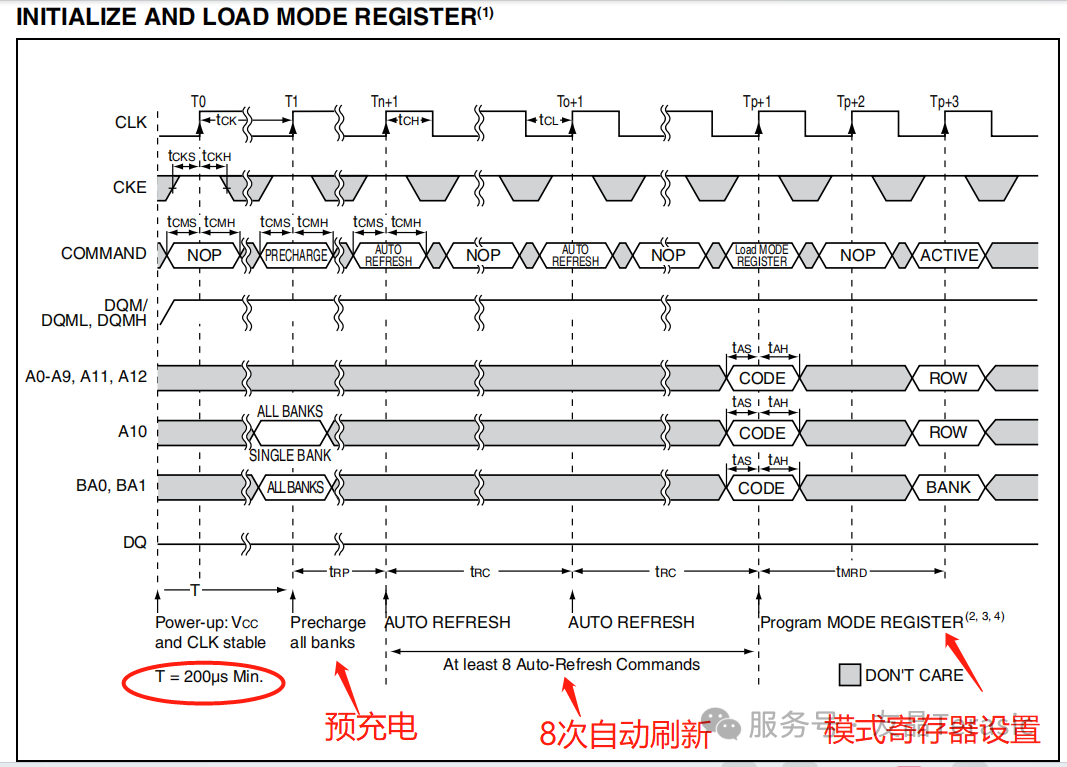

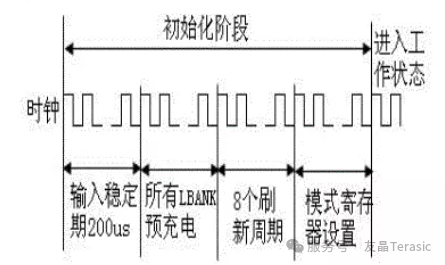

IS42R16320D的初始化過(guò)程是至少等待200us(用于等待power和時(shí)鐘穩(wěn)定),然后進(jìn)行1次預(yù)充電(對(duì)所有bank)和8次自動(dòng)刷新操作,然后設(shè)置模式寄存器。其時(shí)序圖如下:

其中預(yù)充電命令發(fā)送以后要經(jīng)過(guò)tRP時(shí)間才能完成預(yù)充電操作,自動(dòng)刷新命令發(fā)送以后要經(jīng)過(guò)tRC時(shí)間才能完成自動(dòng)刷新操作,模式寄存器設(shè)置命令發(fā)送以后要經(jīng)過(guò)tMRD時(shí)間才能完成寄存器設(shè)定。以上命令發(fā)送后的等待時(shí)間以及最初的200us延遲時(shí)間內(nèi),只有NOP命令有效。

其實(shí)把這個(gè)時(shí)序簡(jiǎn)化一下就是這樣:

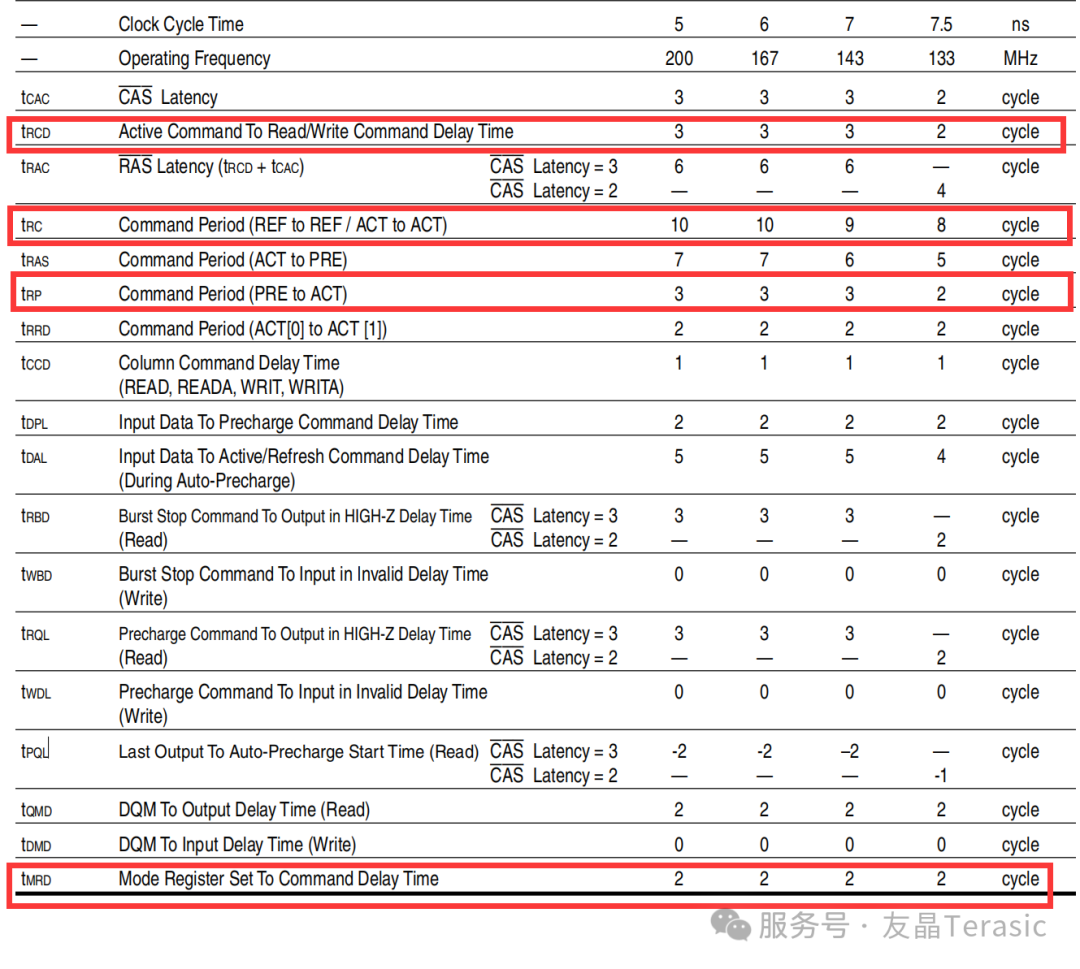

IS42R16320D數(shù)據(jù)手冊(cè)第19頁(yè)可以看到,tRP時(shí)間是2-3個(gè)時(shí)鐘周期,頻率高一點(diǎn)(200MHz)至少要3個(gè)周期,頻率低一點(diǎn)(133MHz)至少要2個(gè)周期,為了保險(xiǎn),在寫(xiě)Verilog代碼的時(shí)候時(shí)間可以設(shè)定比這個(gè)長(zhǎng)一點(diǎn)。比如本案例跑100M,一個(gè)時(shí)鐘周期是10ns,那么預(yù)充電等待時(shí)間可以設(shè)定為2個(gè)時(shí)鐘周期以上。

根據(jù)如下IS42R16320D數(shù)據(jù)手冊(cè)截圖可知tRP時(shí)間是2-3個(gè)時(shí)鐘周期,本案例代碼里面設(shè)定等待20個(gè)時(shí)鐘周期;

tRC時(shí)間是8-10個(gè)時(shí)鐘周期,本案例代碼里面設(shè)定等待20個(gè)時(shí)鐘周期;

tMRD時(shí)間是2個(gè)時(shí)鐘周期,本案例代碼里面設(shè)定等待20個(gè)時(shí)鐘周期;

tRCD時(shí)間是2-3個(gè)時(shí)鐘周期,本案例代碼里面設(shè)定等待3個(gè)時(shí)鐘周期。

1. 預(yù)充電

由于 SDRAM 的尋址具有獨(dú)占性,所以在進(jìn)行完讀寫(xiě)操作后,如果要對(duì)同一 L-Bank 的另一行進(jìn)行尋址,就要將原來(lái)有效(工作)的行關(guān)閉重新發(fā)送行/列地址。L-Bank 關(guān)閉現(xiàn)有工作行,準(zhǔn)備打開(kāi)新行的操作就是預(yù)充電(Precharge)。

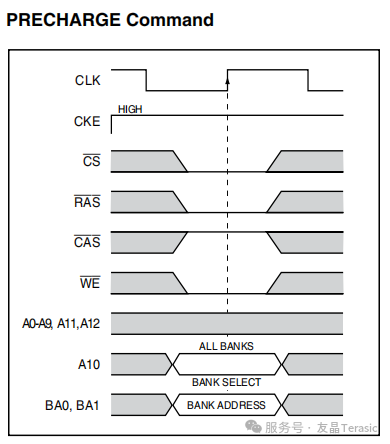

預(yù)充電時(shí)可以是對(duì)指定bank操作,也可以是對(duì)所有bank操作。通過(guò)地址線A10和BANK線BA0、BA1來(lái)決定。如果是對(duì)指定BANK操作時(shí),A10設(shè)置為0,并由BA0、BA1指定某一BANK。如果是對(duì)所有BANK操作,A10設(shè)置為1即可。

SDRAM在初始化階段要進(jìn)行一次預(yù)充電操作。這個(gè)操作是對(duì)所有BANK進(jìn)行的操作。

預(yù)充電要等待tRP時(shí)間。

預(yù)充電命令CSRASCAS組合是010。

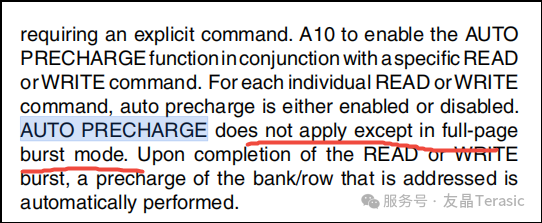

自動(dòng)預(yù)充電

可設(shè)置讓芯片每次讀寫(xiě)操作后,自動(dòng)進(jìn)行預(yù)充電(在發(fā)送讀寫(xiě)命令時(shí)通過(guò)A10信號(hào)線設(shè)置)。這樣設(shè)計(jì)時(shí)無(wú)需要關(guān)心,只需要等待幾個(gè)時(shí)間周期即可。

注意,突發(fā)模式下,當(dāng)突發(fā)長(zhǎng)度為全頁(yè)時(shí)不支持自動(dòng)預(yù)充電命令。

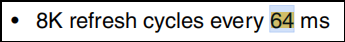

2.自動(dòng)刷新

由于cell的電容很小,并且CMOS晶體管在關(guān)閉的時(shí)候,也存在漏電,這樣電容上的電荷也在隨著時(shí)間的變化,逐漸變少。時(shí)間一長(zhǎng),存儲(chǔ)的信息就會(huì)丟失。為了解決這一問(wèn)題,具體做法是對(duì)于每個(gè)單元行,每過(guò)一段時(shí)間就進(jìn)行讀取,等放大器暫存好信息后就立刻將其寫(xiě)回行。IS42R16320D數(shù)據(jù)手冊(cè)第一頁(yè)提到每64ms內(nèi)就要對(duì)cell陣列進(jìn)行一次全面刷新。

自動(dòng)刷新要等待tRC時(shí)間。

自動(dòng)刷新命令RASCASWE組合是001。

自動(dòng)刷新期間不能做其他操作。

區(qū)別于自刷新(SELF REFRESH),這個(gè)是在SDRAM休眠下為確保數(shù)據(jù)不丟失的自動(dòng)操作。在發(fā)出自動(dòng)刷新命令時(shí),將CKE置于無(wú)效狀態(tài),就進(jìn)入了自刷新模式,此時(shí)不再依靠系統(tǒng)時(shí)鐘工作,而是根據(jù)內(nèi)部的時(shí)鐘進(jìn)行刷新操作。在自刷新期間除了CKE之外,所有外部信號(hào)也都是無(wú)效的(無(wú)需外部提供刷新指令),只有重新使CKE有效才能退出自刷新模式并進(jìn)入正常工作狀態(tài)。

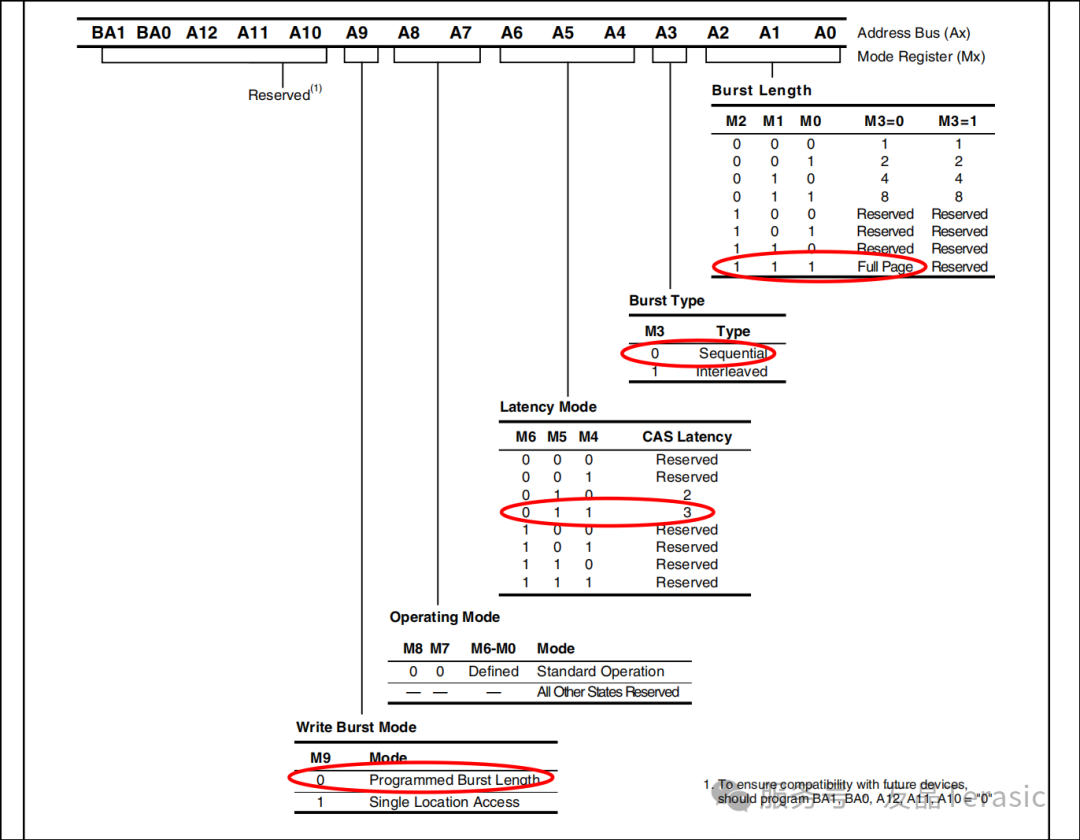

3. 模式寄存器設(shè)置

SDRAM芯片內(nèi)部有一個(gè)邏輯控制單元,這個(gè)控制單元的相關(guān)控制參數(shù)是由MR(Mode Regisister模式寄存器)提供,SDRAM芯片每次進(jìn)行初始化時(shí)都要將重新寫(xiě)MR。MR 中設(shè)置了 SDRAM 的運(yùn)行模式:包括突發(fā)長(zhǎng)度(BL)、突發(fā)類(lèi)型(Burst Type)、CAS 延遲(CAS Latency)、運(yùn)行方式(Operating Mode)和寫(xiě)入突發(fā)模式。

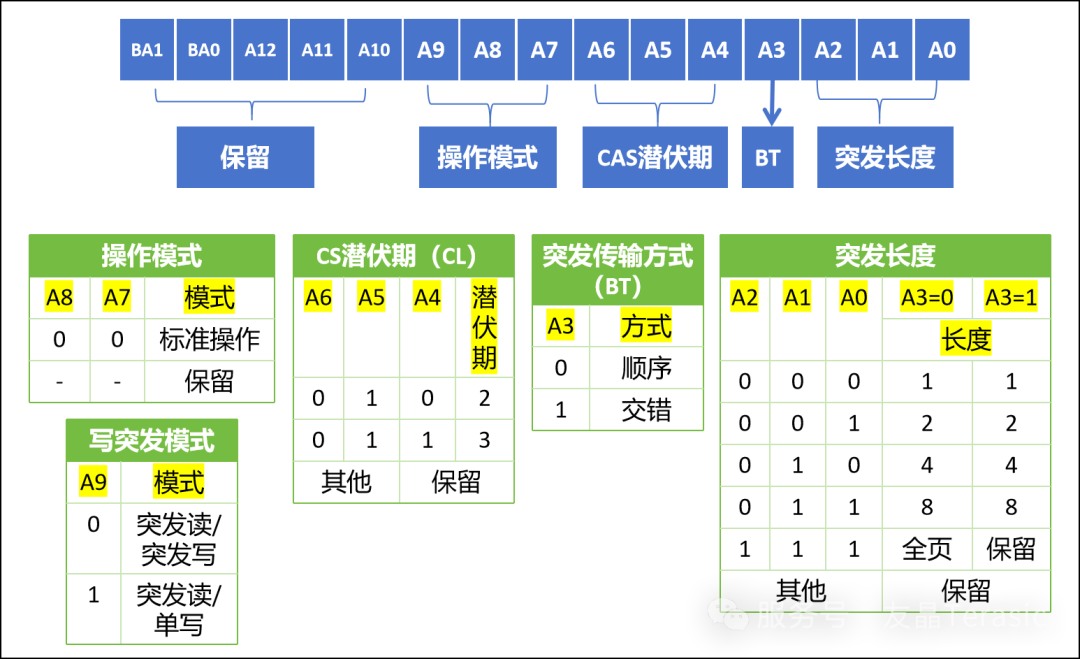

將上面表格翻譯下如下:

突發(fā) burst長(zhǎng)度

突發(fā)(Burst)是指在同一行中相鄰的存儲(chǔ)單元連續(xù)進(jìn)行數(shù)據(jù)傳輸?shù)姆绞健V恍枰谛屑せ詈螅o出一次讀寫(xiě)命令和列起始地址以及突發(fā)長(zhǎng)度,就開(kāi)始讀/寫(xiě)一定長(zhǎng)度數(shù)據(jù),列地址自動(dòng)遞增。

連續(xù)傳輸所涉及到存儲(chǔ)單元(列)的數(shù)量就是突發(fā)長(zhǎng)度(BurstLengths,簡(jiǎn)稱(chēng) BL)。常見(jiàn)的突發(fā)長(zhǎng)度是 1、2、4、8和全頁(yè)(全頁(yè)指的是一整行,比如IS42R16320D一個(gè)bank的一行是1024個(gè)存儲(chǔ)單元,那么全頁(yè)就是1024個(gè))。

突發(fā)讀寫(xiě)完或者提前結(jié)束突發(fā)讀寫(xiě)時(shí),需要發(fā)送突發(fā)停止命令(BURST TERMINATE),或者發(fā)送預(yù)充電命令(PRECHARGE)。

本案例設(shè)置突發(fā)長(zhǎng)度是全頁(yè),A0A1A2設(shè)定為111。

突發(fā)類(lèi)型

突發(fā)類(lèi)型也叫突發(fā)傳輸方式,IS42R16320D突發(fā)類(lèi)型支持順序傳輸和交錯(cuò)傳輸。順序傳輸就是連續(xù)地、依次地讀后面的幾個(gè)存儲(chǔ)單元,交錯(cuò)傳輸就是隔一個(gè)讀一個(gè)。

本案例設(shè)置為順序傳輸(只有順序傳輸支持全頁(yè)的突發(fā)長(zhǎng)度),A3設(shè)置為0。

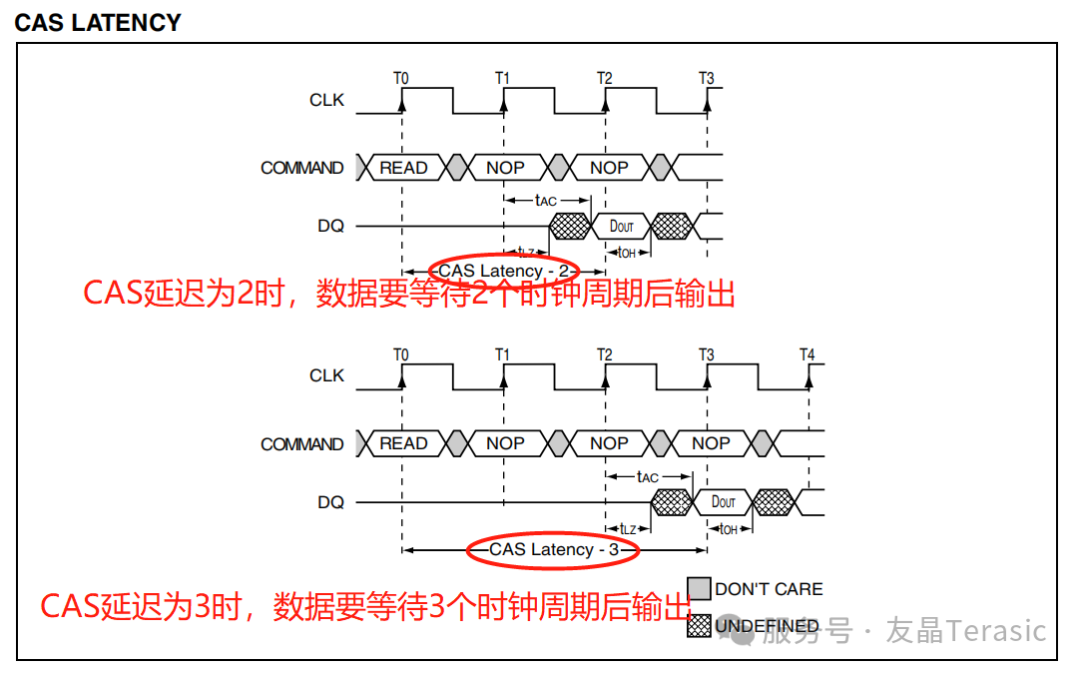

CAS潛伏期

在讀命令發(fā)送了列地址后,數(shù)據(jù)并不是馬上到達(dá)數(shù)據(jù)總線,而是要經(jīng)過(guò)一段潛伏期,一般為2到3個(gè)時(shí)鐘周期,注意潛伏期不是延遲,潛伏期是發(fā)送列地址后數(shù)據(jù)已經(jīng)有效,只是還沒(méi)有達(dá)到一定的高度,或者說(shuō)是信號(hào)不夠強(qiáng),要經(jīng)過(guò)一定的放大才能輸出,所以說(shuō)潛伏期不是延遲。

只有讀操作時(shí)存在CAS潛伏期。

本案例設(shè)置CAS為3,A6A5A4設(shè)置為011。

突發(fā)操作模式

操作模式可以分為突發(fā)讀/突發(fā)寫(xiě),或者是突發(fā)讀/單一寫(xiě)等。

突發(fā)讀就是在讀命令發(fā)送了起始列地址,在讀取第一個(gè)數(shù)據(jù)之后,如果想讀取這個(gè)存儲(chǔ)單元后面的存儲(chǔ)單元的數(shù)據(jù)的話,就不必再次發(fā)送行列地址了,他會(huì)自動(dòng)的讀取接下來(lái)的數(shù)據(jù),至于讀幾個(gè)存儲(chǔ)單元,就涉及到突發(fā)長(zhǎng)度,比如若設(shè)置的是全頁(yè)的方式,就是將這一行上的數(shù)據(jù)一連串的全部讀出或?qū)懭搿?/p>

本案例設(shè)置為突發(fā)讀和突發(fā)寫(xiě),A9設(shè)置為0。

設(shè)置模式寄存器操作要等待tMRD時(shí)間,一般是2個(gè)時(shí)鐘周期。

模式寄存器設(shè)置的命令RASCASWE組合是000。

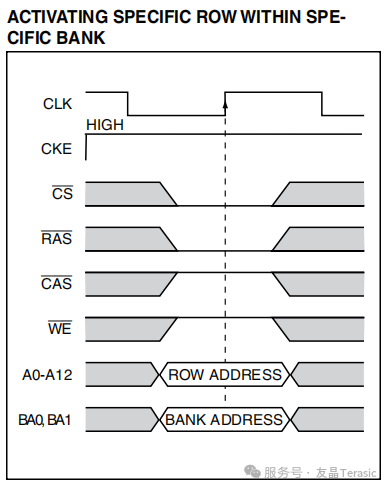

4. 激活

初始化完成后,要想對(duì)某個(gè)bank進(jìn)行讀寫(xiě)操作之前,先要對(duì)這個(gè)bank中的陣列進(jìn)行尋址,首先要確定行(Row),使之處于活動(dòng)狀態(tài)(Active),然后再確定列。雖然之前要進(jìn)行片選和L-Bank 的地址,但它們與行有效可以同時(shí)進(jìn)行。

激活操作要等待tRCD時(shí)間,一般是2-3個(gè)時(shí)鐘周期,本案例設(shè)置為3個(gè)時(shí)鐘周期(SC_RCD=3)。

激活命令RASCASWE組合是011。

5. 讀寫(xiě)操作

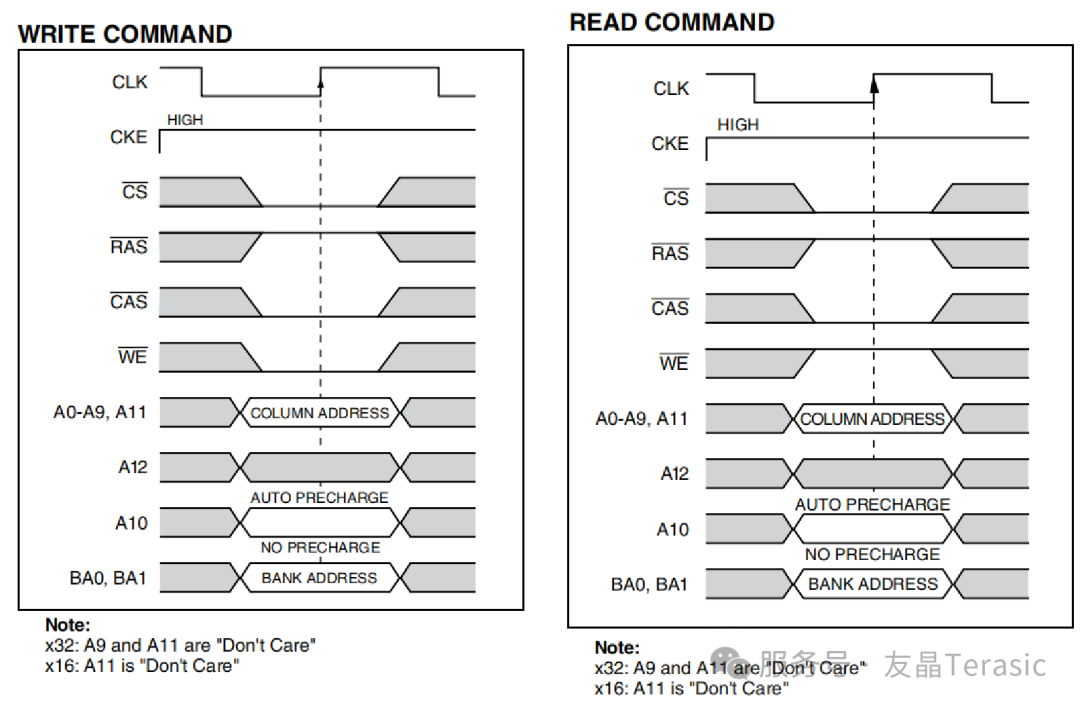

行地址確定之后,就要對(duì)列地址進(jìn)行尋址了。在SDRAM中,行地址與列地址線是共用的,列地址線是 A0-A10。讀/寫(xiě)命令是通過(guò)WE#信號(hào)的狀態(tài)去區(qū)分的,當(dāng)WE#為低電平有效時(shí)是寫(xiě)命令,為高電平無(wú)效時(shí)是讀命令。列尋址信號(hào)與讀寫(xiě)命令是同時(shí)發(fā)出的。雖然列地址線與行尋址共用,當(dāng)CAS為有效電平時(shí),地址線輸入的地址作為列地址;(當(dāng)RAS有效時(shí),地址線輸入的地址作為行地址)。列讀寫(xiě)時(shí)序如圖所示。

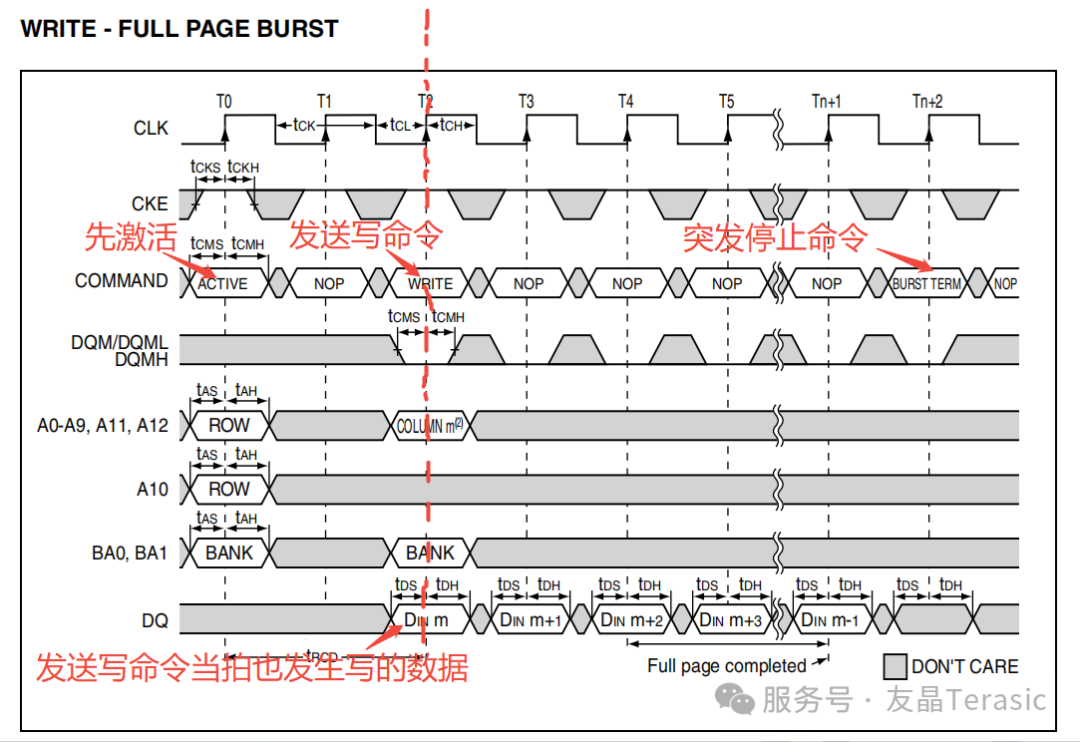

本案例設(shè)置的是突發(fā)讀寫(xiě), 突發(fā)寫(xiě)的時(shí)序圖如下:

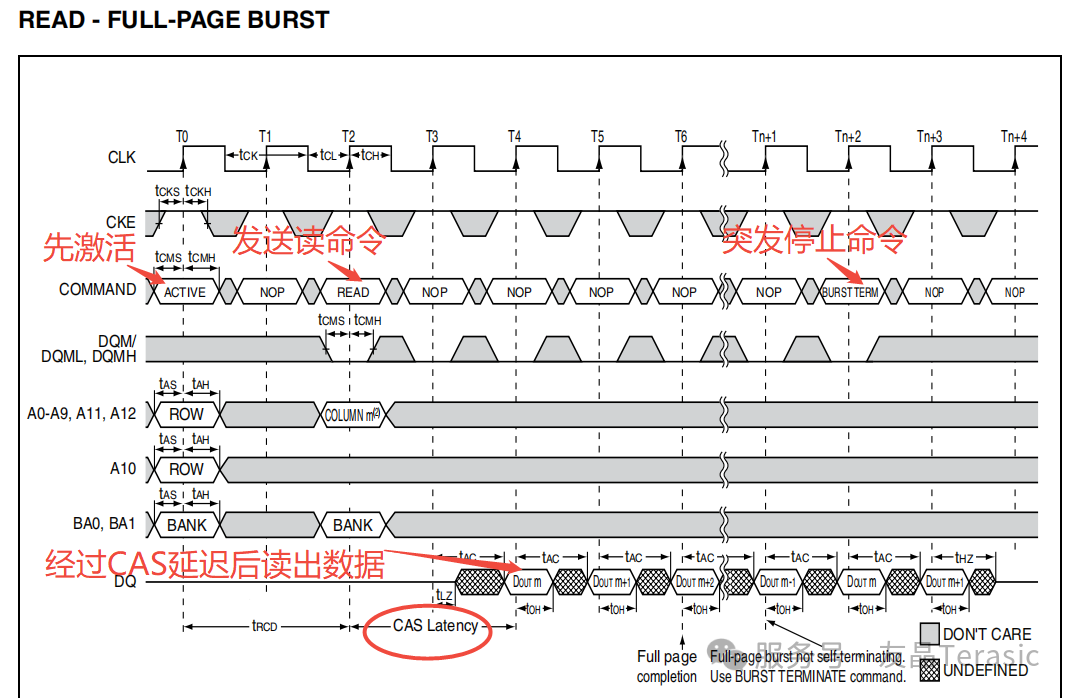

突發(fā)讀的時(shí)序圖如下:

-

控制器

+關(guān)注

關(guān)注

114文章

17026瀏覽量

183305 -

SDRAM

+關(guān)注

關(guān)注

7文章

441瀏覽量

56117 -

時(shí)鐘

+關(guān)注

關(guān)注

11文章

1887瀏覽量

132957

原文標(biāo)題:03-SDRAM控制器的設(shè)計(jì)——解讀IS42R16320D的數(shù)據(jù)手冊(cè)

文章出處:【微信號(hào):友晶FPGA,微信公眾號(hào):友晶FPGA】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

夏華機(jī)密資料 PS-42D8等離子維修手冊(cè)(故障分析篇)

IS25WP016D-JULE-TR進(jìn)口原裝正品假一賠十

iMXRT1172處理器是否支持ISSI制造的SDRAM IS42S16320F-6BLI?

CAT-R131-D1D CAT-R131-D1D D-Sub 后殼和夾具

CAT-R131-D743 CAT-R131-D743 D-Sub 后殼和夾具

CAT-R131-D1B CAT-R131-D1B D-Sub 后殼和夾具

MAX6384XS42D2+T PMIC - 監(jiān)控器

MAX6384XS42D2+ - (Maxim Integrated) - PMIC - 電源管理 - 專(zhuān)用型

解讀IS42R16320D的數(shù)據(jù)手冊(cè)

解讀IS42R16320D的數(shù)據(jù)手冊(cè)

評(píng)論