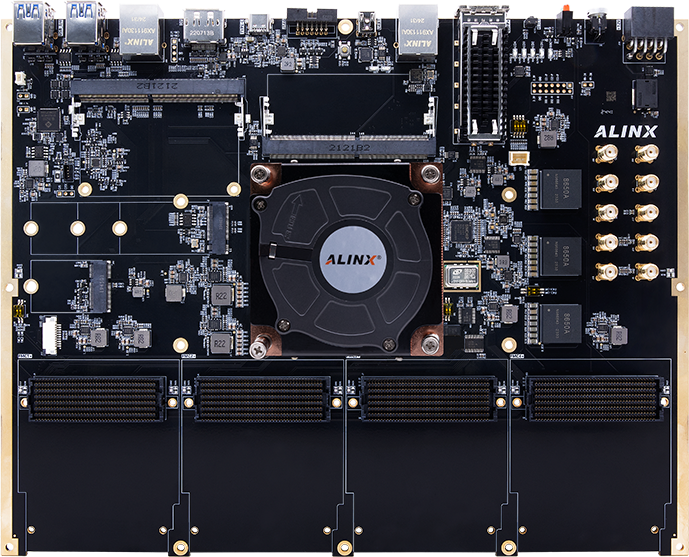

「AXVU13F」Virtex UltraScale+ XCVU13P + Jetson Orin NX

繼發布 AMD Virtex UltraScale+ FPGA PCIE3.0 開發平臺 AXVU13P 后,ALINX 進一步研究尖端應用市場,面向 AI+ 場景進行優化設計,推出AXVU13F。

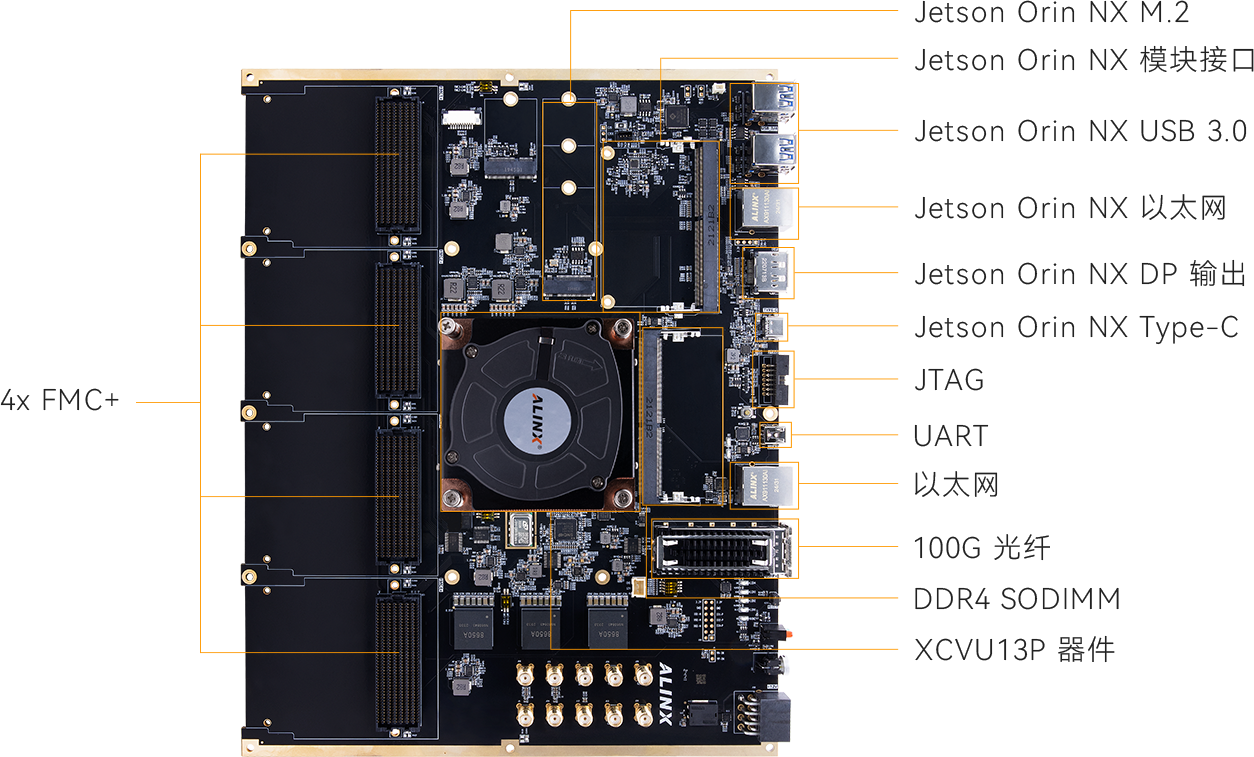

AXVU13F 和 AXVU13P 采用相同的 AMD Virtex UltraScale+ XCVU13P(16nm工藝)FPGA 芯片,但從原先最大支持 16G DDR4 SODIMM 內存條插槽升級為最大支持 32G,并且支持多達 4 個 FMC+ 擴展接口,接入了 100G 光纖接口,使其能夠勝任多傳感器同步或大規模數據采集。不僅如此,AXVU13F 結合了 Jetson Orin NXGPU 在 AI 推理任務方面的優勢,使其更適用于需要和人工智能結合的領域。

距離 2023 AI 元年剛剛過去 2 年,AI 發展速度之快、應用范圍之廣已超乎想象。可以預見,人工智能將逐步滲透進各行各業,從方方面面影響人們的生活。對廠商或企業來說,如何更具性價比地打造 AI+ 設備將成為提升生產力和效益的關鍵。

這正是 ALINX 設計 高端 FPGA + GPU 方案的價值所在。

試想一些典型的 AI 應用場景,比如工業質檢,既要毫秒級的機械臂控制,又需運行精密的視覺算法;又如智慧醫院,既要保護患者隱私在本地處理 CT 影像,又要保證 AI 診斷的準確性。單一芯片方案在這里捉襟見肘:GPU 擅長處理深度學習卻難以實現精準的實時控制,FPGA 能保證納秒級響應卻在 AI 模型部署上效率低下。

若使用特定 ASIC,也要承擔 AI 推理算法迭代速度過快的風險。一旦流片完成,將無法調整其計算邏輯。

企業在選擇 AI 推理硬件時,除了關注性能和功耗,還需要考慮整體擁有成本(TCO),包括開發成本、部署成本和維護成本。然而,傳統硬件架構在這方面存在明顯痛點:

ASIC 設計成本極高,開發周期長(通常需 12-24 個月),適用于大規模量產的消費級 AI 芯片,但對于中小型企業或特定行業應用,ROI 并不劃算。

GPU 受限于固定的指令集和數據流架構,在邊緣計算環境下通常無法發揮最高效能,導致計算資源利用率偏低,進一步增加了單位算力的成本。

當前 AI 推理市場急需一種能夠兼顧高性能、低功耗、靈活性和經濟性的計算架構,以解決現有 ASIC 和 GPU 的局限性,滿足實際應用需求。

ALINX 分別汲取 AMD 和英偉達之長,設計了基于 AMD Virtex Ultrascale+ FPGA(XCVU13P)和 NVIDIA Jetson Orin NX GPU 的超高端開發平臺 AXVU13F。

AMD Virtex Ultrascale+ VU13P

AMD Virtex Ultrascale+ 系列芯片是目前市場上最強大的 FPGA 之一,在 UltraScale 架構中具有最高收發器帶寬、最多 DSP 數量、最高內置和封裝內存可用性。Virtex Ultrascale+ 將全新存儲器、3D-on-3D 和多處理 SoC (MPSoC) 技術進行完美結合,能夠在高度并行計算的應用(如視頻處理、AI推理)中實現領先一代的價值。

Jetson Orin NX

Jetson Orin NX 集成了 NVIDIA 強大的 Ampere 架構 GPU,專為邊緣計算和 AI 推理任務設計,支持強大的深度學習模型推理能力,適用于圖像識別、物體檢測、自然語言處理等領域。8GB/16GB 的可選內存容量保證了處理較大規模神經網絡時的流暢運行。

平臺的設計不僅提供了強大的計算能力和靈活性,還通過豐富的外設擴展接口,使得開發者能夠根據不同應用需求進行高度定制化,進一步提高系統的整體性能。

FPGA 端

4 個 FMC+ 接口

1 路 QSFP28 100G 光纖接口

6 路 SMA 接口

1 路千兆以太網接口

1 路 UART 接口

6 路 IO 擴展接口等;

NVIDIA ORIN 端

1 路千兆以太網接口

4 個 USB3.0 接口

1 路 M.2 SSD 接口

1 路 M.2 WIFI/BT 接口等

高端 FPGA 和 GPU 的結合為開發者提供了一個極具靈活性的開發平臺,能夠應對不同類型的 AI 推理任務。以智能汽車與自動駕駛為例,FPGA 處理傳感器數據的預處理和初步分析,GPU 負責深度學習推理,執行復雜的路徑規劃和目標檢測,確保自動駕駛系統在實時性和安全性上的表現。

這種“FPGA 處理傳感器洪流+GPU 專注模型推理”的協同模式,也同樣適用于其他需要低延遲、高效的圖像識別和決策處理的場景,如工業檢測、視頻監控等。

ALINX 提供完整的用戶開發手冊和工具鏈與全備的技術支持,幫助您縮短從原型到量產的周期。

公司名稱:芯驛電子科技(上海)有限公司

官 網:www.alinx.com | www.aumo.cn

郵 箱:sales.online@alinx.com

服務熱線:021-67676997

技術支持:support@alinx.com

公司地址:上海市松江區新橋鎮漕松路 1 號 1 號樓 3 層

審核編輯 黃宇

-

FPGA

+關注

關注

1645文章

22050瀏覽量

618728 -

AI

+關注

關注

88文章

35168瀏覽量

280179

發布評論請先 登錄

【「零基礎開發AI Agent」閱讀體驗】+讀《零基礎開發AI Agent》掌握扣子平臺開發智能體方法

東軟醫療大模型覆蓋眾多應用場景

數采網關+工業物聯網平臺實現5G工廠應用場景全覆蓋

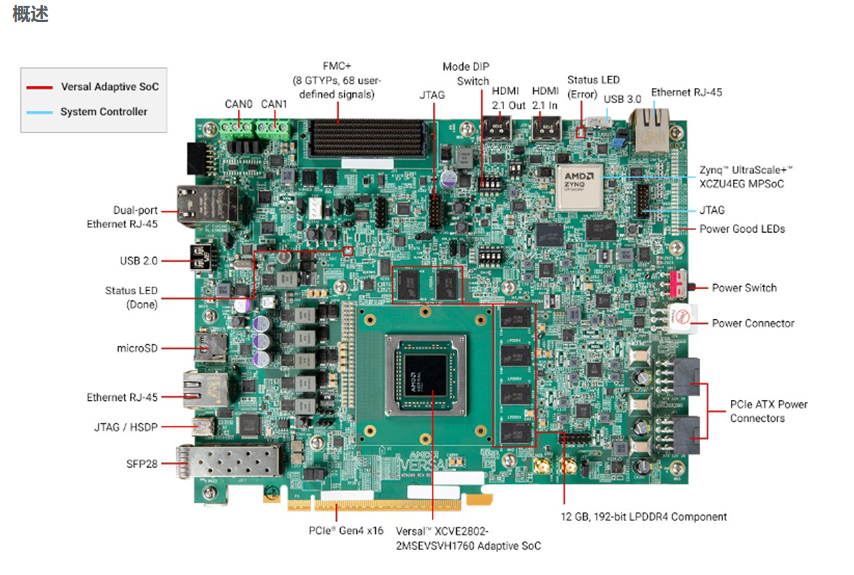

面向AI與機器學習應用的開發平臺 AMD/Xilinx Versal? AI Edge VEK280

《AI Agent 應用與項目實戰》----- 學習如何開發視頻應用

FPGA+AI王炸組合如何重塑未來世界:看看DeepSeek東方神秘力量如何預測......

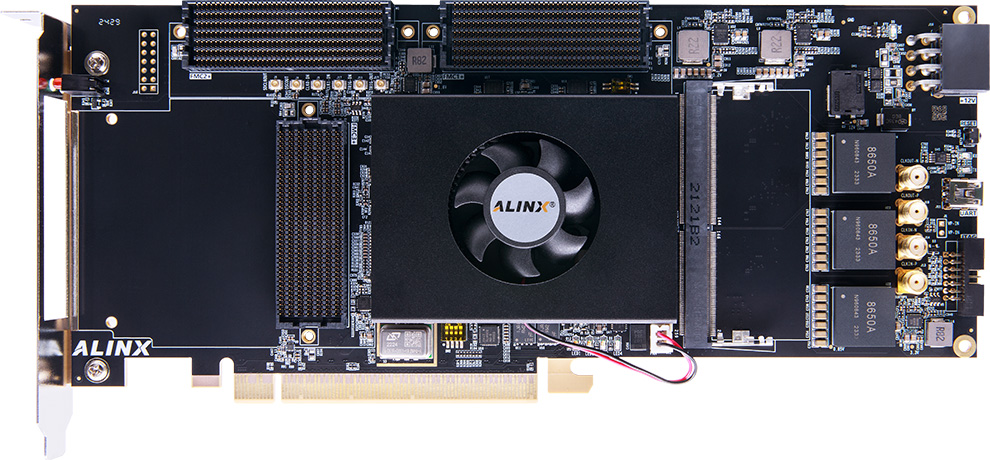

ALINX 發布 AXVU13P:AMD Virtex UltraScale+ 高端 FPGA PCle 3.0 綜合開發平臺

AI 應用場景全覆蓋!解碼超高端 VU+ FPGA 開發平臺 AXVU13F

AI 應用場景全覆蓋!解碼超高端 VU+ FPGA 開發平臺 AXVU13F

評論