本文介紹了集成電路設計中靜態(tài)時序分析(Static Timing Analysis,STA)的基本原理、概念和作用,并分析了其優(yōu)勢和局限性。

靜態(tài)時序分析(Static Timing Analysis,STA)是集成電路設計中的一項關鍵技術,它通過分析電路中的時序關系來驗證電路是否滿足設計的時序要求。與動態(tài)仿真不同,STA不需要模擬電路的實際運行過程,而是通過分析電路中的各個時鐘路徑、信號傳播延遲等信息來評估設計是否符合時序要求。

靜態(tài)時序分析的目標

STA的主要目的是確保電路在每個時鐘周期內(nèi)能夠穩(wěn)定工作,滿足時序要求,避免由于時序違例導致的功能錯誤。例如,信號從一個觸發(fā)器傳播到下一個觸發(fā)器的時間不能超過時鐘周期的長度,否則可能導致數(shù)據(jù)丟失或錯誤。

STA的基本原理

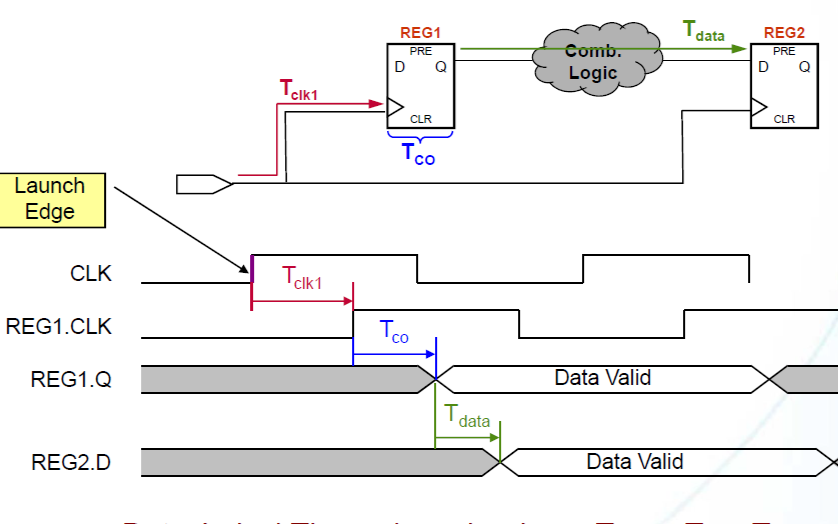

STA通過靜態(tài)地計算信號在電路中從一個觸發(fā)器(或寄存器)到下一個觸發(fā)器的傳播時間,并將這些傳播時間與時鐘周期進行比較,以確保設計中的所有路徑在時序上都符合要求。它并不模擬信號的實際值,只分析電路的時序特性,因此非常高效,適用于大規(guī)模電路的驗證。

STA的主要步驟

路徑識別:STA首先識別電路中的時鐘路徑,即從時鐘源到觸發(fā)器的路徑。在這些路徑中,時鐘信號需要傳播和同步。

計算傳播延遲:對于每一條時鐘路徑,STA計算信號從一個觸發(fā)器到下一個觸發(fā)器的傳播延遲。這包括了電路中各種元器件(如邏輯門、寄存器等)的延遲以及連線的傳播延遲。

時鐘周期與路徑延遲比較:將計算得到的傳播延遲與時鐘周期進行比較。如果路徑延遲小于時鐘周期,那么該路徑是合格的;如果路徑延遲超過時鐘周期,就存在時序違例,可能導致信號同步問題。

時序分析:分析過程中,STA會檢查兩種關鍵時序:建立時間(Setup Time)和保持時間(Hold Time)。

建立時間:信號必須在時鐘沿到達之前穩(wěn)定到一定時間,以確保觸發(fā)器正確捕獲信號。

保持時間:信號必須在時鐘沿后保持穩(wěn)定,避免出現(xiàn)數(shù)據(jù)錯誤。

STA的分析方法

STA主要通過兩種方式進行時序檢查:

最大延遲(Max Path Delay):檢查數(shù)據(jù)路徑的最大傳播延遲是否小于時鐘周期,確保數(shù)據(jù)能夠及時到達目標觸發(fā)器。

最小延遲(Min Path Delay):檢查數(shù)據(jù)路徑的最小傳播延遲,確保信號不會因為過早到達而引起錯誤。

STA的常見問題

時序違例:如果某條路徑的傳播延遲超過時鐘周期,就會出現(xiàn)時序違例,導致芯片無法正確執(zhí)行任務。

信號干擾:時序分析過程中,如果信號線長或交叉不當,會增加信號傳播延遲,影響時序準確性。

時鐘偏移:如果時鐘源不穩(wěn)定或者不同部分的時鐘信號不同步,也可能導致時序違例。

STA的優(yōu)勢

高效性:STA通過靜態(tài)分析計算路徑延遲,不需要模擬電路的每個狀態(tài),因此在大型電路設計中具有很高的計算效率。

準確性:STA能夠提供精確的時序信息,幫助設計人員發(fā)現(xiàn)和解決潛在的時序問題。

全面性:STA能夠覆蓋設計中的所有時鐘路徑,確保設計的每個部分都滿足時序要求。

STA的局限性

無法捕捉動態(tài)行為:STA僅分析電路的靜態(tài)時序特性,無法捕捉到動態(tài)行為中的時序問題,例如由于電源波動引起的時序問題。

無法驗證所有功能:STA主要用于驗證時序,無法檢查電路的邏輯正確性和功能完整性,因此通常需要與其他仿真工具聯(lián)合使用。

STA的應用

芯片驗證:STA廣泛應用于芯片設計中的時序驗證,尤其是在SoC(系統(tǒng)級芯片)設計中。它幫助設計人員確保芯片在實際應用中的時序穩(wěn)定性和可靠性。

時鐘樹優(yōu)化:STA幫助設計人員優(yōu)化時鐘樹的布局和時鐘信號的傳播路徑,從而減少時序違例。

后仿驗證:STA通常是后仿階段的一部分,幫助設計團隊在芯片設計接近完成時進行時序檢查,確保設計能夠按預期工作。

總結

靜態(tài)時序分析(STA)是一項重要的芯片設計驗證技術,它通過分析電路的時鐘路徑和信號傳播延遲,確保芯片設計在時序上沒有違例。STA能夠有效提高設計的可靠性和穩(wěn)定性,尤其在大型復雜的芯片設計中,能夠高效地檢測出潛在的時序問題。因此,它是芯片設計中不可或缺的工具之一。

-

集成電路

+關注

關注

5425文章

12071瀏覽量

368547 -

靜態(tài)時序分析

+關注

關注

0文章

29瀏覽量

9688

原文標題:如何理解芯片設計中的STA?

文章出處:【微信號:bdtdsj,微信公眾號:中科院半導體所】歡迎添加關注!文章轉載請注明出處。

發(fā)布評論請先 登錄

同步電路設計中靜態(tài)時序分析的時序約束和時序路徑

集成電路設計中靜態(tài)時序分析介紹

集成電路設計中靜態(tài)時序分析介紹

評論