文章來源:半導體全解

原文作者:圓圓De圓

高性能計算(High Performance Computing, HPC)以超高的計算性能廣泛應用于國民經(jīng)濟的各個領域,不僅用于氣候模擬、石油勘探等傳統(tǒng)產(chǎn)業(yè),在生命科學、大數(shù)據(jù)等領域成為研究和解決挑戰(zhàn)性問題的重要工具。高性能計算需要配備超強儲存能力,本文對先進的存儲技術做了簡單介紹。

高性能計算主要致力于開發(fā)超級計算機和運行在高性能計算機上的應用軟件,提升并行計算效率,用于處理復雜的科學計算問題。

隨著軍民科技等不同領域?qū)?shù)據(jù)處理需求的不斷提高,多個國家研究者相繼提出運算速度達到每秒百億億次浮點運算的計算目標,Summit、神威太湖之光、天河二號等超級計算機應運而生。

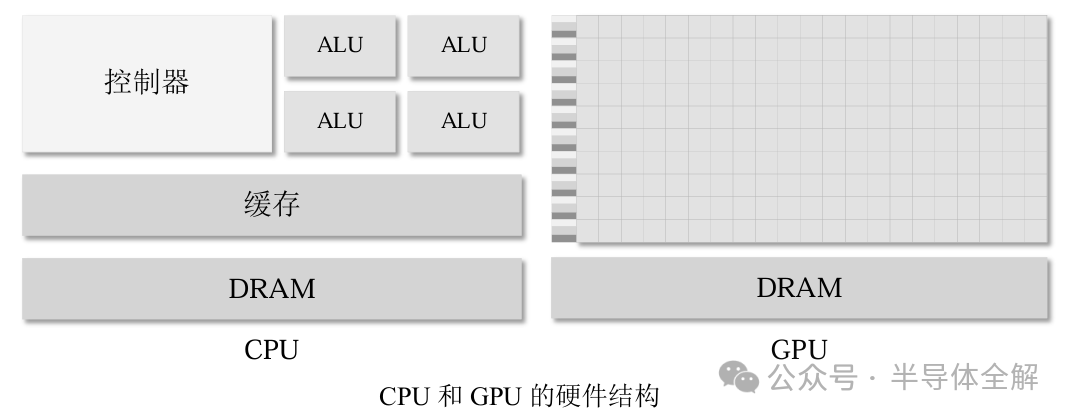

存儲系統(tǒng)是計算機體系結(jié)構中重要的組成部分,處理器核中計算所需要的數(shù)據(jù)以及處理后的數(shù)據(jù)都需要存儲到存儲系統(tǒng)中。

處理器核與存儲系統(tǒng)之間需要傳輸各種數(shù)據(jù)信息和指令信息,所以存儲訪問通信極大程度影響著整個計算系統(tǒng)的性能。

在未來高性能計算系統(tǒng)中,處理器核的數(shù)量,處理器核的計算速度,存儲系統(tǒng)的容量,以及存儲系統(tǒng)的帶寬等方面都在不斷增長,新型存儲的出現(xiàn)相對于傳統(tǒng)存儲有優(yōu)勢,也有挑戰(zhàn)。

對各類存儲系統(tǒng)組織形式、內(nèi)部結(jié)構的研究有利于我們設計更匹配的存儲訪問互聯(lián)網(wǎng)絡,有效提高訪存帶寬優(yōu)勢,降低訪問時延,降低整體功耗等。

目前,國內(nèi)外高性能微處理器的學術研究和工業(yè)實踐都在不斷改進創(chuàng)新,存儲系統(tǒng)的組織結(jié)構、存儲介質(zhì)、存儲方式等方面也在不斷發(fā)展突破。

一、傳統(tǒng)存儲系統(tǒng)

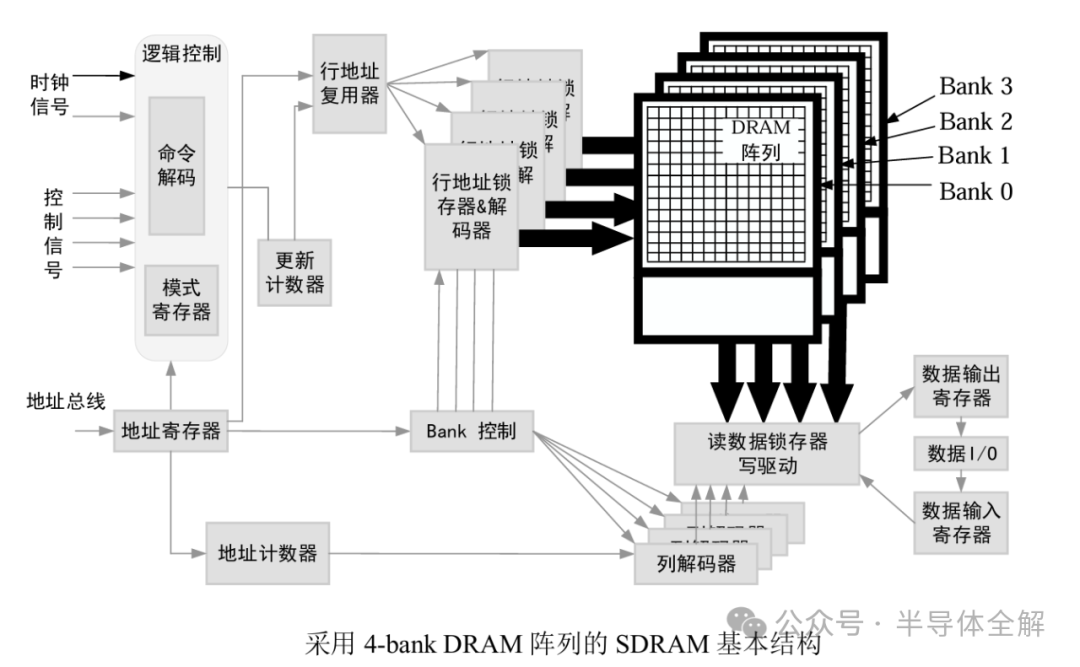

傳統(tǒng)存儲系統(tǒng)主要以DRAM構成,DRAM cell是存儲系統(tǒng)中最基本的存儲單元。

存儲單元在存儲系統(tǒng)內(nèi)部按照行(row)和列(column)的形式進行排布形成一個bank。 一個存儲模塊(memory module)內(nèi)部可以包含多個 bank。

Rank 是存儲系統(tǒng)中對于一個或多個存儲模塊所組成集合的統(tǒng)稱。

Rank 中存儲模塊的數(shù)量由單個存儲模塊位寬以及存儲系統(tǒng)的數(shù)據(jù)位寬決定,例如一個存儲系統(tǒng)的數(shù)據(jù)位寬為64位,每一個存儲模塊的數(shù)據(jù)位寬為16位,則在一個rank 中需要使用4個存儲模塊進行并行訪問,實現(xiàn)存儲系統(tǒng)中數(shù)據(jù)讀寫需求。

在搭建存儲系統(tǒng)中,除了需要考慮存儲模塊的位寬以外,還需要考慮存儲模塊的存儲容量以及系統(tǒng)總?cè)萘恐g的匹配關系。

在對存儲系統(tǒng)進行一次訪問時,存儲訪問控制器會根據(jù)存儲訪問地址首先會決定訪問哪一個 rank,其次決定訪問的bank、row 和 column。

二、新型存儲系統(tǒng)

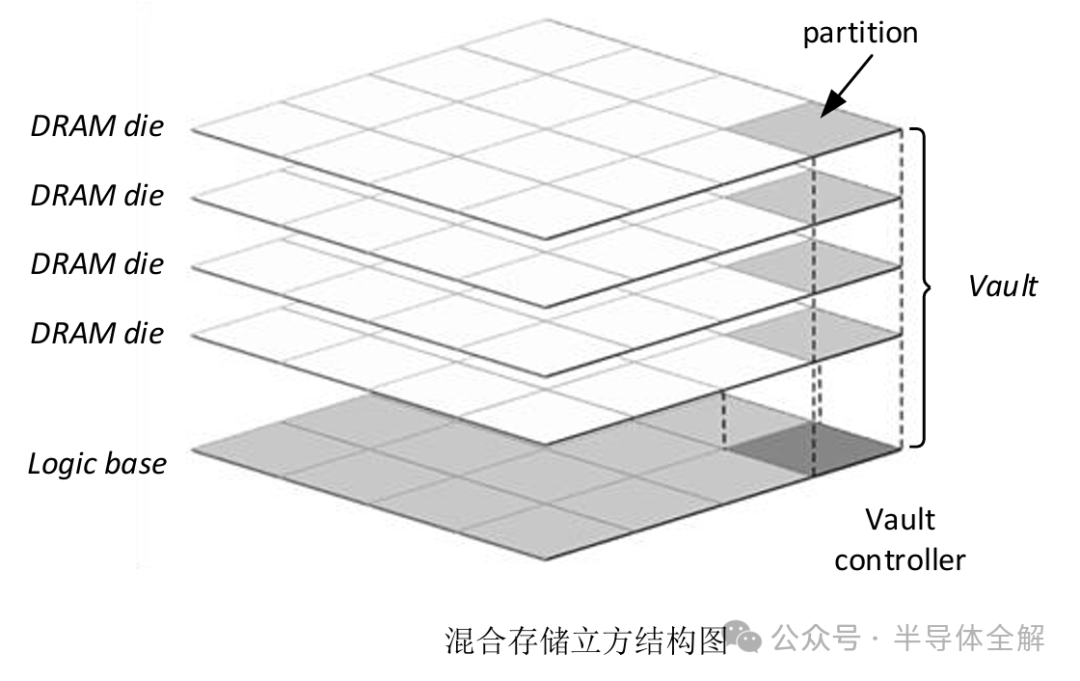

目前出現(xiàn)的新型存儲可以分為兩類: 一類是在傳統(tǒng) DRAM 基礎上,利用三維集成技術堆疊而成的三維存儲,諸如 HMC、HBM 等,本質(zhì)上還是 DRAM 陣列堆疊, 屬于易失性存儲介質(zhì);

HMC 由 DRAM 層(DRAM layer,4 層或 8 層)和邏輯層(logic layer,1 層)構成。

傳統(tǒng) DRAM 中基本概念包括 rank,bank,column,row,HMC 將 DRAM 進 行三維堆疊后,用 vault 代替了 rank,每個 vault 在功能上和操作上都是獨立的。

每個 vault 在邏輯層都設置了一個對應的存儲控制器(即 vault controller),用于管理 vault 內(nèi)的所有存儲操作(memory reference operations),決定該 vault 的時序要求。

刷新操作也由vault controller 控制,而不再是主存儲控制器中進行控制。每個 vault 控制器有一個緩沖查詢操作的隊列,查詢操作的處理不再是按序而是按需求進行。因此,響應信息從vault 操作返回外部串行 I/O 接口有可能是亂序的。而請求信息從同一條外部串行鏈路到同一個 vault/bank 是按序處理,請求信息從不同的外部串行鏈路到同一個 vault/bank 不能保證是按序處理,所以都需要經(jīng)過主控制器進行管理。

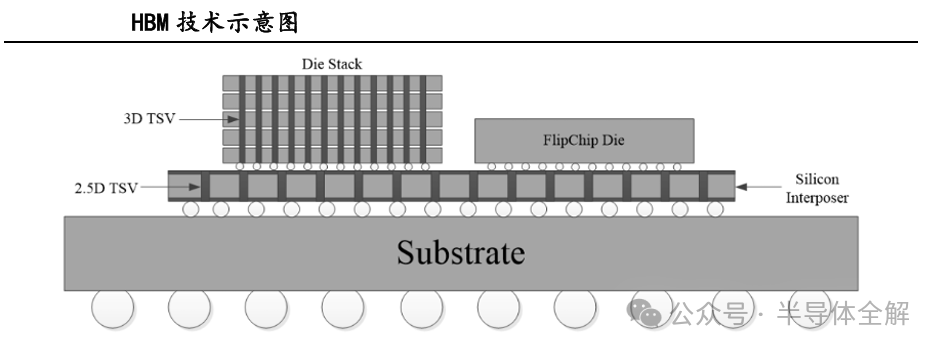

三、HBM (High Bandwidth Memory)

HBM 是另一種典型的三維堆疊 DRAM 存儲,AMD, Nvidia 以及 Hynix 等公司針對 HBM 都進行了相關技術研究。

一般由 4 到 8 個 DRAM die 堆疊而成。每個存儲控制器都是獨立定時和控制。HBM 是成本和帶寬方面的“中間”選項,專為高性能 GPU 環(huán)境設計,較 HMC 成本低,因此具有較高的研究價值。

四、相變存儲器 (PCM)

另一類是非易失性存儲 NVM,諸如 PCM、RRAM 等,存儲基本單元結(jié)構發(fā)生改變,存儲狀態(tài)以及存取方式也相應改變,不同 NVM 之間的差異性也較大。

相變存儲器(Phase Change Memory,PCM)其存儲原理為利用硫化物材料在“非結(jié)晶態(tài)和結(jié)晶態(tài)兩種狀態(tài)間阻值的變化進行數(shù)據(jù)存儲,其讀取速度與 DRAM 相近, 常用于代替或與 DRAM 混合構成計算機存儲,目前,工業(yè)界的公司如 Intel、美光、 IBM、惠普、Numonyx、三星、STMicroelectronics 等都相繼投入研究并生產(chǎn)。

五、電阻式存儲器 (RRAM)

電阻式存儲器(Resistive Random Access Memory, RRAM)的存儲原理為通過對中間的金屬氧化物加壓的方式改變阻值進行數(shù)據(jù)存儲,屬于另外一類非易失性存儲。 實現(xiàn)不同的存儲性能,可以應用在計算機系統(tǒng)的各級存儲中,目前 Rambus、Panasonic、 Adesto Technologies、SHAPP、IMEC,Unity 等公司陸續(xù)投入到 RRAM 的研究與開發(fā)中。

六、新型混合存儲的研究

隨著高性能計算系統(tǒng)對運算能力需求的不斷提升,計算系統(tǒng)面臨處理器核到存儲系統(tǒng)(各級緩存和主存)的訪問帶寬、時延、能耗、存儲系統(tǒng)的處理時間、系統(tǒng)并行計算的可擴展性等巨大的技術瓶頸。

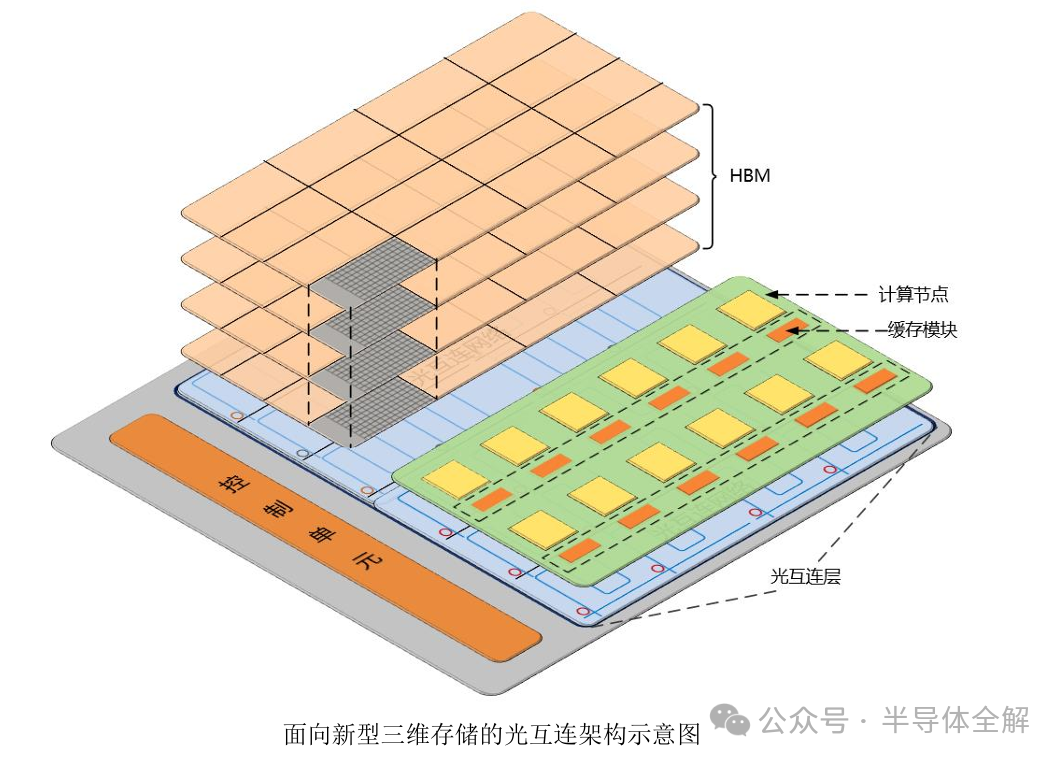

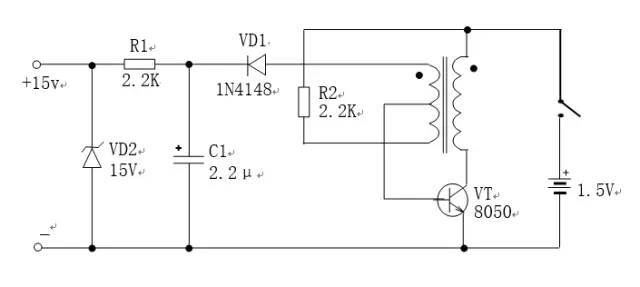

針對高性能計算類應用計算數(shù)據(jù)量大、計算復雜性高、訪存壓力大及訪存功耗高等問題,出現(xiàn)了一種面向新型三維存儲的互連網(wǎng)絡架構,利用2.5D集成技術,將高帶寬存儲HBM集成在基底層上,且在同一基底層上集成計算層,在存儲層與計算層通過光互連網(wǎng)絡層進行互連,如圖所示。

計算層中包括各個計算節(jié)點與緩存節(jié)點,高帶寬存儲HBM作為主存,與計算層共同集成在基底層上。

通過合理配置光互連結(jié)構布局,分配合適數(shù)量的光波長資源,提供計算節(jié)點與存儲模塊間高效的通信可行性。同時,電控制單元負責控制光互連網(wǎng)絡的資源配置及光電器件的狀態(tài)。

七、先進存儲技術解決辦法

國內(nèi)外研究人員針對存儲訪問瓶頸采取的解決思路可分為三種: 第一種是采用新型緩存機制,充分利用片上緩存資源,通過更高效的緩存數(shù)據(jù)管理機制解決訪存瓶頸,例如非一致性緩存訪問(Non-Uniform Cache Access, NUCA),反應性非均勻緩存訪問(Reactive Non-Uniform Cache Access, R-NUCA)等結(jié)構。

第二種是采用近存儲計算(Processing in Memory, PIM),將片上處理器核的部分計算功能轉(zhuǎn)移到存儲系統(tǒng)端,通過減少遠距離訪存讀寫數(shù)據(jù)量解決訪存瓶頸。

第三種是設計高性能存儲訪問互連架構,通過訪存高效互連架構的構建,提升處理器核訪問存儲系統(tǒng)的并行性,降低訪問時延、功耗、能耗等。

根據(jù)不同應用需求,不同系統(tǒng)架構需求,三種思路的解決方式各有不同的特點與優(yōu)勢。

采用新型的緩存機制與近存儲計算所受到的應用類型限制較大,設計處理器核與存儲系統(tǒng)之間高性能互連架構,更具有普遍性優(yōu)勢。

隨著硅光技術、三維集成技術、光通信技術的不斷發(fā)展,更有利于處理器核與存儲系統(tǒng)間訪存互連架構的設計,突破高性能計算中的訪存瓶頸。

-

處理器

+關注

關注

68文章

19833瀏覽量

233898 -

存儲技術

+關注

關注

6文章

754瀏覽量

46272 -

計算機

+關注

關注

19文章

7638瀏覽量

90348 -

存儲芯片

+關注

關注

11文章

931瀏覽量

44010

原文標題:一文了解存儲芯片原理與先進存儲技術

文章出處:【微信號:bdtdsj,微信公眾號:中科院半導體所】歡迎添加關注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

一文搞懂各種RAM、ROM存儲的異同點

一文搞懂UPS主要內(nèi)容

一文搞懂開關電源波紋的產(chǎn)生

一文搞懂Rockchip內(nèi)核存儲庫

一文徹底搞懂C語言指針

一文解析什么是固態(tài)存儲技術

一文解析阻變存儲技術

一文搞懂DDR內(nèi)存原理

一文搞懂先進存儲技術

一文搞懂先進存儲技術

評論