時源芯微 專業EMC解決方案提供商 為EMC創造可能

靜電放電(ESD)是電子設備可靠性設計的核心挑戰之一。其瞬間高電壓(可達數十kV)、短脈沖(ns級)的特性,極易通過直接接觸或空間耦合侵入設備,導致系統復位、數據錯誤甚至硬件損毀。本文基于IEC 61000-4-2標準,結合典型行業案例,系統梳理ESD問題的診斷流程與根治方法,為工程師提供可復用的分析框架。

一、ESD失效現象分類與初步定位

ESD問題的表現復雜多樣,需從現象反推干擾路徑與敏感點:

| 失效現象 | 可能原因 | 典型案例 |

|---|---|---|

| 系統復位/死機 | 放電電流耦合至MCU復位引腳或電源網絡 | 某智能門鎖接觸放電±6kV時死機 |

| 顯示異常(花屏/閃屏) | ESD通過外殼或接口耦合至顯示驅動電路 | 工業HMI屏空氣放電±8kV出現條紋 |

| 通信中斷/誤碼 | 放電噪聲干擾高速信號線(如USB、CAN) | 車載中控屏HDMI接口放電后無輸出 |

| 傳感器數據跳變 | ESD通過屏蔽層或地線干擾模擬信號 | 醫療監護儀血氧值接觸放電后漂移 |

診斷第一步:通過ESD測試復現故障現象,記錄放電點位(如金屬外殼、接口、縫隙)與失效模式的對應關系。

二、ESD耦合路徑分析方法

ESD能量主要通過以下路徑侵入設備,需針對性排查:

直接傳導路徑

金屬外殼放電:電流通過外殼傳導至內部電路地,導致地電位突變。

診斷方法:測量外殼接地點與PCB地之間的阻抗(目標<1Ω),檢查是否存在虛焊或氧化。

接口放電:放電電流通過信號線或電源線進入核心電路。

診斷方法:在接口處串聯電流探頭,觀察放電瞬間電流幅值及頻譜。

空間耦合路徑

電場耦合:高壓靜電場通過寄生電容耦合至敏感節點(如時鐘線)。

診斷方法:使用近場探頭掃描放電點附近電場強度,定位耦合熱點。

磁場耦合:快速變化的放電電流產生瞬態磁場,感應出環路電壓。

診斷方法:檢查敏感信號環路面積(如復位電路),優化布局以減少磁通穿透。

案例輔助:某無人機遙控器在±10kV空氣放電時失控。

驗證手段:用ESD槍模擬放電,同時用頻譜儀觀測射頻信號噪聲電平;

根治措施:在天線區域增加金屬屏蔽罩,并在射頻芯片電源端添加TVS管。

三、敏感電路定位與防護驗證

敏感電路特征

高阻抗節點:如MCU復位引腳、傳感器輸入引腳,易受電場干擾。

長走線或未屏蔽信號:如I2C、SPI總線,易形成接收天線。

電源網絡薄弱點:去耦電容不足或布局不合理,導致電源電壓塌陷。

定位工具與步驟

工具:紅外熱像儀(定位放電發熱點)、示波器(捕獲瞬態電壓)、TDR(檢測阻抗突變)。

步驟:

在ESD測試中實時監測電源電壓、復位信號、關鍵時鐘的波形;

對比正常與失效狀態下的信號差異,鎖定敏感電路;

通過割線、屏蔽或增加濾波驗證防護效果。

案例輔助:某血糖儀接觸放電±4kV時測量值異常。

敏感點定位:放電時模擬前端(AFE)電源電壓出現200mV跌落;

根因分析:AFE電源去耦電容僅0.1μF,儲能不足;

整改驗證:并聯10μF鉭電容后,電壓跌落降至20mV,數據恢復正常。

四、ESD防護設計層級與整改策略

基于“防-泄-抗”三級防護理念,逐層削弱ESD能量:

| 防護層級 | 目標 | 典型措施 |

|---|---|---|

| 一級防護 | 阻止ESD侵入 | 接口TVS管、金屬外殼低阻抗接地、絕緣隔離 |

| 二級防護 | 泄放/吸收殘余能量 | PCB地平面優化、共模扼流圈、去耦電容陣列 |

| 三級防護 | 增強電路抗擾度 | 軟件看門狗、信號冗余校驗、關鍵寄存器備份 |

整改策略優先級:

結構優化(成本最低):例如增加接地點、縮短外殼縫隙;

硬件加固(效果顯著):如添加TVS管、優化去耦電容;

軟件容錯(補充手段):針對無法硬件隔離的敏感功能。

五、典型行業案例深度解析

案例1:智能手表觸摸屏ESD失靈

現象:空氣放電±8kV后觸摸功能失效,需重啟恢復。

診斷:

近場探頭掃描發現放電點靠近觸摸芯片天線;

示波器捕獲觸摸信號線在ESD期間出現3.5V脈沖(正常為1.8V)。

整改:

一級防護:觸摸屏FPC增加銅箔屏蔽層,邊緣接地;

二級防護:觸摸芯片電源端并聯4.7μF MLCC電容;

三級防護:固件增加觸摸信號異常狀態檢測與自恢復邏輯。

結果:通過±15kV空氣放電測試,故障率降為0。

案例2:工業PLC模塊ESD通信中斷

現象:接觸放電±6kV時RS485通信丟包。

診斷:

電流探頭檢測到放電電流通過外殼流入PCB地平面;

整改:

一級防護:外殼接地點增加磁珠(100Ω@100MHz)隔離數字地;

二級防護:RS485線路增加TSCF4532-2L601MT共模扼流圈(600Ω@100MHz);

三級防護:通信協議添加CRC校驗與重傳機制。

結果:ESD抗擾度從±6kV提升至±12kV。

六、總結與設計預防建議

設計階段預防:

遵循“屏蔽-濾波-接地”黃金法則,在PCB布局初期規劃ESD防護區域;

對高速信號、復位電路、電源入口等敏感節點預留TVS管與濾波電容位號。

測試驅動優化:

使用ESD模擬器進行預測試,結合熱成像儀與示波器快速定位問題;

對比不同整改方案的成本與效果,選擇最優解(如TVS管型號、屏蔽材料厚度)。

跨學科協同:

結構工程師(外殼接地)、硬件工程師(濾波設計)、軟件工程師(容錯邏輯)需協同工作,打破ESD整改孤島。

ESD問題本質是能量路徑與電路敏感性的博弈。通過系統化的診斷分析、分層防護設計與多維度驗證,可顯著提升設備魯棒性。正如EMC領域經典理論所言:“沒有完美的單點方案,只有全局優化的防護體系。”

參考文獻:

IEC 61000-4-2: Electrostatic Discharge Immunity Test

《ESD防護設計手冊》(臺灣全華科技)

華為技術文檔 《ESD問題定位與解決指南》

EDN電子技術設計. ESD失效分析十大工具解析

審核編輯 黃宇

-

ESD

+關注

關注

50文章

2279瀏覽量

175570

發布評論請先 登錄

芯知識|廣州唯創電子語音芯片雜音與破音問題全解析:從診斷到解決

時源芯微 大電源EMC設計的挑戰

納芯微通用信號鏈產品矩陣介紹

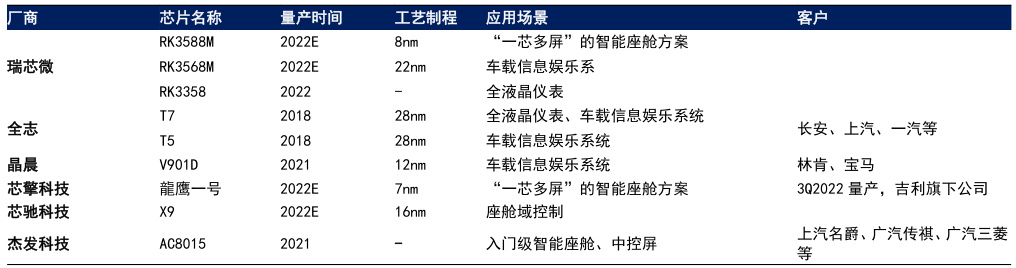

瑞芯微芯片全景與選型推薦

瑞芯微平臺Android系統串口測試方法,觸覺智能RK3562開發板演示

瑞芯微主板/開發板Linux系統播放音頻方法,觸覺智能RK3562開發板演示

時源芯微——電源電纜導致輻射超標定位子流程

時源芯微EMC前車燈案例

從JESD204B升級到JESD204C時的系統設計注意事項

時源芯微 ESD問題通用診斷分析方法:從現象定位到根治方案

時源芯微 ESD問題通用診斷分析方法:從現象定位到根治方案

評論