來源: 疾鋒勁草,作者:風(fēng)生水起

拿到一個ST的宣傳材料,該資料介紹了Si/SiC混合功率器件可能是過渡到全SiC的中間方案,也找了文章了解了一下原理。資料有限,標(biāo)題的問題沒找到答案。有哪位大神愿意分享一下呢?

大概會分三個部分:

1、ST資料;

2、介紹一篇器件測試的論文;

3、介紹一篇綜述文章;

一、ST宣傳資料

1、結(jié)論

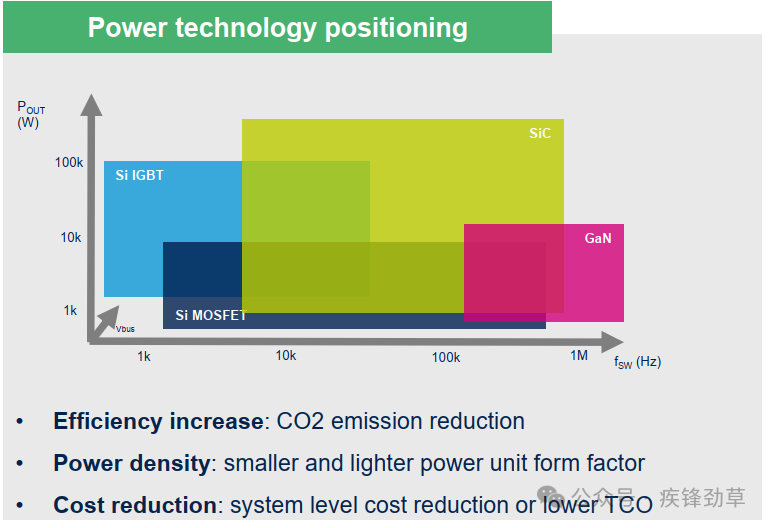

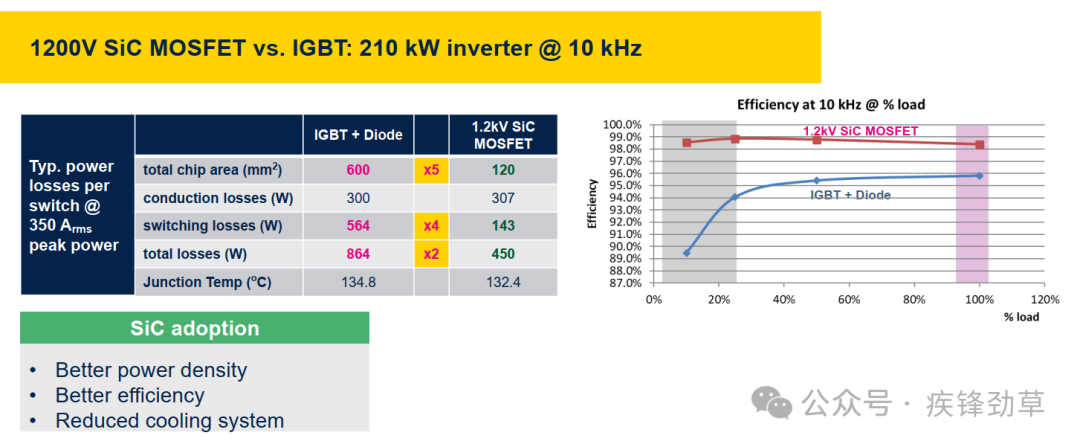

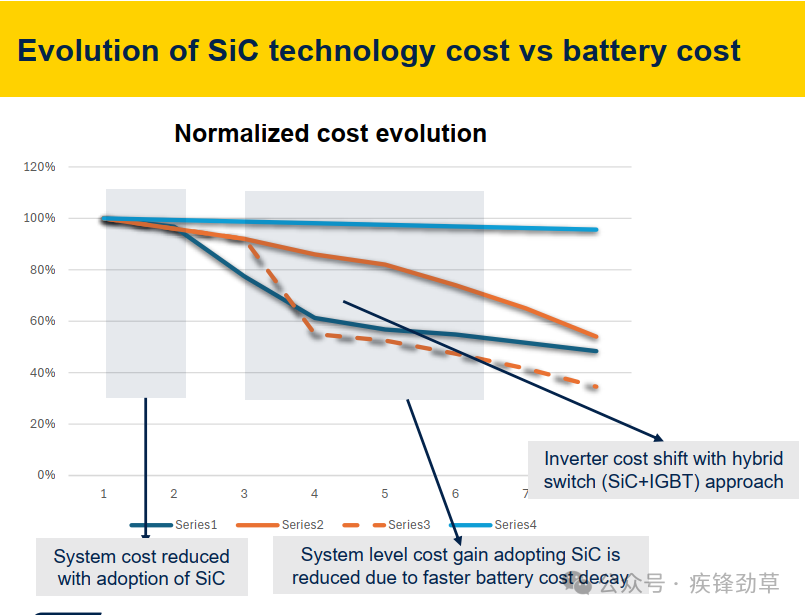

SiC基逆變器的系統(tǒng)成本效益隨著電池技術(shù)的發(fā)展而不斷提高

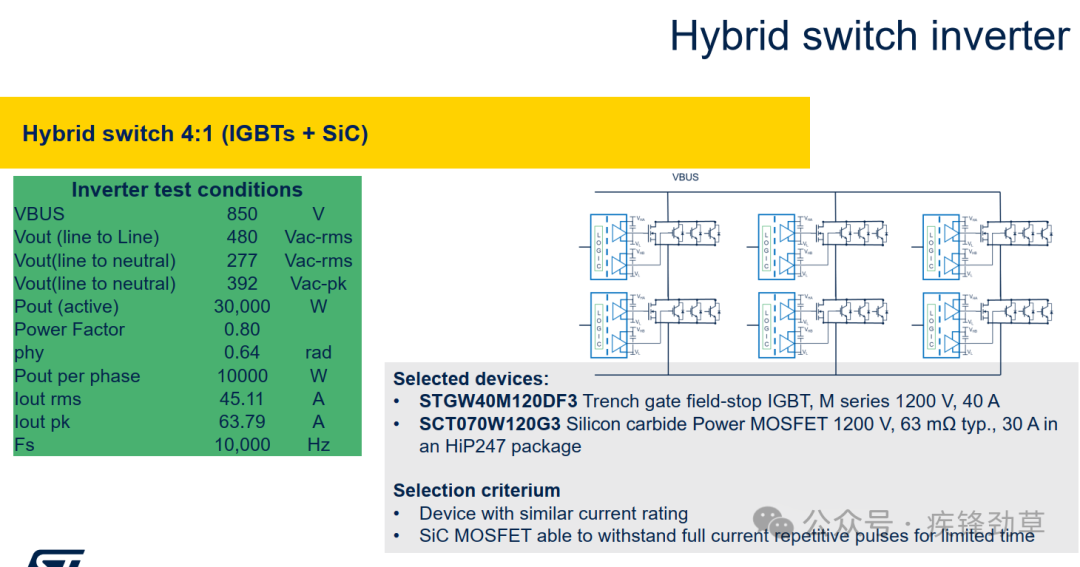

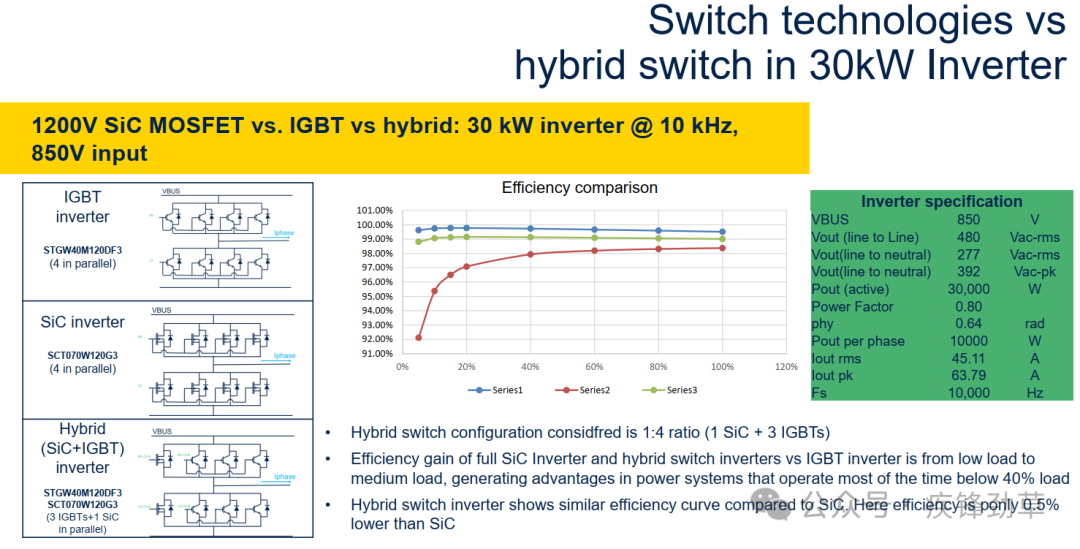

逆變器受益于下一代IGBT和SiC MOSFET的組合,這種混合開關(guān)優(yōu)化了逆變器的性能和成本,優(yōu)化的成本可能使SiC的新應(yīng)用成為可能

混合開關(guān)需要專用的柵極驅(qū)動器,ST正在柵極驅(qū)動器和功率晶體管的各個層面進(jìn)行創(chuàng)新,以引領(lǐng)逆變器設(shè)計的這一新趨勢

2、內(nèi)容

二、混合開關(guān)測試論文

High Voltage Si/SiC Hybrid Switch: An Ideal Next Step for SiC

1、介紹

SiC等高壓寬帶隙半導(dǎo)體的發(fā)展因其相對于Si的固有材料優(yōu)勢而受到廣泛關(guān)注。MOSFET或JFET等SiC功率開關(guān)顯示出比Si IGBT等硅功率器件明顯更好的特性,特別是在顯著降低開關(guān)損耗方面。大規(guī)模采用SiC功率器件面臨的一個主要問題仍然是更高的材料和制造成本。此外,高壓MOSFET的一個固有缺點是高導(dǎo)通損耗,即使對于SiC MOSFET也是如此。在高壓和高溫下尤其如此。相反,IGBT最為人所知的是,由于強(qiáng)電導(dǎo)率調(diào)制,其正向電壓降較低,但在關(guān)斷期間,電流尾部會導(dǎo)致更高的關(guān)斷損耗。因此,提出了通過并聯(lián)連接IGBT和MOSFET來結(jié)合MOSFET和IGBT優(yōu)點的混合MOSFET和IGBT開關(guān)。然而,迄今為止提出的混合開關(guān)都是用于低壓應(yīng)用的,IGBT和MOSFET都是硅器件。本文是高壓Si/SiC混合功率模塊的第一項已知工作,該模塊集成了并聯(lián)的高壓SiC MOSFET和Si IGBT,如圖1所示。本文討論了Si/SiC混合開關(guān)在SiC MOSFET和Si IGBT上的優(yōu)越性能及其可負(fù)擔(dān)的成本,以證明這一有前景的概念是SiC的理想下一步。

2、Si/SiC混合開關(guān)的配置與操作

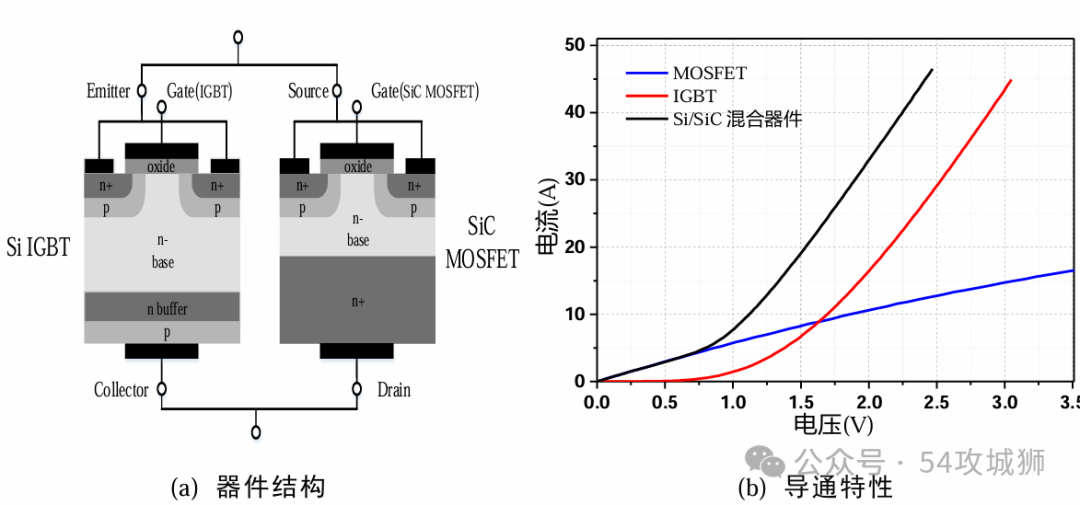

Si/SiC混合開關(guān)的配置

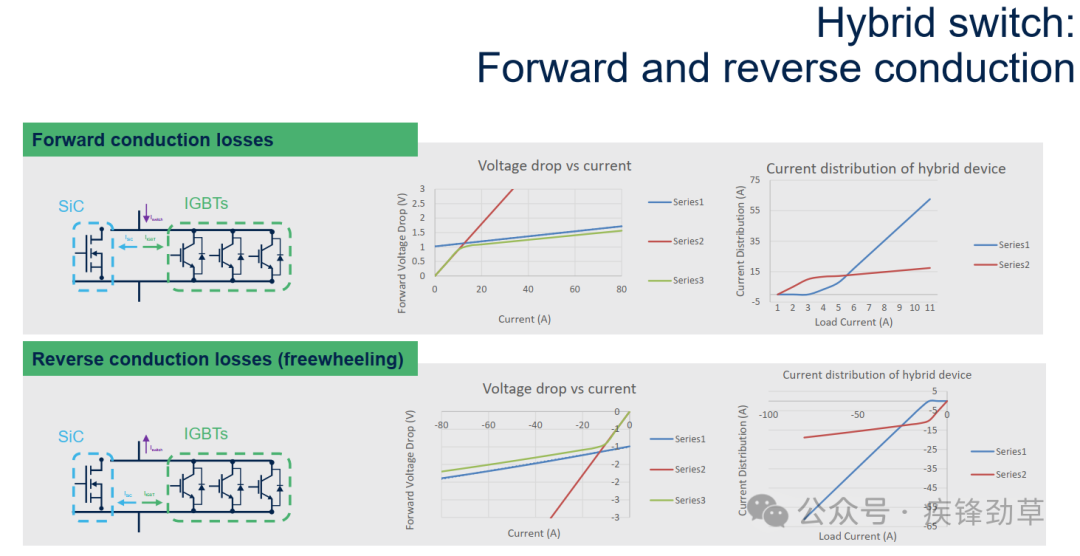

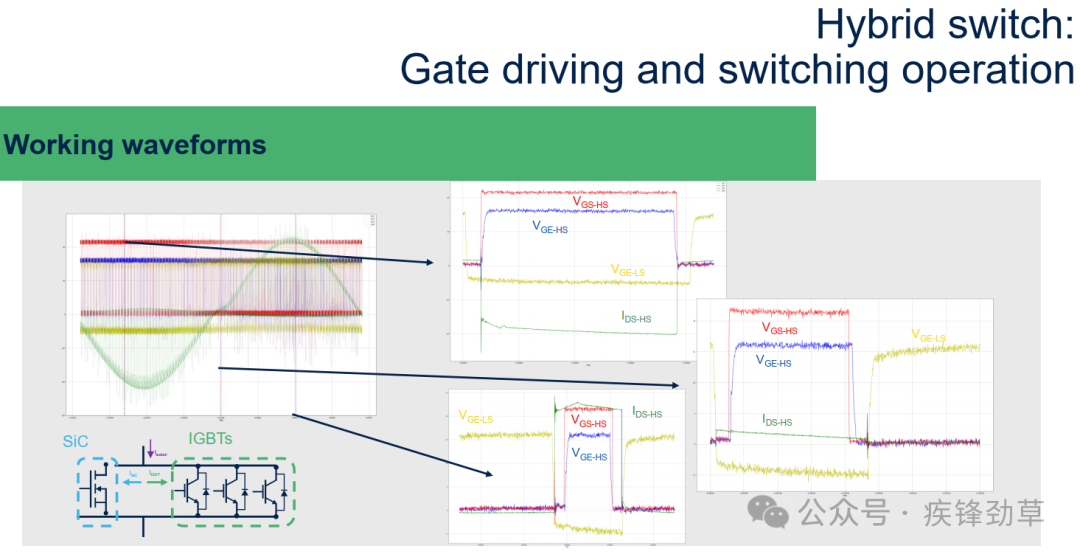

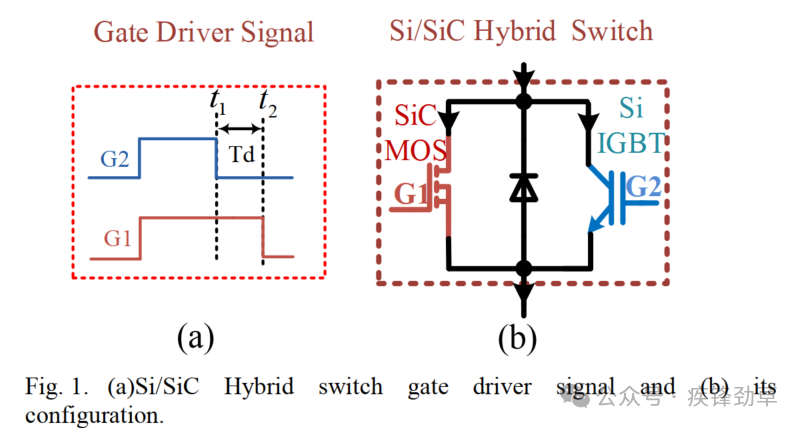

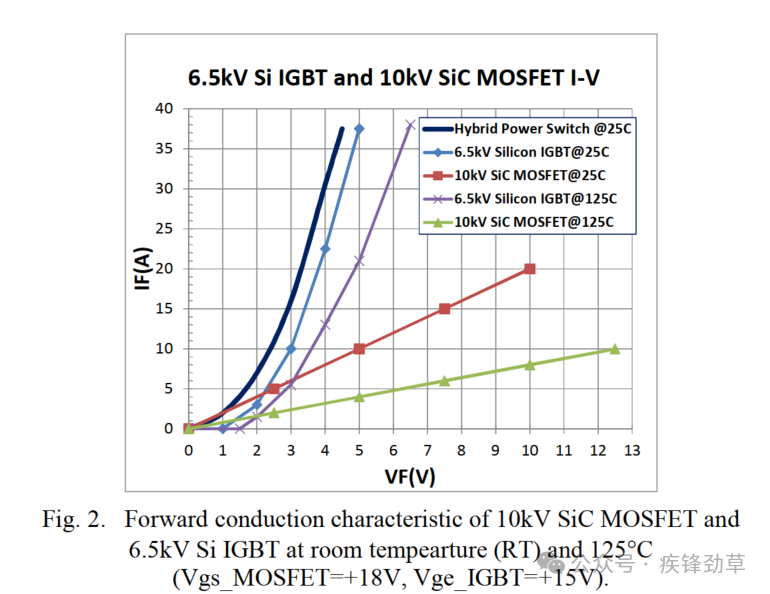

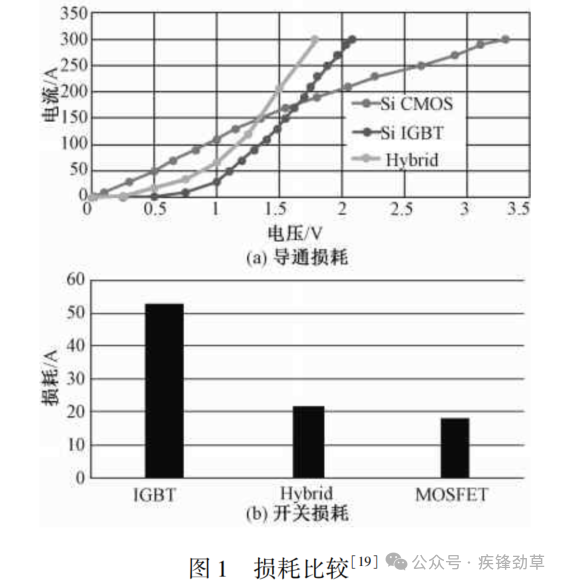

圖1顯示了所提出的Si/SiC混合開關(guān)及其柵極驅(qū)動信號,該開關(guān)集成了并聯(lián)的高壓SiC MOSFET和Si IGBT。眾所周知,IGBT等雙極半導(dǎo)體器件在高電流密度下具有更好的正向?qū)ㄌ匦?如圖2所示),MOSFET等單極半導(dǎo)體器件具有更快的開關(guān)速度和更低的開關(guān)損耗,尤其是關(guān)斷損耗。因此,為了結(jié)合IGBT和MOSFET的優(yōu)點,首先關(guān)閉Si IGBT,所有電流將換向到SiC MOSFET,然后在精心設(shè)計的延遲時間Td后關(guān)閉SiC MOSFET。這樣,利用IGBT的低導(dǎo)通損耗能力,通過混合開關(guān)實現(xiàn)了低正向?qū)▔航怠S捎赟iC MOSFET的超低關(guān)斷損耗,開關(guān)損耗將顯著降低。該概念也適用于SiC JFET。由于缺乏6.5 kV SiC器件樣品,本文中給出的結(jié)果是使用Cree的10kV/10A SiC MOSFET(芯片面積=0.48cm2)原型和ABB的商用6.5kV/25A Si IGBT(芯片面積=1.84cm2)獲得的。

正向特性比較

6.5kV Si IGBT和10kV SiC MOSFET分別在25°C和125°C下的I-V曲線如圖2所示。在較低電流(~5A)下,10kV SiC MOSFET顯示出更好的正向?qū)ㄌ匦裕?0A或更高的高電流下,Si IGBT在正向?qū)ǚ矫婢哂袎旱剐缘膬?yōu)勢。這在更高的溫度下更為明顯。混合開關(guān)在25°C下的IV曲線也如圖2所示。可以發(fā)現(xiàn),混合開關(guān)結(jié)合了Si IGBT在高電流下和SiC MOSFET在低電流下的優(yōu)點。正向傳導(dǎo)特性甚至比Si IGBT更好,因為SiC MOSFET也傳導(dǎo)總電流的一部分。

關(guān)斷延遲時間分析

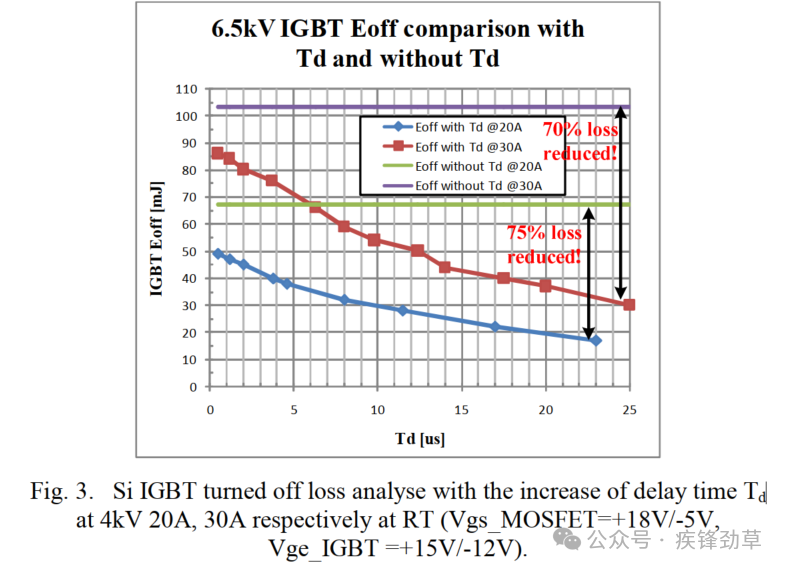

混合開關(guān)的一個主要挑戰(zhàn)是確定適當(dāng)?shù)腟iC MOSFET關(guān)斷延遲時間Td,如圖1所示。在圖3中,Si IGBT關(guān)斷損耗Eoff分別被分析為4kV、20A和30A下Td的函數(shù)。可以發(fā)現(xiàn),IGBT的Eoff隨著Td的增加而減小。在前10us,Eoff的減小速度比Td=10us后快約2倍。當(dāng)Td為20us時,與不添加Td的情況相比,可以實現(xiàn)約70%的IGBT關(guān)斷損耗降低。可以選擇10us MOSFET關(guān)斷延遲作為開關(guān)頻率和關(guān)斷損耗降低之間的折衷。

混合開關(guān)背后的原理

如圖1(a)所示,所提出的開關(guān)損耗改善背后的物理原理是IGBT分別在t1的ZVS關(guān)斷和t2的ZCS關(guān)斷下運(yùn)行。在t1,IGBT的柵極電壓被去除,IGBT中的MOSFET溝道將被快速去除。同時,電流被換向到SiC MOSFET。開放式基極中儲存的過量少數(shù)載流子將根據(jù)雙極/或少數(shù)載流子的壽命逐漸衰變。在此期間(從t1到t2),IGBT上的電壓被MOSFET的低正向電壓降箝位,該電壓降幾乎為零。因此,硅IGBT可以實現(xiàn)ZVS關(guān)斷。在Td期間,IGBT和MOSFET都施加了低電壓降,由于少數(shù)載流子復(fù)合,N基極區(qū)中的大量存儲電荷呈指數(shù)級下降。在t2,混合開關(guān)中的SiC MOSFET被關(guān)斷。如果延遲時間Td設(shè)置得足夠長,則在t2留下的存儲電荷很少。當(dāng)Si IGBT上的電壓由于SiC MOSFET關(guān)斷而增加時,只有很小的電流會通過Si IGBT為其寄生電容器充電。實現(xiàn)了硅IGBT的ZCS關(guān)斷。

圖3顯示,被測IGBT中的載流子壽命相對較高。然而,詳細(xì)分析還表明,基于exp(-t/?hl)的模型不是Eoff估計的準(zhǔn)確模型,因為損耗與t2時ZCS關(guān)斷期間的動態(tài)有關(guān),其中dV/dt由MOSFET強(qiáng)烈決定。留在IGBT中的載流子必須支持高dV/dt,因此通常會再次發(fā)生更高的載流子提取率,導(dǎo)致更高的IGBT電流,從而導(dǎo)致IGBT損耗。由于IGBT處于開基PNP模式,因此該電流還會引起額外的載流子注入,這將進(jìn)一步增加IGBT損耗,或者ZCS模式下IGBT損耗的降低沒有模型exp(-t/?hl)預(yù)測的那么低。

3、Si/SiC混合開關(guān)損耗減少分析

Si/SiC混合開關(guān)單脈沖測試

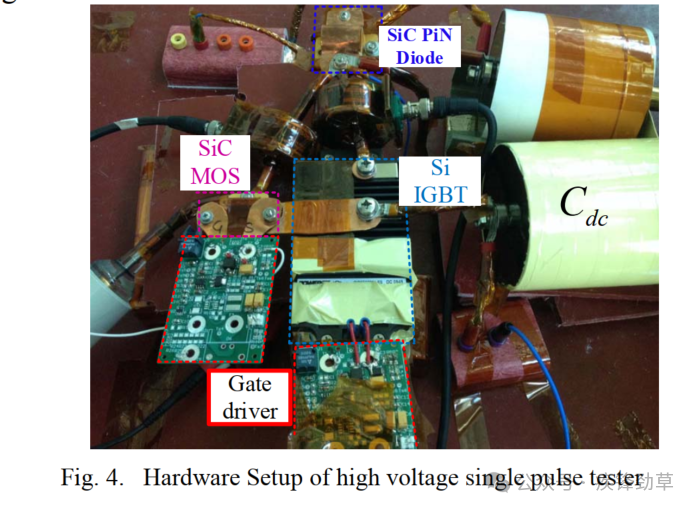

為了評估混合開關(guān)的關(guān)斷損耗改善情況,如圖4所示,開發(fā)了一種單脈沖測試儀,包括高壓直流電源、直流電容器和箝位電感負(fù)載。在單脈沖測試儀中測量了硅IGBT和混合開關(guān)的關(guān)斷損耗,將在圖6和圖7中進(jìn)行比較。

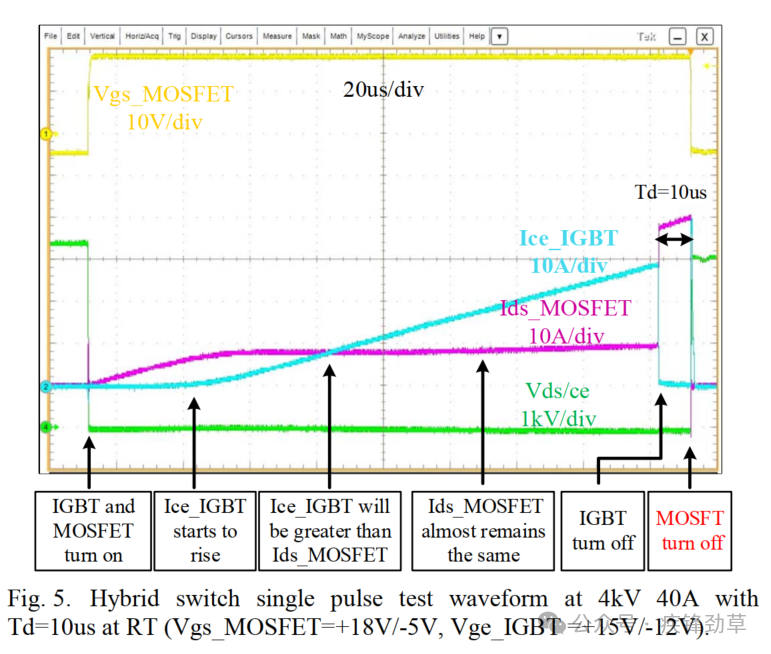

圖5顯示了混合開關(guān)的單脈沖測試波形。首先,SiC MOSFET和Si IGBT同時導(dǎo)通。由于SiC MOSFET在較低電流下的電壓降較低,幾乎所有的電流都通過SiC MOSFET。隨著總電流的增加,總電流的更大一部分通過Si IGBT。可以看出,在高電流下,大部分電流通過Si IGBT,通過SiC MOSFET Ids的電流幾乎保持不變。在關(guān)斷狀態(tài)下,SiC MOSFET在Si IGBT之后10us關(guān)斷。

關(guān)斷損耗比較

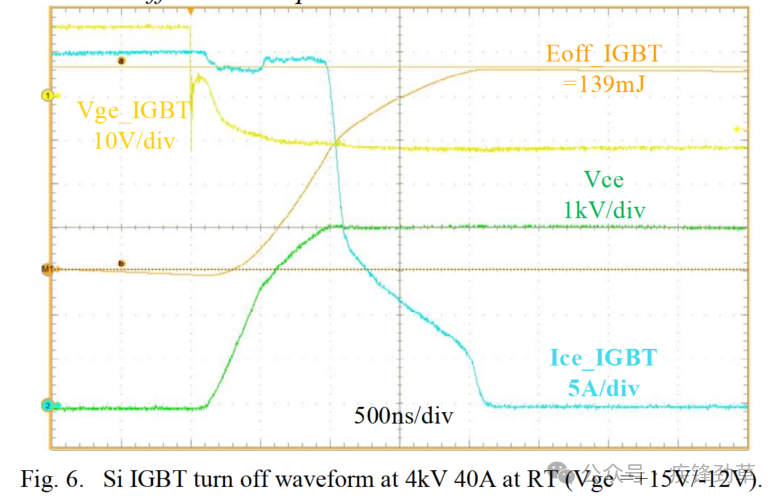

圖6顯示了標(biāo)準(zhǔn)硅IGBT關(guān)斷波形。Si IGBT在4kV、40A下的關(guān)斷損耗約為139mJ,電流變?yōu)榱愦蠹s需要2us。從同一測試儀上獲得的SiC MOSFET在4kV、40A下的關(guān)斷損耗僅為20mJ。

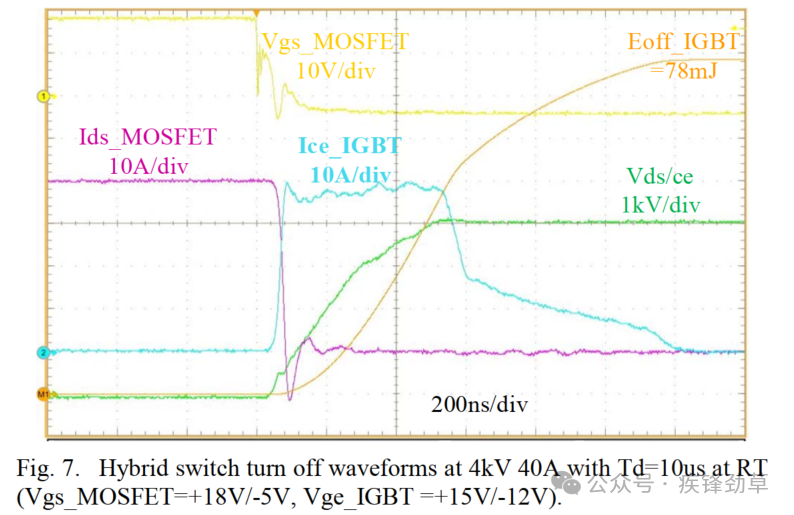

圖7顯示了混合開關(guān)在時刻t2的關(guān)斷波形。混合開關(guān)的總關(guān)斷損耗由兩部分組成,一部分是Si IGBT關(guān)斷損耗,為78mJ,另一部分是SiC MOSFET關(guān)斷損耗。因此,混合開關(guān)的總關(guān)斷損耗約為79mJ,與標(biāo)準(zhǔn)IGBT關(guān)斷相比,損耗降低了近44%。在MOSFET關(guān)斷后的快速電壓上升階段,Si IGBT中仍有大量電荷殘留,導(dǎo)致關(guān)斷損耗顯著降低,但仍然很高。在這個測試案例中,dV/dt仍然主要由IGBT而不是MOSFET決定,因此MOSFET損耗為1 mJ,而不是獨立MOSFET條件下的20 mJ。隨著延遲時間Td的延長,混合開關(guān)的關(guān)斷損耗將進(jìn)一步降低。實驗發(fā)現(xiàn),Si IGBT的開關(guān)損耗在高溫下比室溫下高出約3倍,而正向特性可以保持在較低水平。相比之下, SiC MOSFET在高溫下的Ron大約是室溫下的2倍,而開關(guān)損耗幾乎保持不變。因此,可以預(yù)期,在高溫下,Si/SiC混合開關(guān)可以實現(xiàn)更大的損耗降低。

基于Si/SiC混合開關(guān)的逆變器損耗分析

為了評估Si/SiC混合開關(guān)的損耗改善,以100kW-200kW轉(zhuǎn)換器為例,假設(shè)其開關(guān)頻率為2kHz,占空比為50%。

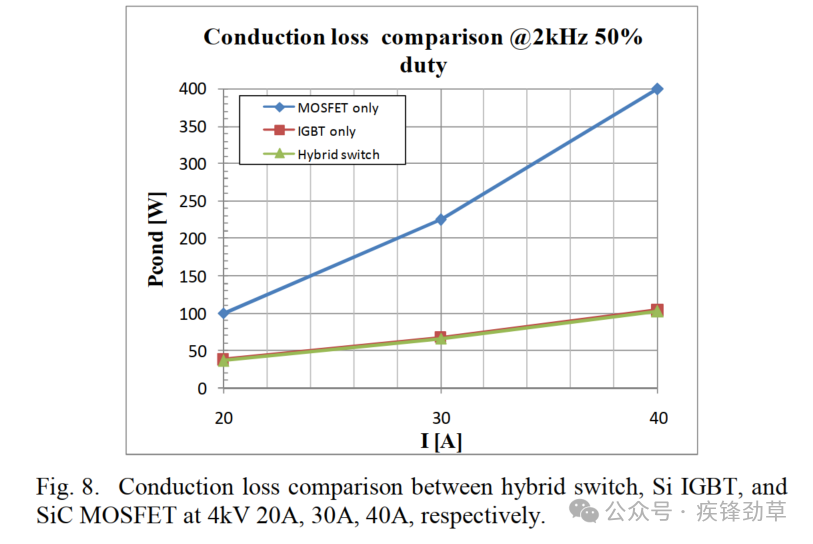

圖8分別顯示了混合開關(guān)、SiC MOSFET和Si IGBT在4kV 20A、30A和40A下的正向傳導(dǎo)損耗比較。可以發(fā)現(xiàn),混合開關(guān)和硅IGBT的導(dǎo)通損耗幾乎相同。SiC MOSFET由于其在高電流密度下的高Ron而具有最高的導(dǎo)通損耗,并且隨著電流的增加,間隙變寬。

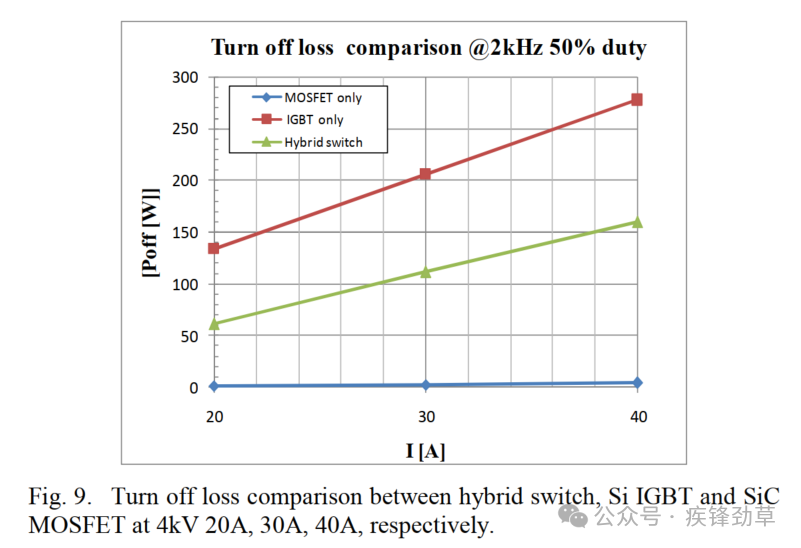

圖9分別給出了三種器件在4kV 20A、30A和40A下的關(guān)斷損耗比較。SiC MOSFET由于其快速的開關(guān)速度而具有最低的關(guān)斷損耗,而Si IGBT具有最高的關(guān)斷損失。由于SiC MOSFET在關(guān)斷狀態(tài)下的幫助,混合開關(guān)的關(guān)斷損耗比Si IGBT低約50%。

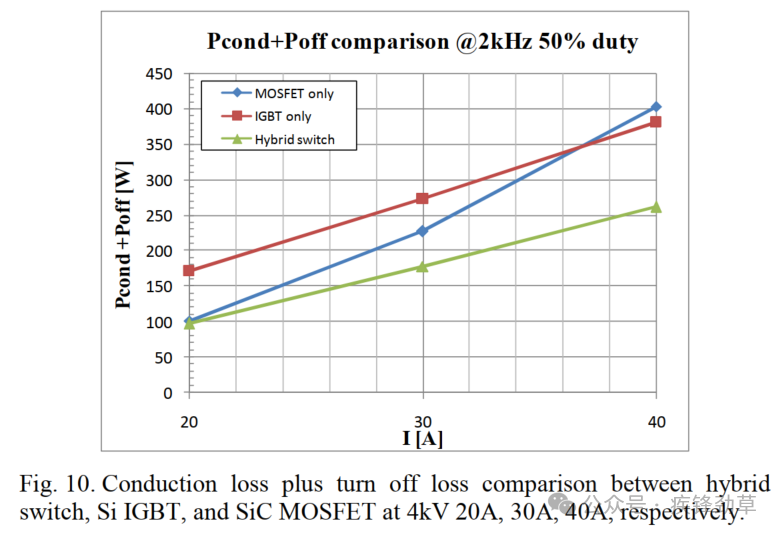

圖10分析了包括傳導(dǎo)損耗和關(guān)斷損耗在內(nèi)的總損耗。與Si IGBT和SiC MOSFT相比,所提出的混合開關(guān)的總損耗降低了約35%。隨著電流的增加,優(yōu)勢也在擴(kuò)大。總之,混合開關(guān)在降低損耗方面表現(xiàn)出了優(yōu)越的性能,特別是在高功率應(yīng)用中。

4、混合開關(guān)的成本分析

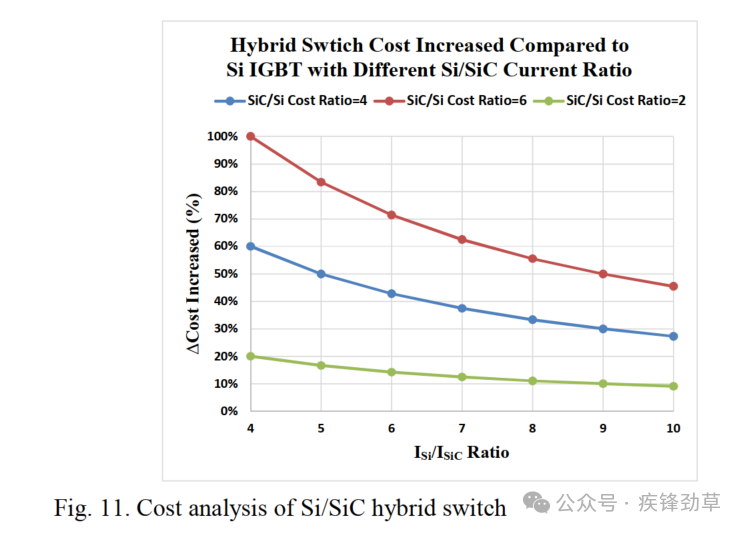

Si/SiC混合開關(guān)的成本由SiC器件與Si器件的成本比以及Si IGBT和SiC MOSFET之間的電流分布決定,如圖11所示。例如,當(dāng)SiC器件的每安培成本是Si器件的4倍(SiC/Si成本比為4),Si IGBT的額定電流是SiC MOSFET的額定電流的5倍(Si/SiC電流比為5)時,與Si IGBT相比,實現(xiàn)高達(dá)70%的關(guān)斷損耗降低只需要50%的額外成本。成本分析表明,成本增長非常溫和,同時實現(xiàn)了顯著的損失減少。較高的Si/SiC電流比意味著所需的成本增加更小。然而,Si/SiC電流比不能無限增加,因為這受到MOSFET安全工作區(qū)域的限制。SiC MOSFET需要大的關(guān)斷能力,這將是我們未來研究和分析的一部分。

5、總結(jié)

本文提出了一種高壓Si/SiC混合開關(guān)概念,作為SiC器件的自然理想下一步。與硅IGBT相比,Si/SiC混合開關(guān)的優(yōu)越性能和可負(fù)擔(dān)的成本表明了其在高壓應(yīng)用中的前景。未來,Si/SiC混合開關(guān)的導(dǎo)通過程將做更多的工作。此外,對SiC和Si器件芯片尺寸優(yōu)化的更多研究可以進(jìn)一步降低Si/SiC混合開關(guān)的成本。

三、綜述

《基于 Si IGBT / SiC MOSFET 的混合開關(guān)器件綜述 》,這篇是中文的,看起來比較方便。如下

1、介紹

近年來,由于碳化硅( SiC) 器件具有優(yōu)異的性能,如單位導(dǎo)通電阻小、可高頻開關(guān)、可高溫運(yùn)行、耐壓高、抗輻射等優(yōu)點,成為電力電子界重點研究的方向之一,具有廣闊的應(yīng)用前景[1,2] 。世界各國都在努力開發(fā) SiC 器件,并希望能夠盡快應(yīng)用到各行業(yè)的變頻器中,早日替代現(xiàn)有硅器件。

然而,受到 SiC 晶圓生長工藝和芯片加工能力限制,當(dāng)前 SiC MOSFET 的單芯片載流能力遠(yuǎn)低于Si IGBT[3] 。

制約芯片載流能力的另一因素是成本,提高芯片面積是提高載流能力主要方法。 現(xiàn)階段 SiC 襯底普遍存在缺陷,強(qiáng)行增大芯片面積會導(dǎo)致成品率大

幅下降、價格飆升[5] 。

面對大電流應(yīng)用的需求,為解決這一問題,SiC /Si 混合器件開始出現(xiàn)。 最初是簡單的 SiC Diode / Si IGBT 混合方法,并不能充分發(fā)揮 SiC 的優(yōu)勢,還可能帶來劇烈的開關(guān)振蕩[10] 。 近年來,各國研究人員不斷開展 SiC MOSFET / Si IGBT 混合開關(guān)器件( Hybird Switch,HyS) 的研究[8-29] ,能夠?qū)崿F(xiàn) IGBT 的零電壓開通和關(guān)斷,有效結(jié)合 SiC MOSFET 的低開關(guān)損耗優(yōu)點和 Si IGBT 大載流能力優(yōu)點,各器件損耗比較如圖 1 所示,與純 SiC 器件相比成本也會大幅下降,特別適合用于同時需求大電流、高開關(guān)頻率、高功率密度的車用電機(jī)控制器、大功率無線充電、多電化飛機(jī)和電力電子變壓器等應(yīng)用[7] 。

本文綜述了基于 Si IGBT / SiC MOSFET 的混合開關(guān)器件,分析了相關(guān)的門極驅(qū)動時序、門極驅(qū)動硬件設(shè)計、電流分配優(yōu)化、功率模塊設(shè)計、變頻器設(shè)計和成本分析等設(shè)計要點。

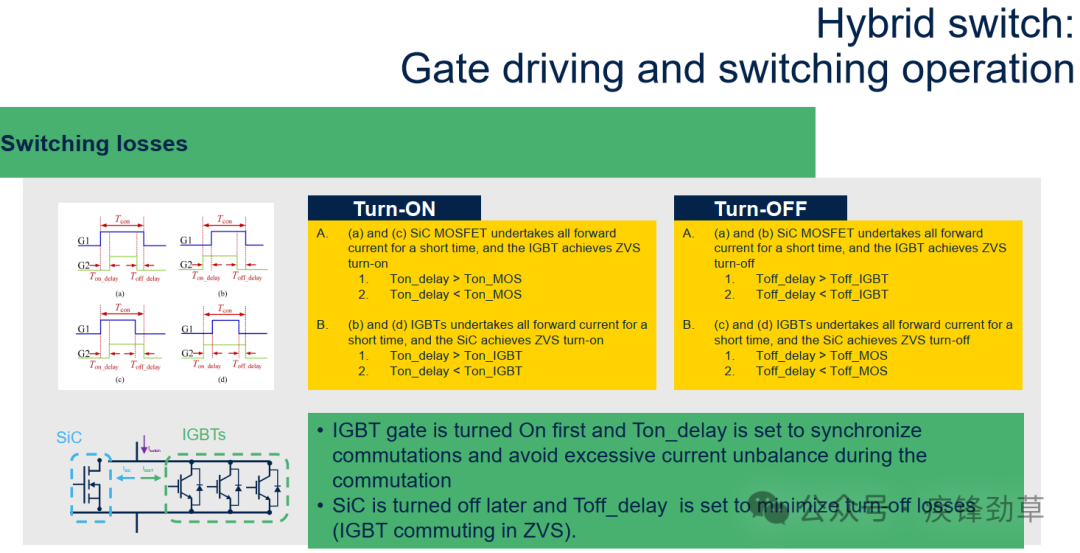

2、 門極驅(qū)動時序

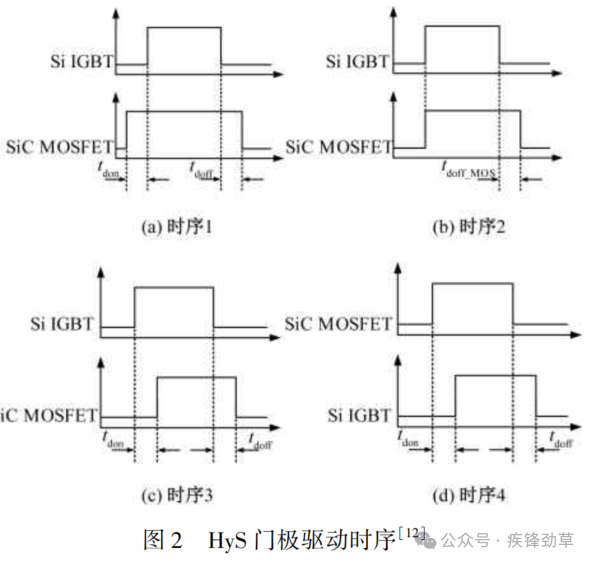

在常規(guī)的混合開關(guān)器件驅(qū)動時序中,為了降低開關(guān)損耗,實現(xiàn) Si IGBT 的零電壓( ZVS) 開通和零電壓關(guān)斷,需要在 Si IGBT 開通前開通 SiC MOSFET,在 Si IGBT 關(guān)斷后關(guān)斷 SiC MOSFET。常見的 4 種門極驅(qū)動時序如圖 2 所示,時序 1是理想器件的驅(qū)動時序,Si IGBT 和 SiC MOSFET 的開關(guān)時序與門極驅(qū)動時序相同。

一般情況下 SiCMOSFET 的門極電容遠(yuǎn)小于 Si IGBT,開關(guān)延時也很小,門極驅(qū)動采用時序 2 可以達(dá)到與時序 1 類似的開關(guān)效果,但可以簡化電路。 如果 HyS 由獨立器件組成,回路中將存在較大的寄生阻抗,Si IGBT 的開關(guān)過程將有較大的延遲,門極驅(qū)動可采用時序 3 實現(xiàn) ZVS,能夠減小 SiC MOSFET 獨立開通載流的時 間。

一些門極硬件設(shè)計不能很好地抑制 Si IGBT 的米勒(Miller)效應(yīng),需要采用時序 4 驅(qū)動防止 Si IGBT 誤導(dǎo)通,這種方法會帶來較大的損耗,有違 HyS的設(shè)計初衷。

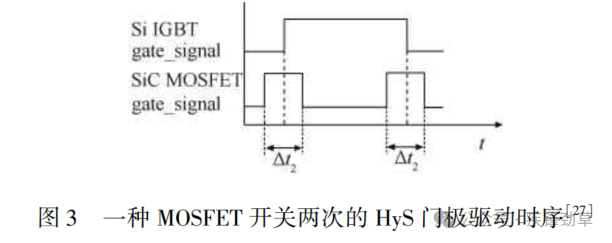

參考文獻(xiàn)[27]給出了另一種驅(qū)動時序,通過降低 SiC / Si 配比來降低成本,如圖 3 所示。 在這種時序中,SiC MOSFET 先于 Si IGBT 開通,在 Si IGBT 開通后立刻關(guān)斷,并于 Si IGBT 關(guān)斷前再次開通,在 Si IGBT 關(guān)斷后再次關(guān)斷。

圖 3 中 SiC MOSFET 只在 HyS 開關(guān)瞬態(tài)時間內(nèi)處于導(dǎo)通狀態(tài),降低了 SiC MOSFET 的導(dǎo)通損耗。然而,這些損耗完全轉(zhuǎn)移到 Si IGBT 上,多出的兩次開關(guān)動作及由此導(dǎo)致的換流過程會引起總損耗的增加,與時序 1 相比其效果較差,還會引起穩(wěn)定性問題 。

3、 門極驅(qū)動硬件設(shè)計

在文獻(xiàn)[8-17]所示的 HyS 關(guān)斷過程中,可以明顯地觀察到米勒效應(yīng)。 這是由 SiC MOSFET 的高速關(guān)斷引起的,較大的 dv / dt 將在已關(guān)斷的 Si IGBT 門極回路上引起較大干擾,感生的米勒電流通過 Si IGBT 門極阻抗出現(xiàn)電壓尖峰,當(dāng)尖峰超過門極電壓閾值時 Si IGBT 會再次導(dǎo)通。

米勒效應(yīng)將影響 Si IGBT 的 ZVS 過程,雖然HyS 的拖尾電流時間短于純 Si IGBT 器件,關(guān)斷時間和關(guān)斷損耗卻遠(yuǎn)大于純 SiC MOSFET 器件。 特別對于由獨立器件組成的 HyS,較大的寄生阻抗將使這一現(xiàn)象更為惡劣,有些研究者使用圖 2 中的時序4,但會帶來較大損耗。

文獻(xiàn)[11] 采用負(fù)電壓來抑制米勒現(xiàn)象,但在HyS 中 Si IGBT 的發(fā)射極和 SiC MOSFET 的源極連在一起。 - 5 V 是常規(guī) SiC MOSFET 產(chǎn)品使用的合理負(fù)壓值,但仍不能夠完全抑制米勒現(xiàn)象。

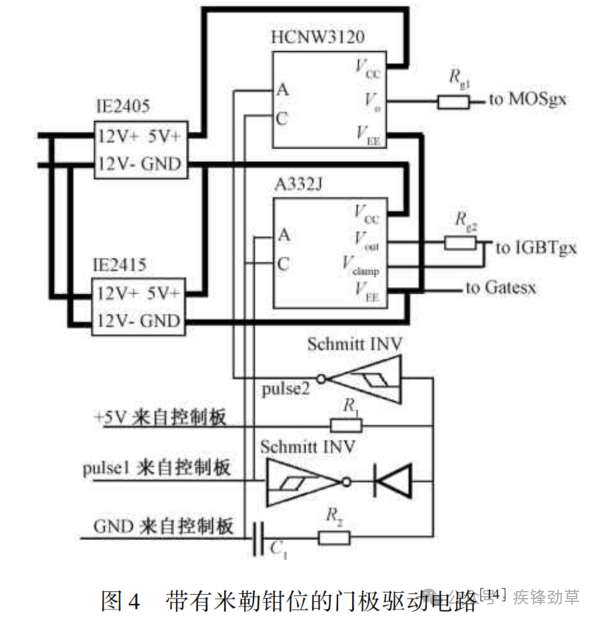

文獻(xiàn)[19]采用帶有米勒鉗位功能的門極驅(qū)動芯片 ACPL-332J 來改進(jìn)硬件電路,實現(xiàn)了較好的效果,帶有米勒鉗位的門極驅(qū)動電路如圖 4 所示。 該芯片內(nèi)部具有米勒鉗位功能,能夠在 Si IGBT 關(guān)斷的情況下降低門極回路阻抗,降低感生電壓峰值,從而抑制米勒現(xiàn)象。

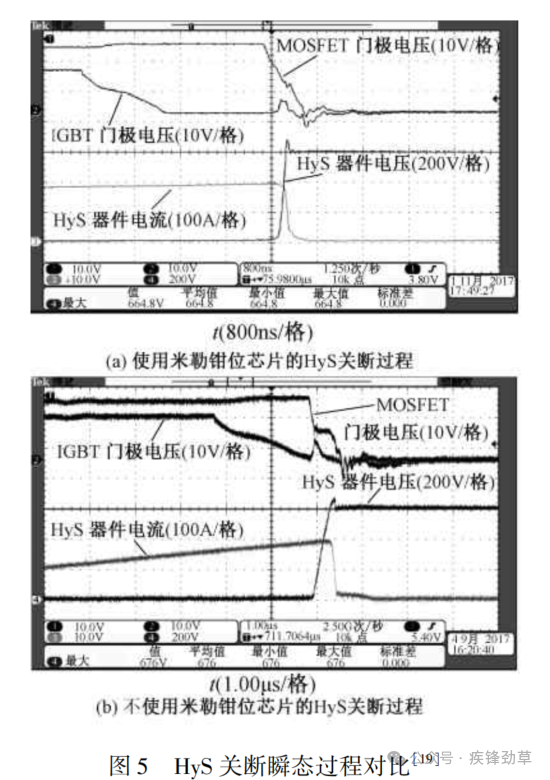

為降低驅(qū)動復(fù)雜度,該電路對于 SiC MOSFET使用簡單的 HCNW3120 進(jìn)行驅(qū)動。 文獻(xiàn)[19 ] 將該電路用于一款 1200V / 200A HyS 模塊的驅(qū)動,在600V / 200A 下的雙脈沖實驗關(guān)斷波形如圖 5 所示。

圖 5 中使用了帶有米勒鉗位的驅(qū)動芯片后,HyS 實現(xiàn)了快速關(guān)斷,沒有明顯的拖尾電流,更接近純 SiC 器件。 與不使用米勒鉗位芯片的驅(qū)動電路相比,其瞬態(tài)特性見表 1:

文獻(xiàn)[11]討論了門極驅(qū)動與器件短路耐量的關(guān)系。 如果降低 MOSFET 的驅(qū)動電壓,HyS 的整體短路耐量將有所改進(jìn),但損耗會大幅增加。

4、 電流分配優(yōu)化和 HyS 模塊設(shè)計

HyS 器件內(nèi)部電流分配優(yōu)化過程中經(jīng)常使用SiC / Si 配比參數(shù),低配比能降低 SiC MOSFET 芯片的載流壓力和散熱壓力,也能降低 HyS 的整體成本。

文獻(xiàn)[18]基于已商業(yè)化的 Si IGBT 和 SiC MOSFET 獨立器件對 1. 2kV 的 HyS 進(jìn)行了較為系統(tǒng)的配比優(yōu)化,得到了 1∶ 4和 1∶ 6的低配比方案。 在優(yōu)化過程中主要比較了器件的結(jié)溫,采用仿真和等效網(wǎng)絡(luò)等方法估算相關(guān)結(jié)溫。 但 50A 的 SiC MOSET 芯片只 能 在 短 時 間 內(nèi) 支 撐 300A 運(yùn) 行, 難 以 超 過500ns,相關(guān)優(yōu)化應(yīng)該注意與門極驅(qū)動的時序結(jié)合。

文獻(xiàn)[14]給出了 HyS 模塊電流分配方案的優(yōu)化過程,該過程評估每種方案的損耗和芯片結(jié)溫。由于 HyS 模塊多使用產(chǎn)品化 Si IGBT 芯片和 SiC MOSFET 芯片,計算并不復(fù)雜。與獨立器件相比,功率模塊可有效降低雜散損耗,也能夠帶來更好的散熱。 特別對于超過 30kW的中、大功率應(yīng)用,在功率模塊內(nèi)部實現(xiàn)多芯片的并聯(lián),其效果要好于通過母排并聯(lián)多個獨立器件。

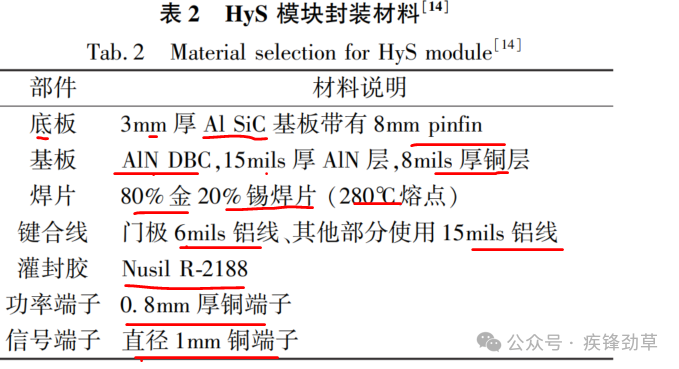

文獻(xiàn)[19]給出了 HyS 功率模塊設(shè)計要點和案例,實現(xiàn)了一款 1200V / 200A 模塊的布局優(yōu)化。 該模塊是橋臂模塊,每個橋臂由 1 個 50A SiC MOSFET 芯片、2 個 100A Si IGBT 芯片、1 個 150A Si Diode 組成。為降低門極回路阻抗,預(yù)留了 kelvin 門極端子。受 Si 芯片限制,該模塊的設(shè)計目標(biāo)為支持芯片結(jié)溫 175°C,首先選取了有關(guān)的封裝材料,具體見表2。 為了進(jìn)一步降低寄生阻抗,該模塊使用超聲波焊接技術(shù)連接 DBC 與功率端子和信號端子。

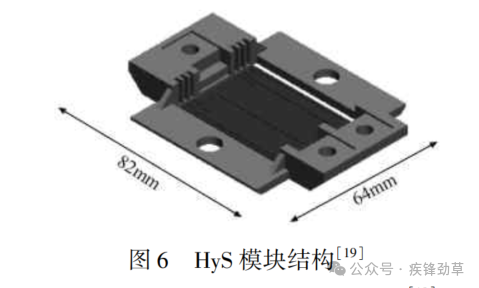

在模塊設(shè)計階段,采用了基于遺傳算法的自動布局優(yōu)化方法,對設(shè)計空間進(jìn)行有向性搜索,充分考慮了寄生電感、并聯(lián)芯片的均流、體積、散熱、門極信號與主回路的解耦。 最終布局的圖案如圖 6 所示,

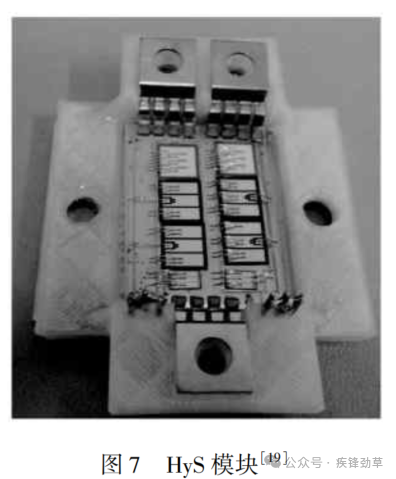

模塊樣件如圖 7 所示。

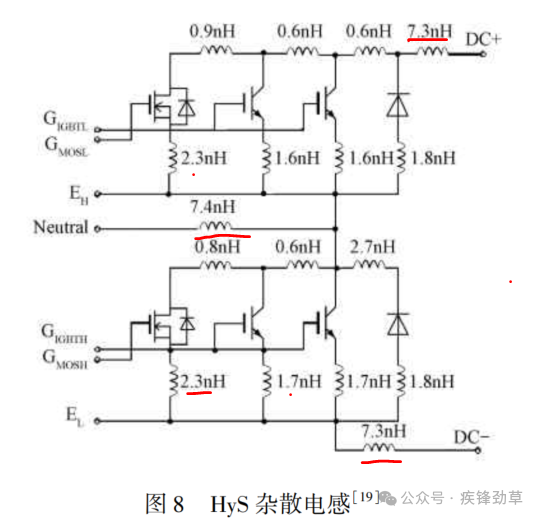

為了驗證布局優(yōu)化結(jié)果,作者采用有限元軟件Q3D 抽取了雜散電感,雜散電感如圖 8 所示,并采用雙脈沖測試的方法檢測了模塊的開關(guān)特性,其結(jié)果與設(shè)計一致。 該模塊用于本文第 5 節(jié)的 3. 4kW無線充電變頻器。

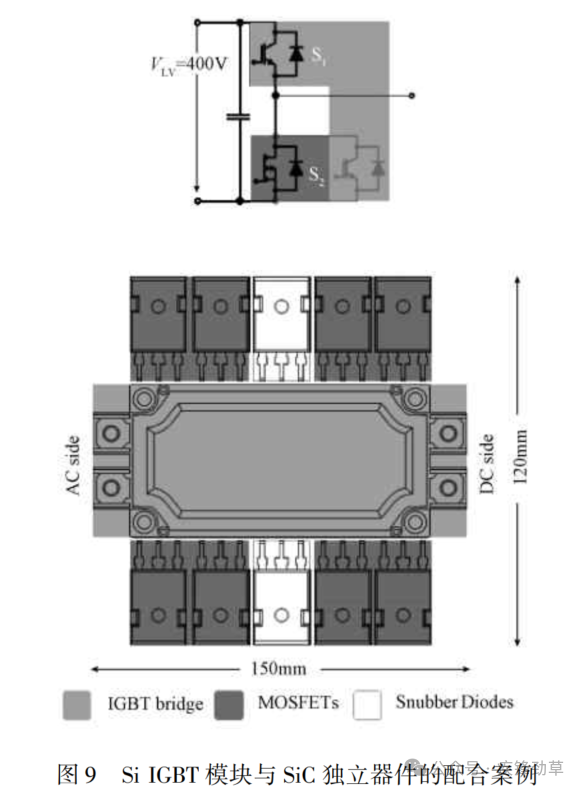

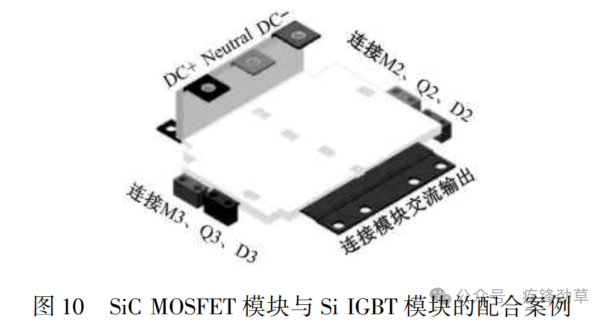

除了設(shè)計開發(fā)混合開關(guān)模塊,還可利用現(xiàn)有的SiC MOSFET 模塊或 Si IGBT 模塊,用母排進(jìn)行器件間的連接[15,29] 。 此方法需要良好的母排設(shè)計才能盡可能降低相關(guān)寄生阻抗,散熱設(shè)計也需兼顧不同器件間的平衡。 圖 9 給出了 IGBT 模塊與 MOSEFT獨立器件的配合案例,圖 10 給出了 SiC MOSFET 模塊與 Si IGBT 模塊的配合案例,具體的母排設(shè)計細(xì)節(jié)和連接方法可以參考文獻(xiàn)[15]和文獻(xiàn)[29]。

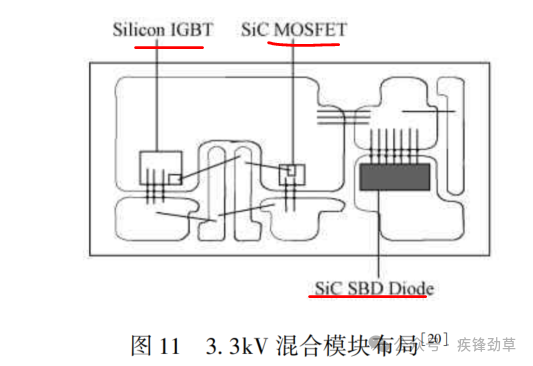

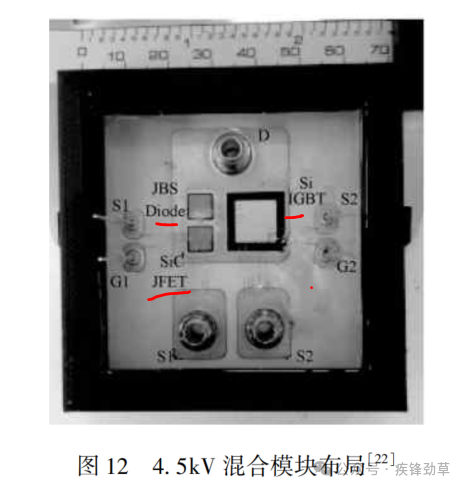

對于高壓 HyS 器件來說功率模塊是必不可少的,高壓模塊的應(yīng)用對象功率普遍較大,還需要考慮局部放電、散熱等一系列問題,很難用獨立器件完成。 圖 11 和圖 12 分別給出了 3. 3kV HyS 模塊和6. 5kV HyS 模塊的布局案例[20,22] 。 這些文獻(xiàn)還驗證了高壓 HyS 的高速開關(guān)特性,有望用于未來電網(wǎng)。 因為高壓芯片的電流普遍較小,普遍需要大數(shù)量芯片并聯(lián)才能達(dá)到所需要的電流,其特性有待進(jìn)一步驗證。

5、 基于 HyS 的變頻器

迄今為止基于 HyS 的變頻器還處于研究階段,尚無小規(guī)模示范應(yīng)用。 受到獨立器件限制,很多文 獻(xiàn)只對 HyS 器件進(jìn)行了雙脈沖實驗。 相對于純 Si

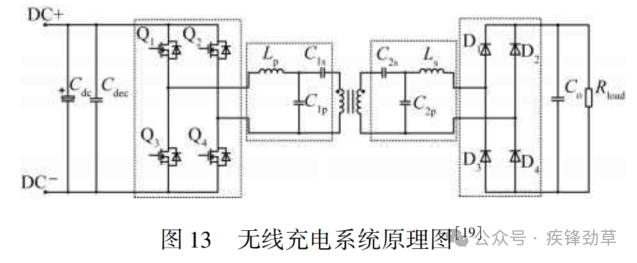

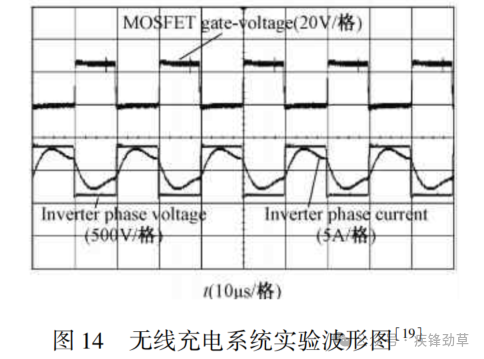

變頻器或純 SiC 變頻器,HyS 變頻器系統(tǒng)復(fù)雜度較高,本節(jié)對相關(guān)文獻(xiàn)工作總結(jié)如下。第一例是 3. 4kW 無線充電用逆變器,如圖 13所示,詳細(xì)的設(shè)計和測試可參考文獻(xiàn)[23]。

該系統(tǒng)使用 2 個 HyS 橋臂模塊實現(xiàn) H 橋拓?fù)?運(yùn)行于 50kHz,峰值功率達(dá)到 3. 4kW,部分波形如圖14 所示。 在測試中 Si IGBT 良好地實現(xiàn)了 ZVS,系統(tǒng)損耗較低。

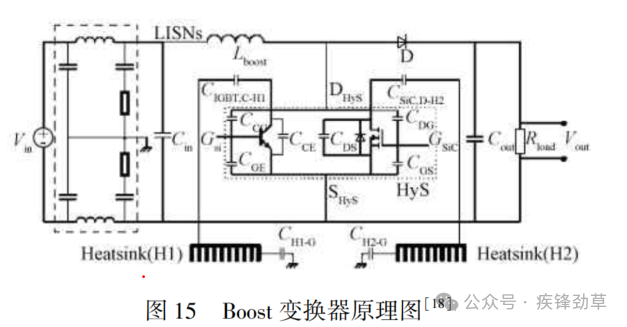

第二例使用獨立器件搭建了 Boost 變頻器[18] ,如圖 15 所示。 該系統(tǒng)使用 650V 的 SiC MOSFET 和 Si IGBT 實現(xiàn)了 1∶ 5的電流配比,運(yùn)行于 20kHz。 該文獻(xiàn) 還對 HyS 變頻器的電磁兼容特性進(jìn)行了測試和分析。

相關(guān)電磁兼容的研究可進(jìn)一步參考文獻(xiàn)[23]。

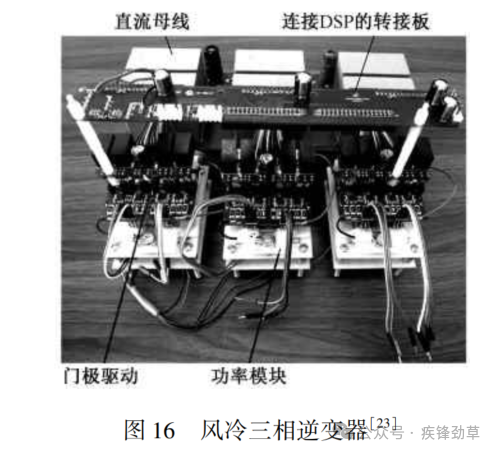

第三例是采用強(qiáng)制風(fēng)冷的三相逆變器,由 3 個HyS 橋臂模塊組成,實現(xiàn)了 30kHz 開關(guān)頻率,功率達(dá)到 5kW[23] ,如圖 16 所示。 在后續(xù)的水冷升級版硬件中,該系統(tǒng)達(dá)到了 15kW。

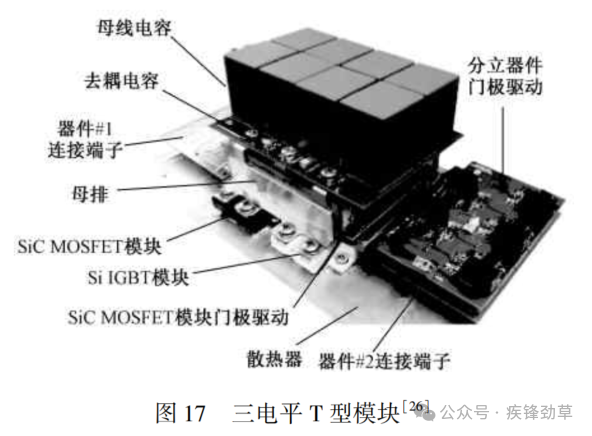

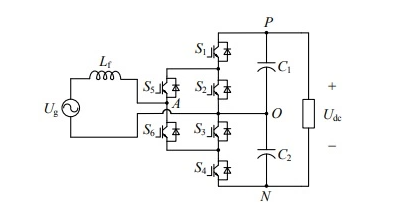

第四例采用了三電平 T 型模塊,如圖 17 所示,由 SiC MOSFET 模塊與 Si IGBT 模塊配合組成HyS,設(shè)計目標(biāo)是 100kW 的變頻器。 文獻(xiàn)[17] 中 對 單 相 器 件 進(jìn) 行 了 測 試, 實 現(xiàn) 了 28kHz 和17. 5kV·A運(yùn)行。

以上幾個 HyS 變頻器都展示了 SiC / Si 混合開關(guān)器件的優(yōu)異特性,在 SiC 器件產(chǎn)品價格降低到接近 Si 器件之前,該類變頻器有一定應(yīng)用前景,特別是對于同時要求較高開關(guān)頻率和中、大輸出功率的應(yīng)用。

6 、HyS 的成本分析

相比于純 SiC 器件,HyS 的最大優(yōu)勢來自成本。這部分?jǐn)?shù)據(jù)比較老了,就刪掉了。

文獻(xiàn)[25] 嘗試使用更低的 SiC / Si 配比,達(dá)到1∶ 6,使 HyS 器件的成本更接近 Si IGBT 器件。 然而這種配比缺乏相關(guān)散熱驗證,需要進(jìn)一步驗證變頻器的性能。

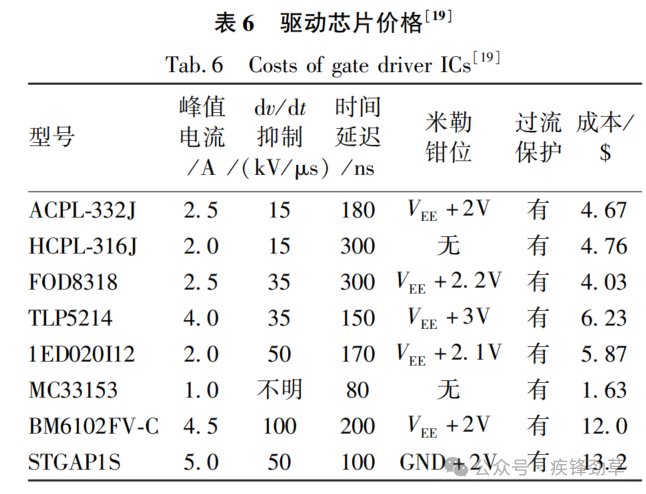

由于 HyS 需要使用更加高性能且復(fù)雜的門極驅(qū)動芯片,在討論 HyS 成本問題的時候應(yīng)該注意包含這一部分。 HyS 所需門極驅(qū)動芯片的特點主要包括大驅(qū)動電流、高 dv / dt 抑制能力、短時間延遲、具有保護(hù)功能、具有米勒鉗位功能等,一些常用驅(qū)動芯片的價格見表 6。

這幾年SiC的價格變化比較大,這篇文章是2018年的,不知道當(dāng)前是個啥進(jìn)展。還下了一些較新的文章,有時間繼續(xù)扒。

-

MOSFET

+關(guān)注

關(guān)注

150文章

8392瀏覽量

219094 -

逆變器

+關(guān)注

關(guān)注

293文章

4871瀏覽量

210330 -

功率器件

+關(guān)注

關(guān)注

42文章

1925瀏覽量

92341 -

SiC

+關(guān)注

關(guān)注

31文章

3189瀏覽量

64603 -

柵極驅(qū)動器

+關(guān)注

關(guān)注

8文章

1060瀏覽量

39563

原文標(biāo)題:Si/SiC混合模塊會是好的選擇嗎?

文章出處:【微信號:芯長征科技,微信公眾號:芯長征科技】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

如何混合Si和SiC器件實現(xiàn)完整SiC MOSFET轉(zhuǎn)換器相同效率的調(diào)制方案

SiC MOSFET 開關(guān)模塊RC緩沖吸收電路的參數(shù)優(yōu)化設(shè)計

為何使用 SiC MOSFET

SiC-MOSFET的應(yīng)用實例

SiC-MOSFET與Si-MOSFET的區(qū)別

Si-MOSFET與IGBT的區(qū)別

搭載SiC-MOSFET和SiC-SBD的功率模塊

SiC-MOSFET有什么優(yōu)點

SiC功率器件概述

SiC功率器件SiC-MOSFET的特點

SiC-MOSFET器件結(jié)構(gòu)和特征

SiC MOSFET的器件演變與技術(shù)優(yōu)勢

對SiC-MOSFET與IGBT的區(qū)別進(jìn)行介紹

Si-IGBT+SiC-MOSFET并聯(lián)混合驅(qū)動逆變器設(shè)計的關(guān)鍵要素

基于Si IGBT/SiC MOSFET的混合開關(guān)器件綜述

基于Si IGBT/SiC MOSFET的混合開關(guān)器件綜述

評論