數(shù)據(jù)延時線(Delay Line)在數(shù)字信號處理中具有廣泛的應(yīng)用,例如FIR濾波器設(shè)計中就會需要用到數(shù)據(jù)延時線。實際上,在絕大部分的Pipeline設(shè)計中都會需要用到數(shù)據(jù)延時。本文介紹一種基于EBR(Embedded Block RAM,Xilinx叫做BRAM,Altera叫做Embedded memory)的數(shù)據(jù)延時的實現(xiàn)方法。

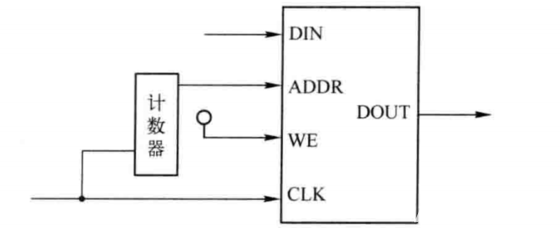

如下圖所示:

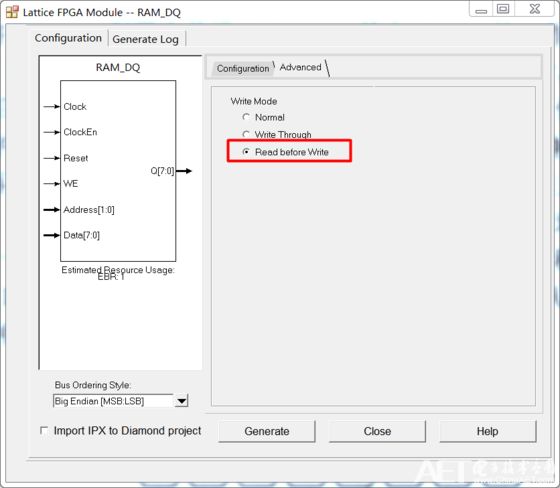

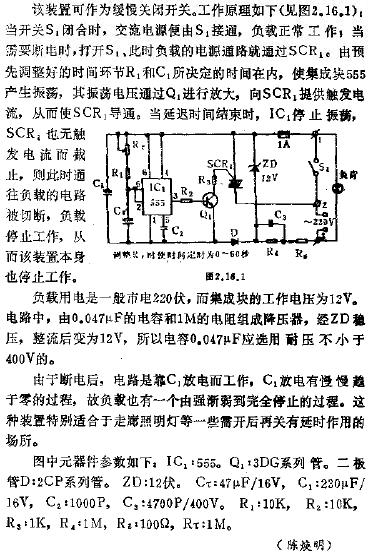

將EBR配置為單端口的RAM(即RAM_DQ),其中,Write Mode配置為Read before write。即同時對同一地址進(jìn)行讀寫操作時,將首先讀取出改地址空間的原有數(shù)據(jù),然后在將新的數(shù)據(jù)寫入到該地址空間中。如下圖所示:

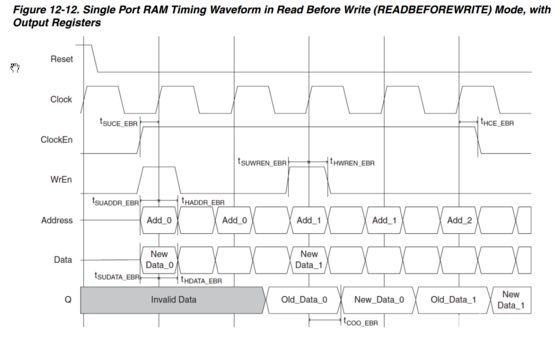

此模式下的波形圖為:

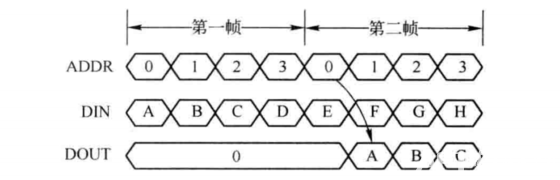

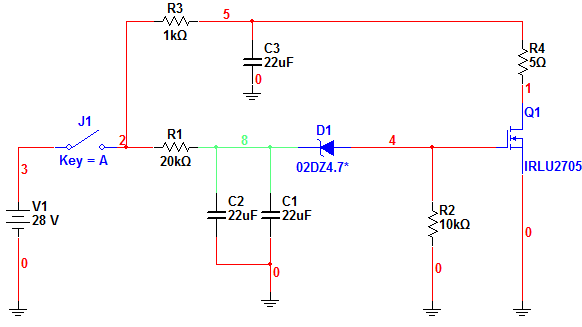

假定計數(shù)器模為4,并將WE信號接高電平,RAM的初始值為0,則相應(yīng)的時序圖如下圖所示:

在第一幀地址內(nèi),從0號地址讀出的數(shù)據(jù)為0,再將數(shù)據(jù)A寫入0號地址中,從1號地址讀出的數(shù)據(jù)為0,再將數(shù)據(jù)B寫入1號地址。類似的,數(shù)據(jù)C和數(shù)據(jù)D分別被寫入到2號地址和3號地址中。在第二幀地址內(nèi),從0號地址讀取出的數(shù)據(jù)即為在第一幀地址內(nèi)寫入的數(shù)據(jù)A,類似的,從1~3號地址中讀出的數(shù)據(jù)分別為B,C和D。由于我們使能了輸出寄存器,所以從輸入端DIN到輸出端DOUT一共有5級時鐘周期的Latency。

-

濾波器

+關(guān)注

關(guān)注

161文章

7860瀏覽量

178931 -

數(shù)字信號

+關(guān)注

關(guān)注

2文章

982瀏覽量

47663

原文標(biāo)題:【精品博文】一種借助EBR實現(xiàn)數(shù)據(jù)延時的方法

文章出處:【微信號:ChinaAET,微信公眾號:電子技術(shù)應(yīng)用ChinaAET】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

請問有沒有一種延時電路能實現(xiàn)兩用?

介紹一種Cortex-M內(nèi)核中的精確延時方法

有什么方法可以實現(xiàn)單片機延時呢

一種systick不進(jìn)中斷的延時方法

一種特殊陣列實現(xiàn)DOA估計的方法

Boost電路的一種軟開關(guān)實現(xiàn)方法

單片機系統(tǒng)實現(xiàn)延時的兩種方法解析

片機實現(xiàn)延時的兩種方法

單片機實現(xiàn)延時的方法

單片機實現(xiàn)延時兩種方法

一種基于EBR的數(shù)據(jù)延時的實現(xiàn)方法

一種基于EBR的數(shù)據(jù)延時的實現(xiàn)方法

評論