FPGA設(shè)計(jì)調(diào)試流程

FPGA開發(fā)是一個(gè)不斷迭代的過程,一般的FPGA設(shè)計(jì)流程一般包含下面幾個(gè)步驟:

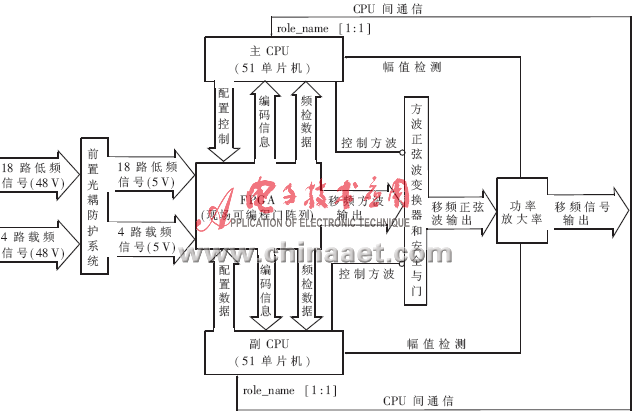

硬件架構(gòu)和算法驗(yàn)證:實(shí)現(xiàn)需要的功能需要哪幾個(gè)模塊,模塊和模塊之間如何進(jìn)行通信和連接;硬件算法是否可行和穩(wěn)定(以圖像處理算法為例,一般可以采用MATLAB進(jìn)行算法驗(yàn)證);

RTL代碼編寫;

硬件調(diào)試與驗(yàn)證:一般這個(gè)過程會(huì)耗費(fèi)大量的時(shí)間,如果沒有一定的經(jīng)驗(yàn)以及技巧,有可能會(huì)使得開發(fā)時(shí)間延長(zhǎng)幾倍,甚至開發(fā)失敗;

調(diào)試,即Debug,有一定開發(fā)經(jīng)驗(yàn)的人一定會(huì)明確這是設(shè)計(jì)中最復(fù)雜最磨人的部分。對(duì)于一個(gè)龐大復(fù)雜的FPGA工程而言,出現(xiàn)問題的概率極大,這時(shí)如果沒有一個(gè)清晰的Debug思路,調(diào)試過程只能是像無頭蒼蠅一樣四處亂撞。在FPGA設(shè)計(jì)中一般的調(diào)試思路如下所示:

?

首先排查硬件問題:在出現(xiàn)問題時(shí),首先懷疑并排除硬件問題。首先檢查開發(fā)板的供電和連接是否正常,是否有電子元件被燒毀,是否出現(xiàn)元件虛焊等問題。確認(rèn)開發(fā)板以及供電沒有問題后,使用例程或者已有的程序或者工程對(duì)出現(xiàn)問題的核心部件進(jìn)行測(cè)試。例如,在讀寫DDR時(shí),如果DDR沒有反應(yīng),可以通過網(wǎng)絡(luò)查找例程,或者使用開發(fā)板官方提供的例程對(duì)DDR讀寫進(jìn)行測(cè)試,確認(rèn)DDR可以正常工作;在讀寫SD卡時(shí),可以嘗試換一張SD卡操作,或者通過將SD卡切換到其他設(shè)備上,確保SD卡沒有損壞等。實(shí)際工程應(yīng)用中,需要靈活選擇測(cè)試和排查方案,但是目的基本都是相同的。

?

其次排查全局信號(hào):確認(rèn)硬件連接沒有問題后,排查全局信號(hào)可能出現(xiàn)的問題。全局信號(hào)一般指接在內(nèi)部所有模塊的信號(hào),例如i_sys_clk和i_sys_rst_n等。需要確保這些信號(hào)正常工作,之后的RTL排查才有意義。

?

最后排查RTL代碼:在確保硬件和全局信號(hào)沒有問題后,再開始排查RTL代碼。在RTL代碼排查中也有一定的順序可以參考,一般可以參考下面的順序:

檢查主從設(shè)備(模塊)之間的握手機(jī)制,或者說檢查主從設(shè)備之間是否正常連接。很多時(shí)候可以參考設(shè)備的官方Datasheet檢查主從模塊之間的初始化指令是否書寫正確。

檢查狀態(tài)跳轉(zhuǎn)是否正常:在初始化過程中,經(jīng)常使用狀態(tài)機(jī)進(jìn)行RTL編程。

檢查讀寫數(shù)據(jù)是否正常:可以設(shè)計(jì)一些“假數(shù)據(jù)”,例如人為規(guī)定的一些有規(guī)律的數(shù)據(jù),檢查這些數(shù)據(jù)在從設(shè)備中的地址是否正常,數(shù)據(jù)是否正確。

檢查執(zhí)行操作的觸發(fā)信號(hào):檢查信號(hào)的Trigger是否正常工作。

總之,RTL調(diào)試是最枯燥的部分,很多時(shí)候需要“抽絲剝繭”、“追本溯源”才能找到問題所在。但是筆者認(rèn)為這恰恰是體現(xiàn)一個(gè)FPGA工程師硬實(shí)力的必要技能和心境。

Vivado ILA IP 的使用

ILA,全稱Integrated Logic Analyzer,是Xilinx FPGA芯片中設(shè)計(jì)的芯片內(nèi)部集成邏輯分析儀。它可以在一定程度上替代外部的傳統(tǒng)邏輯分析儀的作用。ILA通常和VIO(Vritual Input/Output)結(jié)合使用,VIO不僅可以實(shí)時(shí)監(jiān)控內(nèi)部的邏輯信號(hào)和端口信號(hào),還可以充當(dāng)模擬輸入驅(qū)動(dòng)內(nèi)部端口。ILA監(jiān)控內(nèi)部信號(hào)輸出給PC端,而VIO接收PC端的實(shí)時(shí)指令從而給內(nèi)部端口提供輸入信號(hào)。

?

ILA調(diào)試有多種方法,可以直接在代碼中通過原語添加,也可以在原理圖中通過Debug添加,也可以在網(wǎng)絡(luò)列表Netlist中添加。

?

在這里先創(chuàng)建一個(gè)示例工程,使用一個(gè)呼吸燈模塊作為頂層代碼:

module Breath_LED ( input sys_clk, input sys_rst_n, output reg led ); parameter CNT_2US_MAX = 7'd100; parameter CNT_2MS_MAX = 10'd1000; parameter CNT_2S_MAX = 10'd1000; reg [6:0] cnt_2us; // sys_clk = 50MHz, T = 20ns, cnt_2us: 0 ~ 99 reg [9:0] cnt_2ms; reg [9:0] cnt_2s; // cnt_2ms, cnt_2s: 0 ~ 999 reg inc_dec_flag; // 0: increase, 1: decrease // count to 2us always @(posedge sys_clk or negedge sys_rst_n) begin if (!sys_rst_n) cnt_2us <= 7'd0; else if (cnt_2us == (CNT_2US_MAX - 7'd1)) cnt_2us <= 7'd0; else cnt_2us <= cnt_2us + 7'd1; end // count to 2ms by cnt_2us always @(posedge sys_clk or negedge sys_rst_n) begin if (!sys_rst_n) cnt_2ms <= 10'd0; else if ((cnt_2us == (CNT_2US_MAX - 7'd1)) && (cnt_2ms == (CNT_2MS_MAX - 10'd1))) cnt_2ms <= 10'd0; else if (cnt_2us == (CNT_2US_MAX - 7'd1)) cnt_2ms <= cnt_2ms + 10'd1; end // count to 2s by cnt_2ms always @(posedge sys_clk or negedge sys_rst_n) begin if (!sys_rst_n) cnt_2s <= 10'd0; else if ((cnt_2us == (CNT_2US_MAX - 7'd1)) && (cnt_2ms == (CNT_2MS_MAX - 10'd1)) && (cnt_2s == (CNT_2S_MAX - 10'd1))) cnt_2s <= 10'd0; else if ((cnt_2us == (CNT_2US_MAX - 7'd1)) && (cnt_2ms == (CNT_2MS_MAX - 10'd1))) cnt_2s <= cnt_2s + 10'd1; end // inc_dec_flag always @(posedge sys_clk or negedge sys_rst_n) begin if (!sys_rst_n) inc_dec_flag <= 1'b0; else if ((cnt_2us == (CNT_2US_MAX - 7'd1)) && (cnt_2ms == (CNT_2MS_MAX - 10'd1)) && (cnt_2s == (CNT_2S_MAX - 10'd1))) inc_dec_flag <= ~inc_dec_flag; else inc_dec_flag <= inc_dec_flag; end // led PWM configuration always @(posedge sys_clk or negedge sys_rst_n) begin if (!sys_rst_n) led <= 1'b0; else if ((inc_dec_flag == 1'b0) && (cnt_2ms <= cnt_2s)) // increase led <= 1'b1; else if ((inc_dec_flag == 1'b1) && (cnt_2ms >= cnt_2s)) // decrease led <= 1'b1; else led <= 1'b0; end endmodule

IP核配置

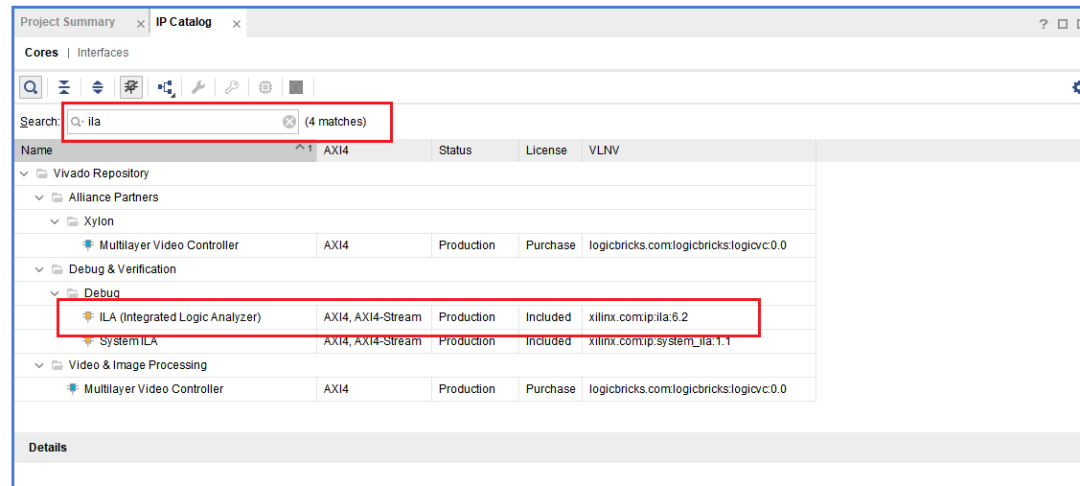

在IP Catalog中搜索ILA即可找到ILA IP核,雙擊之后就會(huì)跳出配置界面。

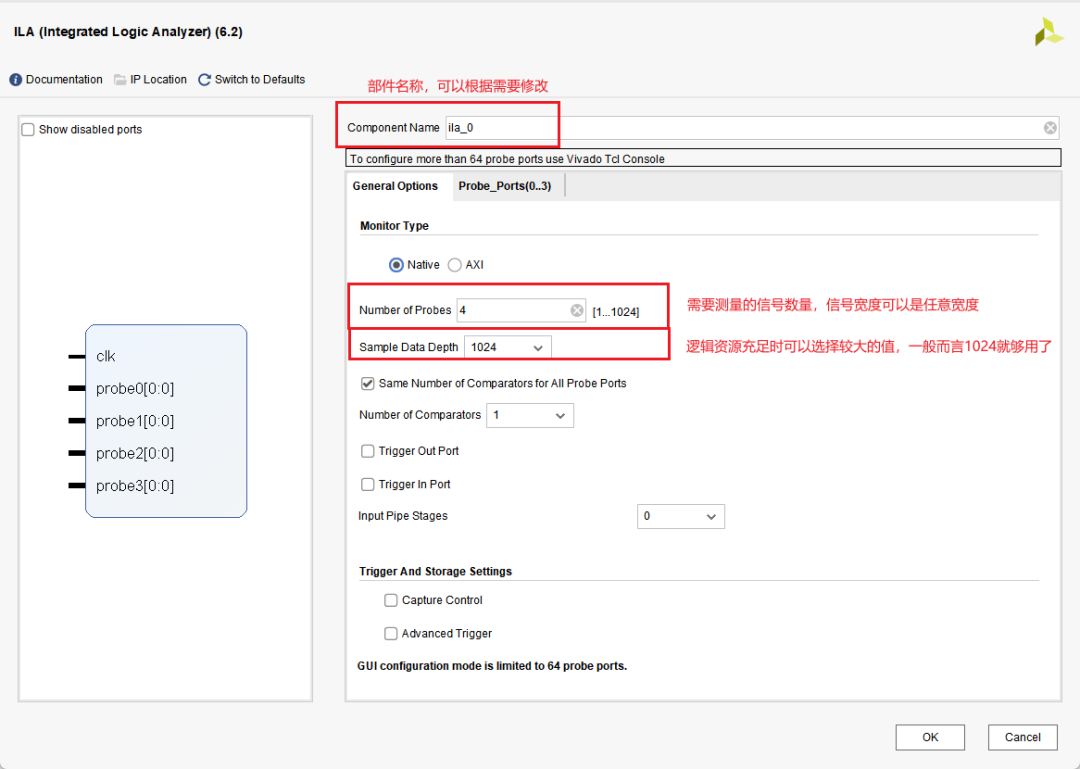

設(shè)置部件名稱、探針數(shù)量(需要測(cè)量信號(hào)的數(shù)量)和采樣深度。clk信號(hào)一般是系統(tǒng)的時(shí)鐘信號(hào),ILA IP會(huì)在每個(gè)clk上升沿(或下降沿、具體有待考量)采一次對(duì)應(yīng)信號(hào)的數(shù)據(jù),直到采信號(hào)的次數(shù)達(dá)到采樣深度為止。

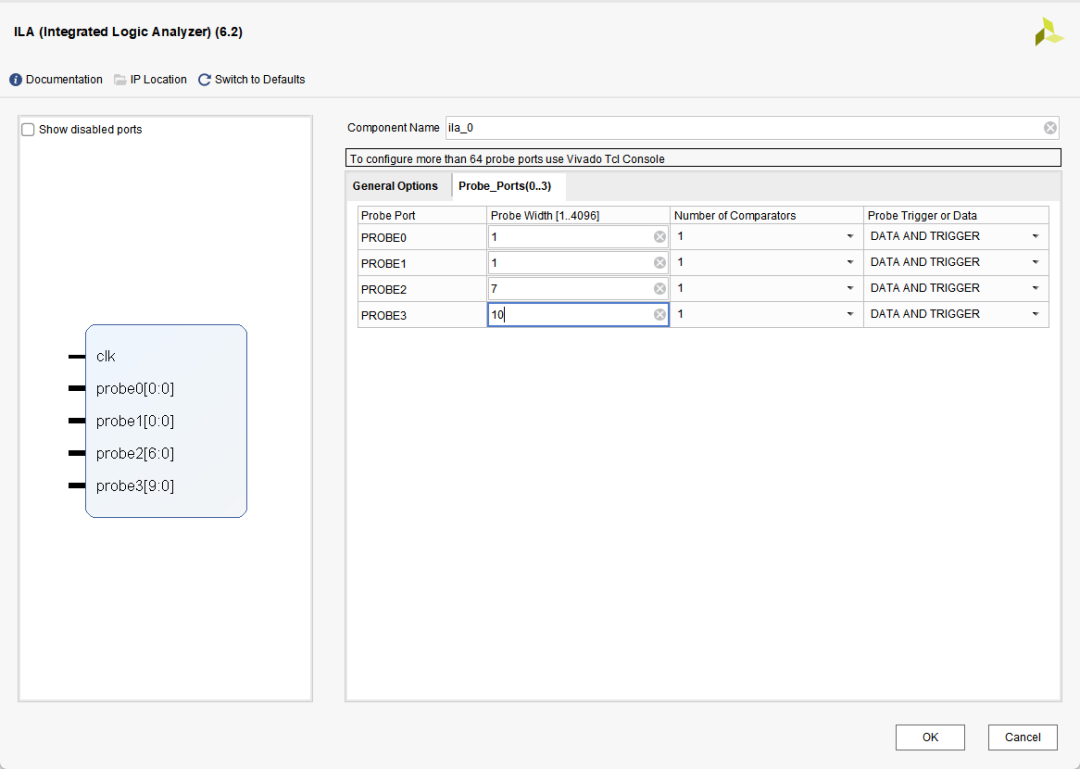

在這里,假設(shè)代碼出現(xiàn)了問題,我們需要檢測(cè)sys_clk、led、sys_rst_n、cnt_2us、cnt_2ms四個(gè)信號(hào)。四個(gè)信號(hào)的寬度分別為1,1,7,10。

完成設(shè)置后,點(diǎn)擊OK,出現(xiàn)下面界面。如果綜合選項(xiàng)選擇Global,代碼會(huì)在每次綜合時(shí)都對(duì)ILA進(jìn)行綜合;如果選擇OutofconextperIP(OOC模式),代碼只會(huì)在ILA設(shè)置發(fā)生改變時(shí)對(duì)ILA進(jìn)行綜合。一般選擇后者即可,可以加快綜合速度。

-

FPGA

+關(guān)注

關(guān)注

1645文章

22050瀏覽量

618702 -

Vivado

+關(guān)注

關(guān)注

19文章

835瀏覽量

68807 -

硬件調(diào)試

+關(guān)注

關(guān)注

1文章

10瀏覽量

10835 -

ILA

+關(guān)注

關(guān)注

0文章

6瀏覽量

3754

原文標(biāo)題:使用ILA進(jìn)行FPGA硬件調(diào)試

文章出處:【微信號(hào):gh_9d70b445f494,微信公眾號(hào):FPGA設(shè)計(jì)論壇】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

FPGA基本開發(fā)流程概述

FPGA基本開發(fā)設(shè)計(jì)流程

FPGA的設(shè)計(jì)流程是怎樣的

FPGA調(diào)試工具-chipscope

FPGA硬件系統(tǒng)的調(diào)試方法

加速FPGA系統(tǒng)實(shí)時(shí)調(diào)試技術(shù)

FPGA設(shè)計(jì)流程指南

對(duì)FPGA進(jìn)行測(cè)試和調(diào)試有哪些辦法?

關(guān)于FPGA它的開發(fā)流程是怎樣的

FPGA的開發(fā)流程以及它的適用場(chǎng)景

FPGA設(shè)計(jì)與調(diào)試教程說明

FPGA基礎(chǔ)知識(shí)----第二章 FPGA 開發(fā)流程

FPGA入門之FPGA 開發(fā)流程

FPGA設(shè)計(jì)流程

FPGA設(shè)計(jì)調(diào)試流程

FPGA設(shè)計(jì)調(diào)試流程

評(píng)論