PCIe7.0的測(cè)試方案

隨著 PCIe 6.0 標(biāo)準(zhǔn)剛剛進(jìn)入市場(chǎng),PCI-SIG 組織已著手推動(dòng)下一代標(biāo)準(zhǔn)——PCIe 7.0,預(yù)計(jì)將在 2025 年正式發(fā)布,持該標(biāo)準(zhǔn)的設(shè)備預(yù)計(jì)將在 2026 年問(wèn)世,而大規(guī)模商用應(yīng)用可能要到 2028-2029年才會(huì)普及。盡管消費(fèi)級(jí)市場(chǎng)短期內(nèi)不會(huì)廣泛采用 PCIe 7.0,但對(duì)于AI 計(jì)算、高性能數(shù)據(jù)中心和云計(jì)算而言,它將成為未來(lái)計(jì)算架構(gòu)的關(guān)鍵推動(dòng)力。

作為新一代高速互連協(xié)議,PCIe 7.0 在數(shù)據(jù)速率、能效優(yōu)化和新型傳輸技術(shù)等方面實(shí)現(xiàn)了重大突破,特別是引入了光學(xué)通信連接,這將徹底改變計(jì)算基礎(chǔ)架構(gòu)。

PCIe 7.0 的主要特性

1. 帶寬翻倍

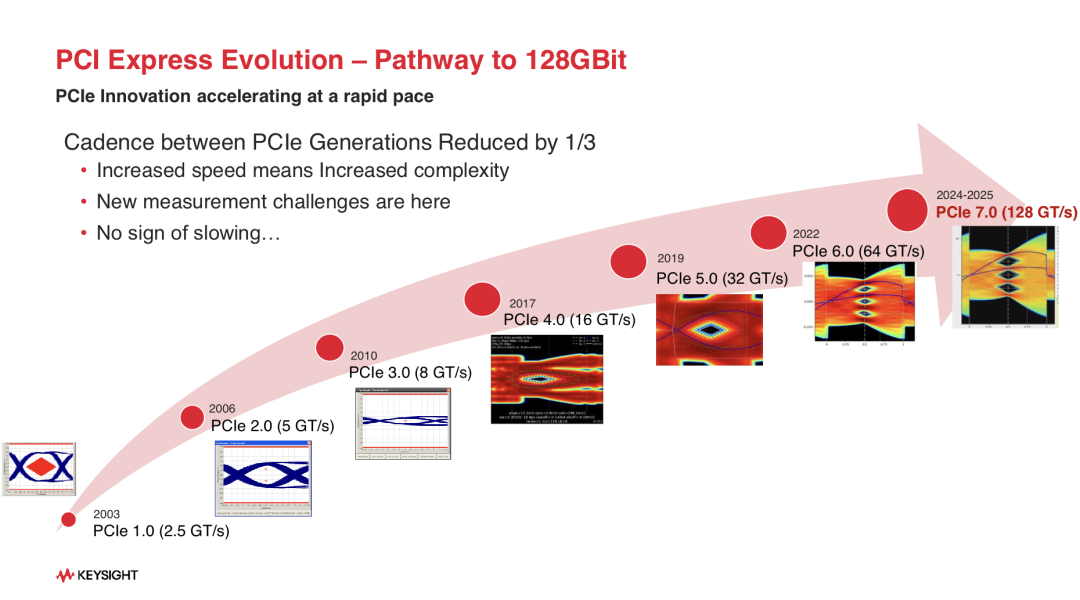

PCIe 7.0 的核心目標(biāo)是將數(shù)據(jù)傳輸速率提升至 128 GT/s,相比 PCIe 6.0 實(shí)現(xiàn)翻倍,相當(dāng)于 PCIe 5.0 的四倍。在 x16 通道配置下,理論雙向帶寬可達(dá) 512 GB/s,顯著提升數(shù)據(jù)吞吐能力。這一突破對(duì)于 AI、高性能計(jì)算(HPC)等需要超高速數(shù)據(jù)交換的應(yīng)用至關(guān)重要,有助于緩解數(shù)據(jù)傳輸瓶頸。

2. PAM4 信號(hào)編碼

PCIe 7.0 繼承了 PCIe 6.0 引入的 PAM4(四級(jí)脈沖幅度調(diào)制)技術(shù),相較于傳統(tǒng)的 NRZ(二進(jìn)制非歸零編碼),PAM4 在每個(gè)時(shí)鐘周期內(nèi)傳輸 2 位數(shù)據(jù),無(wú)需大幅提高信號(hào)頻率即可提升數(shù)據(jù)傳輸速率。這種編碼方式有效提高信號(hào)效率,同時(shí)優(yōu)化通道利用率。

3. 低延遲與高可靠性

PCIe 7.0 在提升帶寬的同時(shí),進(jìn)一步優(yōu)化數(shù)據(jù)傳輸延遲和可靠性,確保在高負(fù)載環(huán)境下依然能夠提供穩(wěn)定的傳輸體驗(yàn)。這對(duì)實(shí)時(shí)計(jì)算、云計(jì)算、自動(dòng)駕駛等對(duì)時(shí)延敏感的應(yīng)用尤為關(guān)鍵。

4. 能效優(yōu)化

在提供更高性能的同時(shí),PCIe 7.0 也注重功耗控制和能效優(yōu)化。盡管更高的傳輸速率可能會(huì)增加功耗,但單位傳輸效率(性能/功耗比)預(yù)計(jì)將顯著提升。這對(duì)于數(shù)據(jù)中心、邊緣計(jì)算等大規(guī)模部署場(chǎng)景有助于降低運(yùn)營(yíng)成本,并減少碳排放。

5. 向后兼容

PCIe 7.0 保持了與所有前代 PCIe 版本的向后兼容性,無(wú)論是舊設(shè)備插入 PCIe 7.0 插槽,還是 PCIe 7.0 設(shè)備連接至早期版本插槽,系統(tǒng)都會(huì)自動(dòng)協(xié)商雙方支持的最高速率,確保平穩(wěn)升級(jí),最大程度保護(hù)用戶投資。

6. 通道優(yōu)化與信號(hào)完整性增強(qiáng)

面對(duì)更高的傳輸頻率,PCIe 7.0 對(duì)信號(hào)完整性和通道設(shè)計(jì)進(jìn)行了深度優(yōu)化,包括改進(jìn)信號(hào)路徑設(shè)計(jì)、降低噪聲、增強(qiáng)誤碼率(BER)控制,以確保在更遠(yuǎn)傳輸距離下仍能保持穩(wěn)定的數(shù)據(jù)傳輸。

PCIe 7.0 的推出標(biāo)志著數(shù)據(jù)傳輸技術(shù)的重大突破,同時(shí)也是對(duì)未來(lái)計(jì)算需求的前瞻性布局。通過(guò)大幅提升帶寬、降低延遲、優(yōu)化能效,PCIe 7.0 為 AI、高性能計(jì)算(HPC)、數(shù)據(jù)中心等關(guān)鍵領(lǐng)域的持續(xù)發(fā)展提供了強(qiáng)有力的支撐。

盡管消費(fèi)級(jí)市場(chǎng)的普及可能仍需時(shí)日,但 PCIe 7.0 在服務(wù)器、數(shù)據(jù)中心等高性能應(yīng)用領(lǐng)域的前景毋庸置疑。隨著光纖互連等前沿技術(shù)的進(jìn)步,PCIe 7.0 有望突破傳統(tǒng)銅纜的物理限制,推動(dòng)計(jì)算與互連技術(shù)邁向新高度。同時(shí),它確保了 PCIe 生態(tài)系統(tǒng)的穩(wěn)定演進(jìn),避免市場(chǎng)碎片化,并為未來(lái)更高速互連技術(shù)的發(fā)展奠定堅(jiān)實(shí)基礎(chǔ)。

近期,是德科技也與各廠商聯(lián)合展出了基于PCIe 7.0的測(cè)試方案預(yù)研,如需了解更多有關(guān) PCIe 7.0的解決方案,請(qǐng)點(diǎn)擊鏈接:PCIe 7.0 互連— PCIe的盡頭會(huì)是光嗎?

PCIe6.0的測(cè)試方案

在數(shù)據(jù)密集型計(jì)算和人工智能(AI)快速發(fā)展的推動(dòng)下,計(jì)算機(jī)互連技術(shù)正經(jīng)歷著前所未有的變革。隨著標(biāo)準(zhǔn)的確立和技術(shù)的成熟,PCIe 6.0 已經(jīng)在全球范圍內(nèi)進(jìn)入商業(yè)化落地階段。2022年1月,PCI-SIG 組織正式發(fā)布了 PCI Express 6.0(PCIe 6.0)標(biāo)準(zhǔn),這次升級(jí)堪稱該技術(shù)自誕生以來(lái)變化最大的一次。

相較于前幾代標(biāo)準(zhǔn),PCIe 6.0 不僅繼續(xù)提升帶寬,還在底層架構(gòu)和功能特性上進(jìn)行了革命性改進(jìn),使其能夠滿足未來(lái)高性能計(jì)算、數(shù)據(jù)中心、人工智能(AI)、汽車、物聯(lián)網(wǎng)(IoT)等領(lǐng)域的需求。

圖 1:PCIe 標(biāo)準(zhǔn)的發(fā)展

PCIe7.0 正在向高達(dá) 128GT/s 和 PAM4 調(diào)制的速度發(fā)展

PCIe 6.0的帶寬是 PCIe 5.0 的兩倍,達(dá)到 1024 Gb/s,最大通道數(shù)仍為 16。每個(gè)引腳的數(shù)據(jù)傳輸速率將從 PCIe 5.0 的 32 GT/s 提高到 64 GT/s。從 NRZ 到 PAM4 信號(hào)的轉(zhuǎn)變帶來(lái)了新的挑戰(zhàn)。PCIe 6.0 還向后兼容前幾代 PCIe 產(chǎn)品。PCIe 技術(shù)已部署在高性能計(jì)算、超大規(guī)模數(shù)據(jù)中心基礎(chǔ)設(shè)施、人工智能系統(tǒng)、臺(tái)式機(jī)計(jì)算、汽車應(yīng)用和移動(dòng)設(shè)備等各種產(chǎn)品中。

PCIe 6.0 采用 PAM4 信號(hào)編碼,使數(shù)據(jù)傳輸速率達(dá)到 64 GT/s,同時(shí)在保持向下兼容的前提下實(shí)現(xiàn)了更高帶寬。然而,這也給發(fā)射機(jī)測(cè)試帶來(lái)了全新的難題,尤其是在信號(hào)完整性和噪聲管理方面。

今天我們將帶您深入了解 PCIe 6.0發(fā)射機(jī)合規(guī)性測(cè)試的關(guān)鍵挑戰(zhàn)以及 Keysight 如何通過(guò)領(lǐng)先技術(shù)和自動(dòng)化解決方案為工程師保駕護(hù)航。

PCIe 6.0 發(fā)射機(jī)測(cè)試(TX)的挑戰(zhàn)

PAM4 信號(hào)編碼帶來(lái)的噪聲問(wèn)題

相比傳統(tǒng)的 NRZ 信號(hào),PAM4 編碼固有地引入額外約 9 dB 的信噪比下降,這要求測(cè)試儀器必須具有極低的噪聲底和高精度測(cè)量能力。

高速信號(hào)傳輸中的通道損耗

隨著數(shù)據(jù)速率提升至 64 GT/s,高頻信號(hào)在傳輸過(guò)程中會(huì)遭受更嚴(yán)重的通道損耗和衰減,測(cè)試時(shí)需要準(zhǔn)確捕捉并分析信號(hào)衰減與失真情況。

多速率測(cè)試要求

PCIe 6.0 不僅要求驗(yàn)證最高速率下的性能,還需要在 64、32、16、8、5、2.5 GT/s 等多個(gè)速率下進(jìn)行測(cè)試,確保不同場(chǎng)景下的發(fā)射機(jī)性能均符合規(guī)范。

硅級(jí)與系統(tǒng)級(jí)驗(yàn)證難度

測(cè)試既要關(guān)注芯片內(nèi)部(硅級(jí))的信號(hào)質(zhì)量,又要驗(yàn)證整機(jī)系統(tǒng)在實(shí)際工作環(huán)境下的互聯(lián)性能,這就需要不同層次的測(cè)試方案協(xié)同工作。

這些挑戰(zhàn)促使測(cè)試設(shè)備必須具備高帶寬、低噪聲和自動(dòng)化測(cè)試功能,以確保 PCIe 6.0 發(fā)射機(jī)能夠精確、穩(wěn)定地運(yùn)行并順利通過(guò) PCI-SIG 官方認(rèn)證。

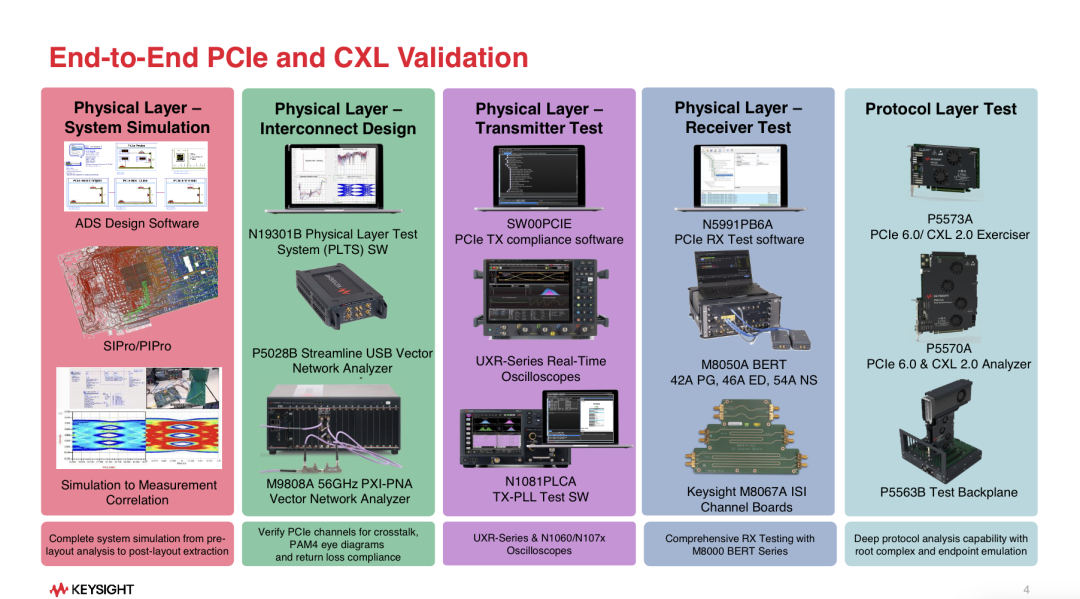

Keysight 的測(cè)試解決方案

Keysight 提供了一整套覆蓋從系統(tǒng)仿真到協(xié)議分析的 PCIe 6.0 到 PCIe 7.0測(cè)試方案,其中包括針對(duì)PCIe 發(fā)射機(jī)合規(guī)性測(cè)試的關(guān)鍵技術(shù)。

圖2:是德科技PCIe解決方案

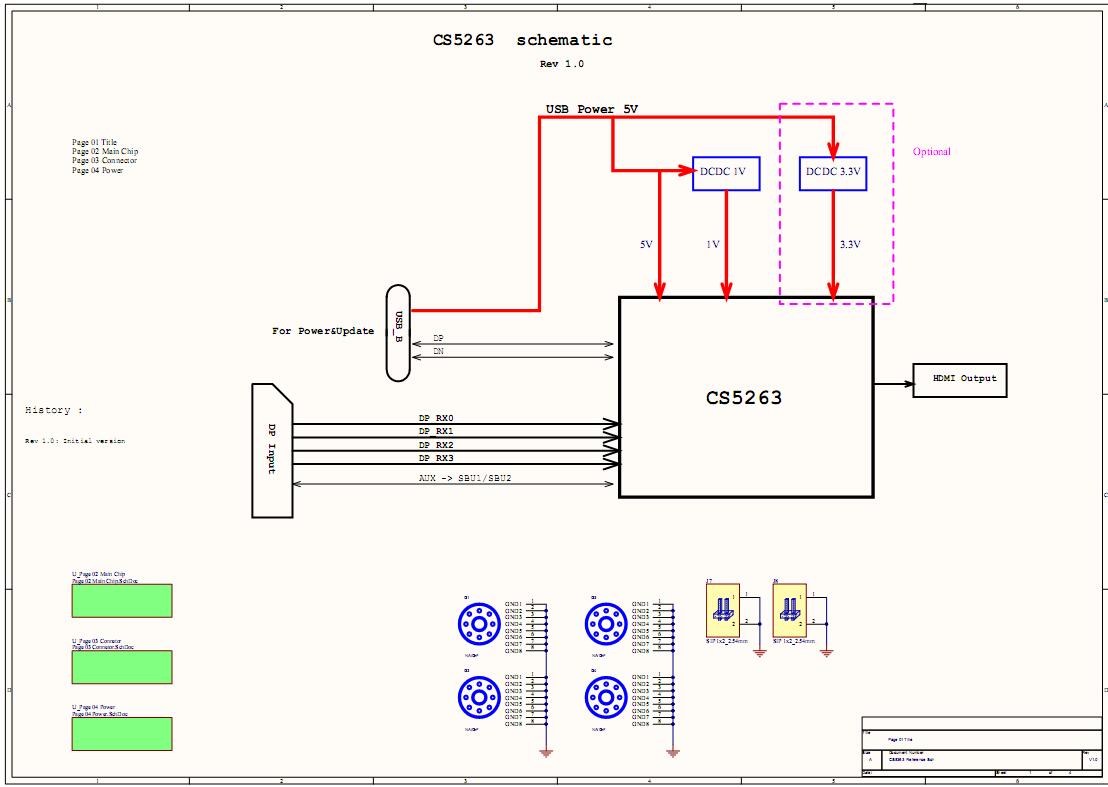

對(duì) PCIe 6.0 器件進(jìn)行發(fā)射機(jī)合規(guī)性測(cè)試,需要使用示波器測(cè)量被測(cè)器件(DUT)發(fā)送的、數(shù)據(jù)速率高達(dá) 64 GT/s 的 PAM4 信號(hào)。研發(fā)工程師需要使用大帶寬示波器執(zhí)行物理層測(cè)試、數(shù)據(jù)鏈路層測(cè)試和通用互操作性測(cè)試,以確保發(fā)射機(jī)達(dá)到 PCI-SIG 認(rèn)可的合規(guī)性。

圖 3:PCIe 6.0 發(fā)射端(TX)一致性測(cè)試解決方案

Keysight PCIe 6.0 發(fā)射機(jī)合規(guī)性測(cè)試解決方案包括 Keysight PCI Express 驗(yàn)證許可證套件、先進(jìn)信號(hào)完整性分析軟件、抖動(dòng)和噪聲分析軟件,以及脈沖幅度調(diào)制分析軟件。這些軟件均在大帶寬的 Keysight UXR 系列示波器上運(yùn)行。工程師需要使用一臺(tái)帶寬 > 50 GHz、采樣率不低于 256 GSa/s 的示波器,以便測(cè)試 64 GT/s 信號(hào)。開(kāi)發(fā)人員可以借助這些工具自動(dòng)對(duì) PCIe 6.0 器件進(jìn)行合規(guī)性測(cè)試,通過(guò)分析器件發(fā)送的 PAM4 噪聲和抖動(dòng)性能,從而準(zhǔn)確測(cè)量被測(cè)器件發(fā)送的信號(hào),確認(rèn)其符合 PCI-SIG 標(biāo)準(zhǔn)。

關(guān)于是德科技

是德科技(NYSE:KEYS)啟迪并賦能創(chuàng)新者,助力他們將改變世界的技術(shù)帶入生活。作為一家標(biāo)準(zhǔn)普爾 500 指數(shù)公司,我們提供先進(jìn)的設(shè)計(jì)、仿真和測(cè)試解決方案,旨在幫助工程師在整個(gè)產(chǎn)品生命周期中更快地完成開(kāi)發(fā)和部署,同時(shí)控制好風(fēng)險(xiǎn)。我們的客戶遍及全球通信、工業(yè)自動(dòng)化、航空航天與國(guó)防、汽車、半導(dǎo)體和通用電子等市場(chǎng)。我們與客戶攜手,加速創(chuàng)新,創(chuàng)造一個(gè)安全互聯(lián)的世界。

-

帶寬

+關(guān)注

關(guān)注

3文章

992瀏覽量

41839 -

發(fā)射機(jī)

+關(guān)注

關(guān)注

7文章

513瀏覽量

48472 -

PCIe

+關(guān)注

關(guān)注

16文章

1327瀏覽量

84731 -

發(fā)射端

+關(guān)注

關(guān)注

0文章

49瀏覽量

8419 -

是德科技

+關(guān)注

關(guān)注

21文章

984瀏覽量

83270

原文標(biāo)題:Solution Talks | 如何測(cè)試 PCIe? 6.0 / 7.0的發(fā)射端(TX)一致性

文章出處:【微信號(hào):是德科技KEYSIGHT,微信公眾號(hào):是德科技KEYSIGHT】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

串行ATA測(cè)試解決方案

新應(yīng)用 | 橫掃第四代串行測(cè)試(之二)

大功率發(fā)射機(jī)的水冷散熱解決方案

執(zhí)行802.11克發(fā)射機(jī)測(cè)量應(yīng)用指南

羅德與施瓦茨 SFE100 回收 測(cè)試發(fā)射機(jī)

多標(biāo)準(zhǔn)無(wú)線電基站發(fā)射機(jī)測(cè)試

是德科技推出全新的發(fā)射機(jī)(Tx)和接收機(jī)(Rx)綜合測(cè)試解決方案

泰克提供業(yè)界首創(chuàng)的 PCIe 6.0 測(cè)試解決方案

是德科技發(fā)布端到端PCIe5.0/6.0測(cè)試解決方案

是德科技發(fā)布新款端到端的PCIe5.0/6.0測(cè)試解決方案

CS5263高性能HDMI 2.0發(fā)射機(jī)概述及特性

是德科技PCIe 6.0發(fā)射機(jī)合規(guī)性測(cè)試解決方案

是德科技PCIe 6.0發(fā)射機(jī)合規(guī)性測(cè)試解決方案

評(píng)論