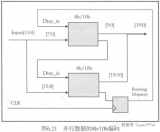

為了提高串行數(shù)據(jù)傳輸?shù)目煽啃裕F(xiàn)在很多更高速率的數(shù)字接口采用的是對(duì)數(shù)據(jù)進(jìn)行編碼后再做并串轉(zhuǎn)換的方式。編碼的方式有很多,如8b/9b編碼、8b/10b編碼、64b/66b編碼、128b/130b編碼等,下面我們以最流行的ANSI 8b/10b編碼為例進(jìn)行一下介紹。

在ANSI 8b/10b編碼方式中,8比特的數(shù)據(jù)先通過(guò)相應(yīng)的編碼規(guī)則轉(zhuǎn)換成10比特的數(shù)據(jù),然后再進(jìn)行并串轉(zhuǎn)換;接收端收到信號(hào)后先把串行數(shù)據(jù)進(jìn)行串并轉(zhuǎn)換得到10比特的數(shù)據(jù),然后再通過(guò)10比特到8比特的解碼得到原始傳輸?shù)?比特?cái)?shù)據(jù)。因此,如果發(fā)送端并行側(cè)的數(shù)據(jù)速率是8bit*100Mb/s,通過(guò)8b/10b編碼和并串轉(zhuǎn)換后的串行側(cè)的數(shù)據(jù)速率就是1bit*1Gb/s。8b/10b編碼方法最早由IBM發(fā)明,后來(lái)成為ANSI標(biāo)準(zhǔn)的一部分(ANSI X3.230-1994, clause 11),并在通信和計(jì)算機(jī)總線上廣泛應(yīng)用。

數(shù)據(jù)經(jīng)過(guò)8b/10b編碼后有幾個(gè)最大的好處:

有足夠多的跳變沿,可以從數(shù)據(jù)里進(jìn)行時(shí)鐘恢復(fù)。正常傳輸?shù)臄?shù)據(jù)里可能會(huì)有比較長(zhǎng)的連續(xù)的0或者連續(xù)的1,而進(jìn)行完8b/10b編碼后,其編碼規(guī)則保證了編碼后的數(shù)據(jù)流里不會(huì)出現(xiàn)超過(guò)5個(gè)的連續(xù)的0或1,信號(hào)里會(huì)出現(xiàn)足夠多的跳變沿,因此可以采樣嵌入式的時(shí)鐘方式,即接收端可以從數(shù)據(jù)流里用PLL電路直接恢復(fù)時(shí)鐘,不需要專門的時(shí)鐘傳輸通道。

直流平衡,可以采用AC耦合方式。經(jīng)過(guò)編碼后數(shù)據(jù)里不會(huì)出現(xiàn)連續(xù)的0或者1了,但是還是有可能在某個(gè)時(shí)間段內(nèi)0或者1的數(shù)量偏多一些。從上面的編碼表中我們可以看到同一個(gè)Byte對(duì)應(yīng)有正、負(fù)兩組10bit的編碼,一個(gè)編碼里1的數(shù)量多一些,另一個(gè)編碼里0的數(shù)量多一些。數(shù)據(jù)在對(duì)當(dāng)前的Byte進(jìn)行8b/10b編碼傳輸時(shí),會(huì)根據(jù)前面歷史傳輸?shù)臄?shù)據(jù)中正負(fù)bit的數(shù)量來(lái)選擇使用哪一組編碼,從而可以保證總線上正負(fù)bit的數(shù)量在任何時(shí)刻基本都是平衡的,也就是直流點(diǎn)不會(huì)發(fā)生大的變化。直流點(diǎn)平衡以后,在信號(hào)傳輸?shù)穆窂缴衔覀兙涂梢圆捎肁C耦合方式(最常用的方法是在發(fā)送端或接收端串接隔直電容),這樣信號(hào)對(duì)于收發(fā)端的地電平變化和共模噪聲的抵抗能力進(jìn)一步增強(qiáng),可以傳輸更遠(yuǎn)的距離。采用AC耦合方式的另一個(gè)好處是收發(fā)端在做互連時(shí)不用太考慮直流偏置點(diǎn)的互相影響,互連變得非常簡(jiǎn)單,對(duì)于熱插拔的支持能力也更好。

有利于信號(hào)校驗(yàn)。很多高速信號(hào)在做傳輸時(shí)為了保證傳輸?shù)目煽啃砸獙?duì)接收到的信號(hào)進(jìn)行檢查以確認(rèn)收到的信號(hào)是否正確。在8b/10bit編碼表里,原始的8bit數(shù)據(jù)總共有256個(gè)組合,即使考慮到每個(gè)Byte有正負(fù)兩個(gè)10bit編碼也只需要用到512個(gè)10bit的組合。而10bit的數(shù)據(jù)總共可以有1024個(gè)組合,因此有大約一半的10bit組合是無(wú)效的數(shù)據(jù),接收端一旦收到這樣的無(wú)效組合就可以判決數(shù)據(jù)無(wú)效。另外,前面我們介紹過(guò)數(shù)據(jù)在傳輸過(guò)程中是要保證直流平衡的,一旦接收端收到的數(shù)據(jù)中發(fā)現(xiàn)違反直流平衡的規(guī)則,也可以判決數(shù)據(jù)無(wú)效。因此采用8b/10b編碼以后數(shù)據(jù)本身就可以提供一定的信號(hào)校驗(yàn)功能。不過(guò)需要注意的是,這種校驗(yàn)不是足夠可靠,因?yàn)槔碚撋线€是可能存在有幾個(gè)bit在傳輸中發(fā)生了錯(cuò)誤但是結(jié)果仍然符合8b/10b編碼和規(guī)則和直流平衡原則。因此,很多使用8b/10b編碼的總線都還會(huì)在上層協(xié)議上再做相應(yīng)的CRC校驗(yàn)(循環(huán)冗余校驗(yàn))。

可以插入控制字符。在10bit數(shù)據(jù)可以表示的1024個(gè)組合中,除了512個(gè)組合用于對(duì)應(yīng)原始的8bit數(shù)據(jù)以及一些不太好的組合(比如0b1100000000這樣信號(hào)里有太長(zhǎng)的連續(xù)0或者1而且明顯0、1的數(shù)量不平衡)以外,還有一些很特殊的組合。這些特殊的組合可以用來(lái)在數(shù)據(jù)傳輸過(guò)程中做為控制字符插入。這些控制字符不對(duì)應(yīng)特定的8bit數(shù)據(jù),但是在有些總線應(yīng)用里可以代表一些特殊的含義。比如K28.5碼型,其特殊的碼型組合可以幫助接收端更容易判別接收到的連續(xù)的10bit數(shù)據(jù)流的符號(hào)邊界,所以在一些總線的初始化階段或數(shù)據(jù)包的包頭都會(huì)進(jìn)行發(fā)送。還有一些特殊的符號(hào)用于進(jìn)行鏈路訓(xùn)練、標(biāo)記不同的數(shù)據(jù)包類型、進(jìn)行收發(fā)端的時(shí)鐘速率匹配等。

綜上所述,要把并行的信號(hào)通過(guò)串行總線傳輸,一般需要對(duì)數(shù)據(jù)進(jìn)行并串轉(zhuǎn)換。為了進(jìn)一步減少傳輸線的數(shù)量和提高傳輸距離,很多高速數(shù)據(jù)總線采用嵌入式時(shí)鐘和8b/10b的數(shù)據(jù)編碼方式。8b/10b編碼由于直流平衡、支持AC耦合、可嵌入時(shí)鐘信息、抗共模干擾能力強(qiáng)、編解碼結(jié)構(gòu)相對(duì)簡(jiǎn)單等優(yōu)點(diǎn),在很多高速的數(shù)字總線如FiberChannel、PCI-E、SATA、USB3.0、DisplayPort、XAUI、RapidIO等接口上得到廣泛應(yīng)用。

-

編碼

+關(guān)注

關(guān)注

6文章

967瀏覽量

55595 -

串行總線

+關(guān)注

關(guān)注

1文章

185瀏覽量

31034

原文標(biāo)題:串行總線的8b/10b編碼

文章出處:【微信號(hào):gh_bee81f890fc1,微信公眾號(hào):面包板社區(qū)】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

USB3.0中8b/10b編解碼器的設(shè)計(jì)

8b10b編碼verilog實(shí)現(xiàn)

Aurora 8b/10b IP核問(wèn)題

8b/10b編解碼的控制字問(wèn)題

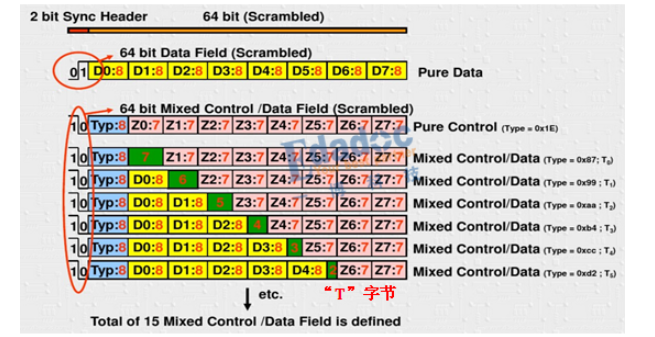

淺析64B//66B編碼

收發(fā)器向?qū)е袉⒂?b class='flag-5'>8b/10b編碼器的方法是什么?

如何使用Aurora 8B / 10B建立僅傳輸?

怎么禁用Aurora IP Core 8B / 10B中的時(shí)鐘補(bǔ)償功能?

基于FPGA的8B/10B編解碼設(shè)計(jì)

基于PRBS的8B/10B編碼器誤碼率為0設(shè)計(jì)

基于Virtex-6 的Aurora 8B/10B,PCIe2.0,SRIO 2.0三種串行通信協(xié)議分析

淺談高速信號(hào)的64B/66B編碼方式

高速串行通信常用的編碼方式-8b/10b編碼/解碼解析

串行總線的8b/10b編碼

串行總線的8b/10b編碼

評(píng)論