文章來源:學習那些事

原文作者:小陳婆婆

本文主要講解了Bi-CMOS工藝。

Bi-CMOS工藝將雙極型器件(Bipolar)與CMOS工藝結合,旨在融合兩者的優勢。CMOS具有低功耗、高噪聲容限、高集成度的優勢,而雙極型器件擁有大驅動電流、高速等特性。Bi-CMOS則能通過優化工藝參數,實現速度與功耗的平衡,兼具CMOS的低功耗和雙極器件的高性能,本文分述如下

Bi-CMOS概述

Bi-CMOS工藝分類

Bi-CMOS工藝詳解

Bi-CMOS的核心優點

驅動能力增強:相同尺寸下,Bi-CMOS邏輯門的驅動電流更大,驅動大電容負載時速度顯著提升。

低功耗特性:與CMOS門電路靜態功耗相當,但動態(交流)功耗更低。

接口兼容性:可直接驅動TTL或ECL電平接口,簡化系統設計。

主要應用場景

存儲器電路:如SRAM中,雙極器件構成靈敏放大器,檢測微小電壓變化。

高速數字電路:雙極器件驅動大電容負載,提升電路速度。

數模混合電路:結合CMOS的數字邏輯與雙極器件的模擬精度,適用于高精度傳感器或射頻電路。

Bi-CMOS工藝分類

根據應用場景和成本需求,Bi-CMOS工藝分為三類:

低成本、中速數字Bi-CMOS

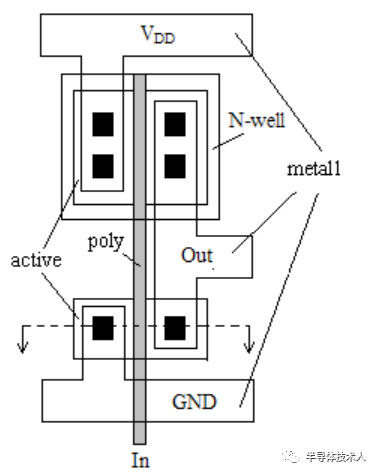

工藝特點:基于標準N阱CMOS工藝,增加一塊掩膜版形成雙極晶體管的P型基極,N阱作為集電極。

結構:發射極由NMOS源漏注入完成,采用LOCOS隔離。

缺點:集電極串聯電阻(Rc)較大(約2kΩ),限制強電流下的性能。

高成本、高性能數字Bi-CMOS

工藝特點:確保CMOS和雙極器件性能均達到單獨工藝水平,需額外增加3~4塊掩膜版。

實現方式:

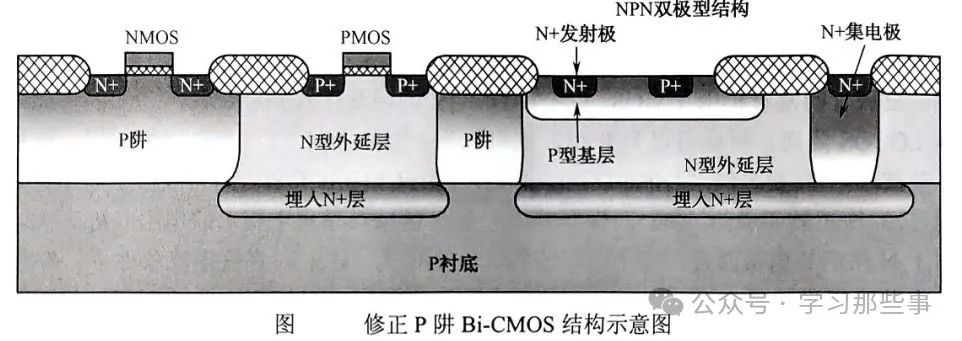

修正P阱工藝:優化阱結構以提升雙極器件性能。

修正雙阱工藝:通過深阱隔離技術減少寄生效應,提高集成度。

數模混合Bi-CMOS

數模混合Bi-CMOS工藝與數字Bi-CMOS的核心區別在于其需適應寬范圍工作電壓(尤其是高壓場景),這對器件結構和工藝設計提出了特殊要求。

特點:工作電壓范圍寬(模擬部分需高壓),復雜工藝通常由雙極工藝衍生而來。

關鍵器件:PNP晶體管、精密電阻/電容,用于模擬電路的低噪聲和匹配特性。

以下從工藝分類、關鍵設計考量及典型工藝步驟展開分析:

數模混合Bi-CMOS工藝根據電壓和功率需求分為兩類:

中壓工藝(10~30V):基于標準CMOS流程優化,需平衡高電壓耐受與器件性能。例如,加厚柵氧以提升柵壓承受能力,但會犧牲部分驅動電流。

大功率工藝(>30V且>1A):采用功率模擬工藝,需強化器件的電流承載能力和散熱設計,常用于電源管理或電機驅動等場景。

關鍵設計考量——高壓耐受性

柵氧加厚:防止高柵壓下氧化層擊穿,但導致MOS管飽和電流降低,需通過工藝調整(如優化溝道摻雜)補償性能損失。

隔離結構優化:采用擴散隔離(如CDI)或深溝槽隔離,避免高壓下寄生器件開啟。

模擬器件精度

多晶硅電阻:溫度系數優于擴散電阻,適用于高精度模擬電路

PIP電容:多晶硅-絕緣層-多晶硅結構(Poly-Insulator-Poly)寄生效應小,適合開關電容電路和A/D轉換器。

寄生效應抑制

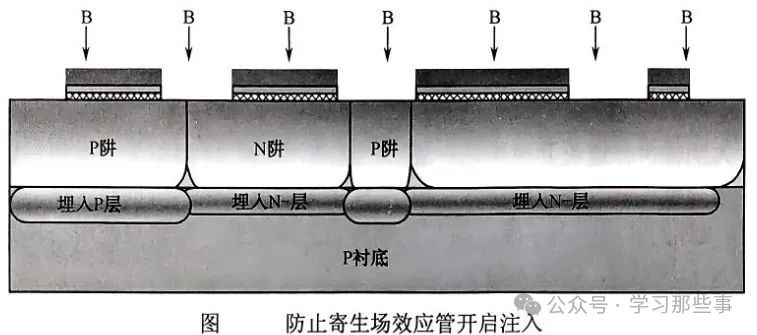

防寄生場效應管注入:通過離子注入調整寄生管閾值電壓,避免高壓下意外導通。

技術挑戰與優化方向

集電極電阻問題:低成本工藝中Rc過大,需通過優化摻雜或結構改進(如埋層集電極)降低電阻。

工藝復雜度:高性能和數模混合工藝需平衡掩膜步驟增加帶來的成本與設計靈活性。

功耗與速度權衡:根據應用場景調整雙極器件比例,例如在關鍵路徑插入雙極器件以提升速度,其余部分保持CMOS低功耗。

Bi-CMOS工藝詳解

P阱與雙阱工藝對比

P阱Bi-CMOS工藝(SBC工藝)

工藝特點

材料結構:采用P型襯底+N型外延層,通過重摻雜的N+埋層形成雙極晶體管的集電極

核心優勢

低集電極電阻(Rc):N+埋層顯著降低Rc,提升電流驅動能力。

抗閂鎖能力增強:N型外延層替代P型外延,降低寄生PNPN路徑的增益。

閂鎖敏感性降低:埋層結構減少襯底耦合效應。

隔離方式:P阱提供雙極結隔離,防止相鄰集電極間的干擾。

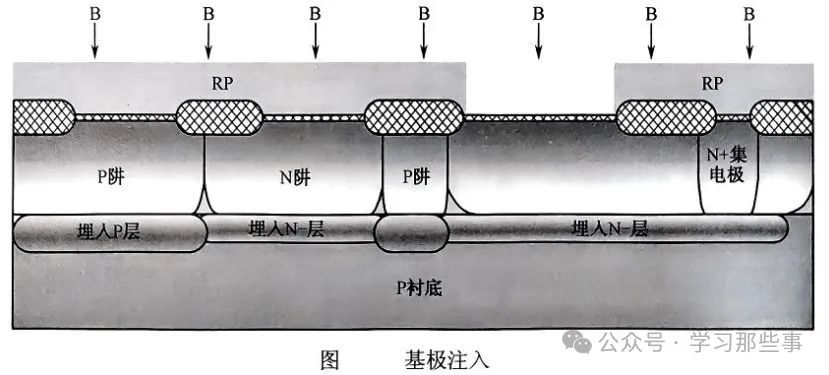

掩膜增加:需額外3塊掩膜版(N+埋層、深N+集電極、P基極區)。

應用場景:適用于對集成度要求適中、需平衡成本與性能的Bi-CMOS電路。

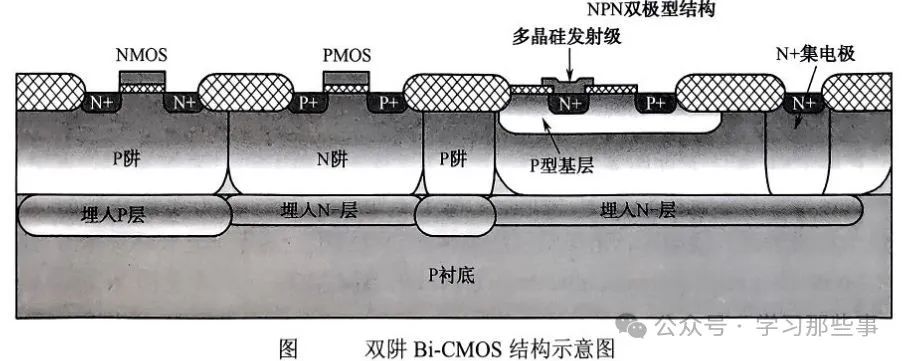

雙阱Bi-CMOS工藝(高性能工藝)

工藝改進

自校準埋層:引入埋入P層

使相鄰集電極間距縮小至亞微米級,提升集成度。

外延層優化:采用近本征(低摻雜)外延層,靈活調整摻雜濃度以滿足雙極與PMOS器件需求。

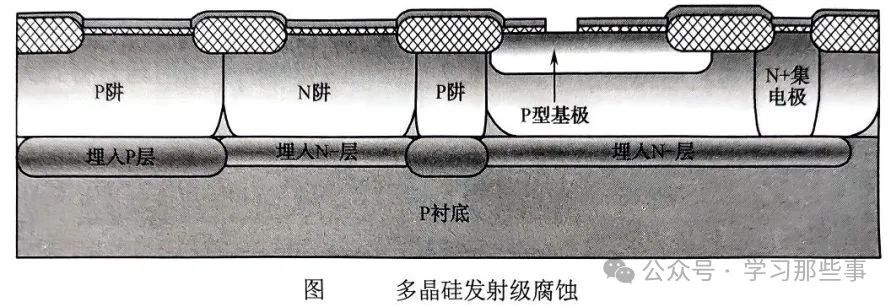

多晶硅發射

性能提升:淺發射極+窄基區寬度提高截止頻率。

工藝簡化:同一多晶硅層兼作CMOS柵極與雙極發射極,減少額外步驟。

掩膜增加:需4塊額外掩膜版(埋入N+、深N+擴散、P基極、多晶硅發射極)。

技術優勢

高密度集成:緊湊的集電極布局支持復雜電路設計。

靈活性:獨立優化P阱與N阱摻雜,適配不同器件需求。

電壓兼容性:支持3.3V/5V電路,適用于高性能混合信號系統。

雙阱Bi-CMOS工藝步驟詳解

初始材料:P型輕摻雜100晶向硅片。

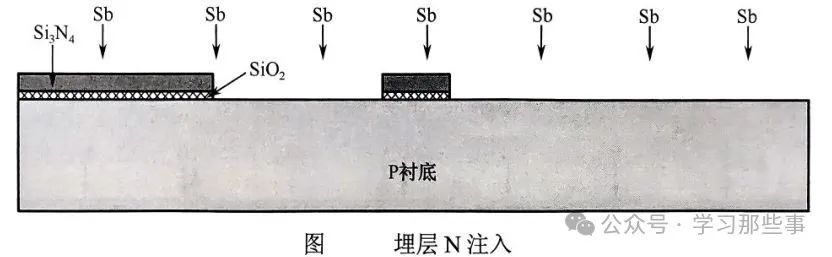

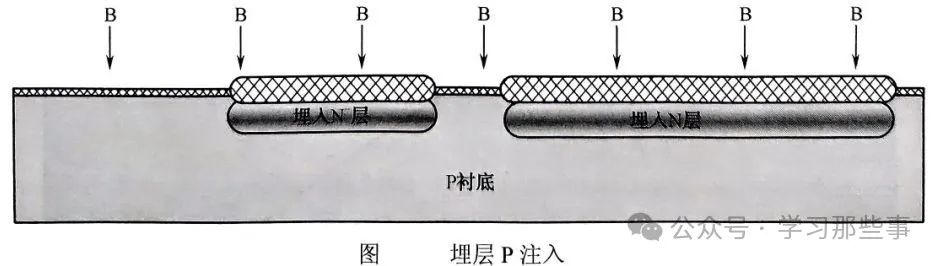

埋層形成

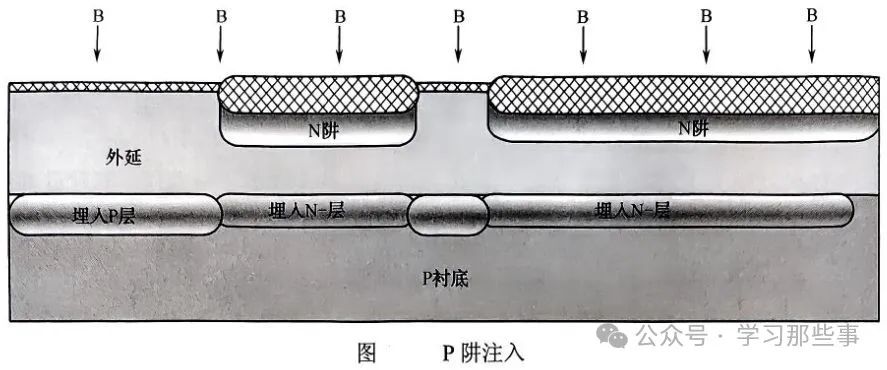

N埋層:光刻定義區域,銻注入后退火,形成N+埋層

自對準P埋層:硼注入時,厚氧化層阻擋N埋層區域,形成P埋層

外延生長:沉積外延層,摻雜濃度由器件需求決定。

阱工藝

N阱:磷注入并推阱,厚氧化層阻擋后續硼注入。

P阱:利用N阱氧化層阻擋,硼注入形成P阱

有源區與隔離

LOCOS隔離:多晶硅緩沖層提高集成度

雙極器件制作

N+集電極:磷注入并擴散至埋層N

P基極:硼注入形成基區。

多晶硅發射極

雙層多晶硅:第一層定義發射極窗口,第二層形成發射極接觸

后續工藝:與標準CMOS工藝兼容,完成金屬互聯等步驟。

-

CMOS

+關注

關注

58文章

6001瀏覽量

238295 -

工藝

+關注

關注

4文章

677瀏覽量

29303 -

數字電路

+關注

關注

193文章

1638瀏覽量

81667 -

數模混合

+關注

關注

0文章

24瀏覽量

9404

原文標題:Bi-CMOS工藝解析

文章出處:【微信號:bdtdsj,微信公眾號:中科院半導體所】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

CMOS,Bipolar,FET這三種工藝的優缺點是什么?

特征工藝尺寸對CMOS SRAM抗單粒子翻轉性能的影響

視頻驅動芯片ISL59830相關資料推薦

《炬豐科技-半導體工藝》CMOS 單元工藝

分享芯片SWF254N

MSC1163 pdf datasheet (40-Bit

A705,pdf,datasheet (220mA ADVA

OCP8110,pdf 350mA Advanced Cur

一種采用Bi-CMOS 緩沖器的LDO電路設計

新型BiCMOS集成運算放大器設計

LIN通信總線標準和混合信號半導體工藝技術提高汽車維護性能和可靠性

什么是BCD工藝?BCD工藝與CMOS工藝對比

Bi-CMOS工藝解析

Bi-CMOS工藝解析

評論