概述

AD8343是一款高性能、寬帶有源混頻器,具有極低交調(diào)失真,所有端口均具有寬帶寬,非常適合要求嚴格的發(fā)射應(yīng)用或接收通道應(yīng)用。

AD8343的典型變頻增益為7 dB。集成的LO驅(qū)動器以低LO驅(qū)動電平,支持50 Ω差分輸入阻抗,有助于將外部元件數(shù)降至較少。

開發(fā)差分輸入可以直接與差分濾波器接口,或通過平衡-不平衡變換器(變壓器)驅(qū)動,由單端源提供平衡驅(qū)動。

開集差分輸出可以用來驅(qū)動差分中頻信號接口,或通過匹配網(wǎng)絡(luò)或變壓器轉(zhuǎn)換為單端信號。以VPOS電源電壓為中心時,輸出擺幅為±1 V。

LO驅(qū)動器電路的典型功耗為15 mA。可利用兩個外部電阻來設(shè)置混頻器內(nèi)核電流,以達到要求的性能,總電流為20 mA至60 mA。采用5 V單電源供電時,相應(yīng)的功耗為100 mW至300 mW。

AD8343采用ADI公司的高性能25 GHz硅雙極性IC工藝制造,提供14引腳TSSOP封裝,工作溫度范圍為?40°C至+85°C,同時提供配置齊全的評估板。

數(shù)據(jù)表:*附件:AD8343 DC至2.5 GHz 、高IP3有源混頻器技術(shù)手冊.pdf

應(yīng)用

- 蜂窩基站

- 無線局域網(wǎng)(LAN)

- 衛(wèi)星轉(zhuǎn)換器

- SONET/SDH無線電

- 無線電鏈路

- 無線電鏈路

特性

- 高性能有源混頻器

- 寬帶操作,頻率最高達2.5 GHz

- 轉(zhuǎn)換增益:7 dB

- 輸入IP3:16.5 dBm

- LO驅(qū)動:–10 dBm

- 噪聲系數(shù):14 dB

- 輸入P1dB:2.8 dBm

- 差分LO、IF和RF端口

- 50 Ω LO輸入阻抗

- 單電源供電:5 V(50 mA,典型值)

- 省電模式:20 μA(典型值)

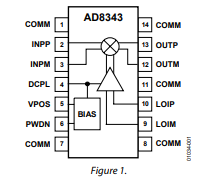

框圖

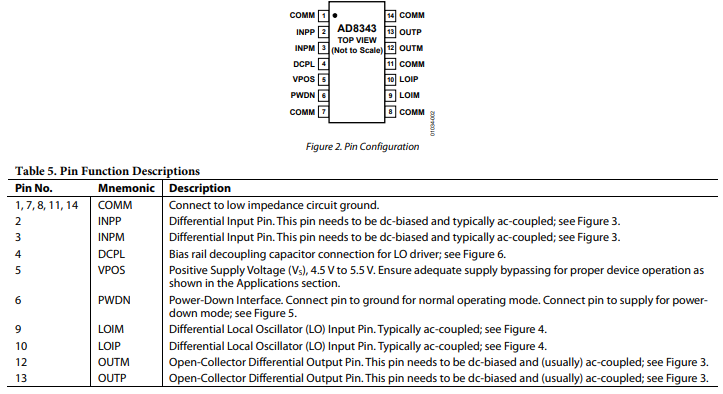

引腳配置描述

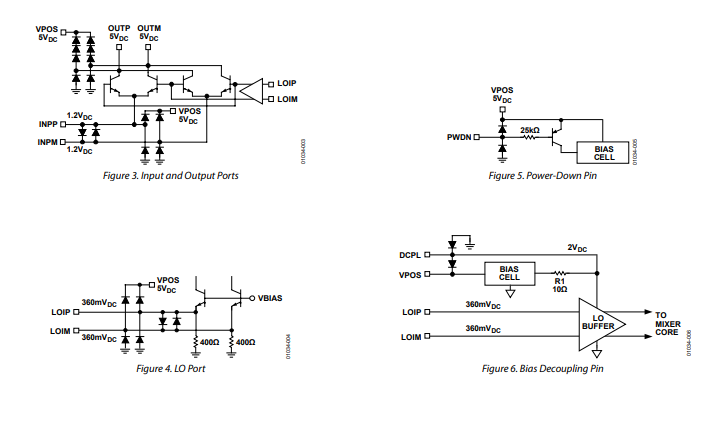

簡化接口示意圖

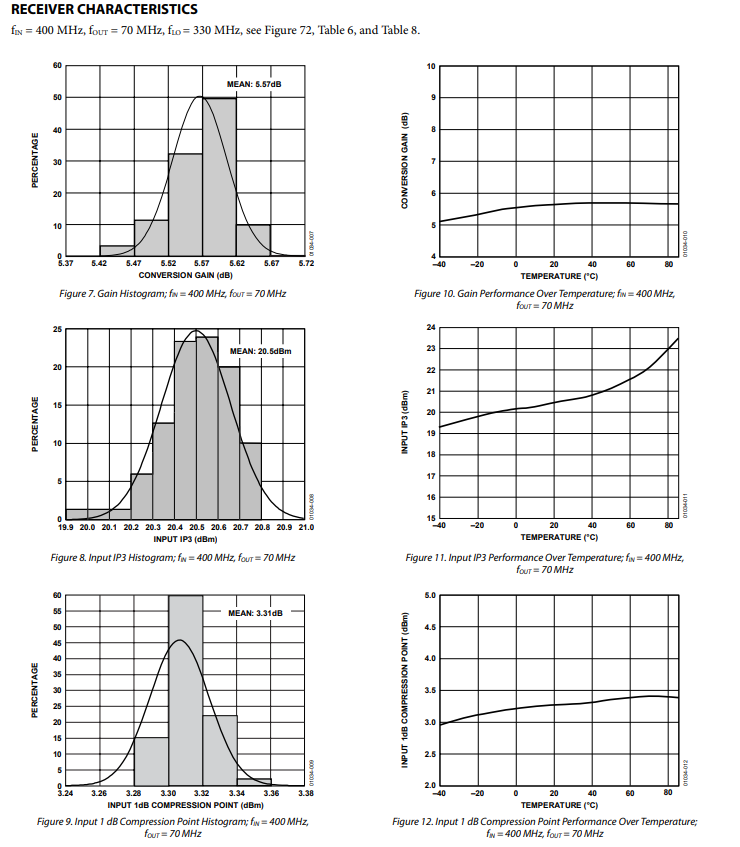

典型性能特征

電路描述

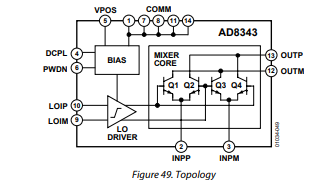

AD8343 是一款適用于高截點應(yīng)用的混頻器。其信號路徑完全為差分且直流耦合,能夠在寬頻率范圍內(nèi)實現(xiàn)高性能運行。功能模塊的基本框圖見圖 49。偏置單元為本地振蕩器(LO)驅(qū)動器和核心提供與絕對溫度成比例(PTAT)的偏置。LO 驅(qū)動器由三級限幅差分放大器組成,能為混頻器核心的基極提供極快速(近乎方波)的驅(qū)動。

AD8343 核心采用標準架構(gòu),通過施加信號輸入來激勵單元中的晶體管(見圖 49 和圖 55)。基極由限幅的內(nèi)部 LO 信號驅(qū)動,該信號引導(dǎo)晶體管在輸出端之間交替切換,從而使信號與 LO 方波進行周期性極性反轉(zhuǎn),實現(xiàn)乘法運算。

為說明此功能,當(dāng) LOIP 為正時,Q1 和 Q4 導(dǎo)通,Q2 和 Q3 截止。在此狀態(tài)下,Q1 將 I_{INSP} 連接至 OUTP,Q4 將 I_{INSM} 連接至 OUTM。當(dāng) LOIP 為負時,晶體管角色反轉(zhuǎn),I_{INSM} 連接至 OUTP,I_{INSP} 連接至 OUTM。通過共基極晶體管放大器對實現(xiàn)隔離和增益,可在任何瞬間保證信號通過。

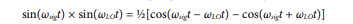

乘法運算會產(chǎn)生頻率混頻,理想的乘法器可構(gòu)成出色的混頻器。該原理可用以下三角函數(shù)恒等式表示:

這表明兩個不同頻率的正弦波相乘,結(jié)果是一對頻率等于兩相乘頻率之和與差的正弦波。

遺憾的是,由于線性度不佳以及添加噪聲,模擬乘法器在實際應(yīng)用中通常并非理想的混頻器,這在試圖提高線性度時尤為明顯。但本章節(jié)中的混頻器通過使信號周期性地反轉(zhuǎn)極性來解決此問題。在此類混頻器中,頻率轉(zhuǎn)換是信號與 LO 頻率處的方波相乘的結(jié)果。由于方波除基頻外還包含奇次諧波,信號會被 LO 的每個頻率分量有效地相乘。混頻器輸出為

等。LO 諧波產(chǎn)生的分量幅度隨諧波階數(shù)增加而減小,因為方波諧波的幅度會隨諧波階數(shù)增加而減小。

圖 50 展示了此過程的一個示例。該圖第一部分顯示一個 800MHz 的正弦波代表輸入信號,第二部分是一個 600MHz 的方波代表 LO 信號,第三部分展示了輸出變換的時域表示,第四部分展示了頻域表示。頻譜中最強的兩條線是由 LO 基頻乘法產(chǎn)生的和頻與差頻。較弱的譜線是信號與 LO 方波各諧波相乘的結(jié)果。

應(yīng)用

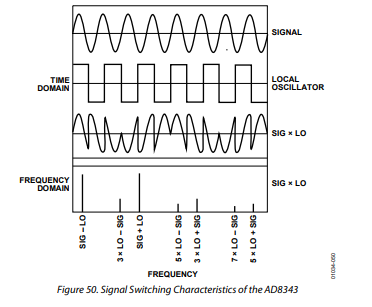

下變頻混頻器

典型的下變頻應(yīng)用如圖 69 所示,這是一個與 DC 電路相連的接收混頻器。單端輸入通過 1:1 傳輸線巴倫轉(zhuǎn)換為差分信號,輸入匹配網(wǎng)絡(luò)位于巴倫和輸入引腳之間。LO 信號通過一個 2:1 匝數(shù)比變壓器傳輸?shù)奖镜卣袷幤饕_,-12dB 至 -3dB 的電平通過第二個 1:1 巴倫傳輸?shù)讲罘州敵鲎杩埂?/p>

中頻輸出通過 4:1(阻抗比)變壓器獲取,該變壓器可將 200Ω 差分負載反射到集電極。這種輸出耦合方式具有較寬的帶寬,不過在某些情況下,用戶可能希望在集電極處添加諧振槽路電路,以提供一定的中頻選擇性。與輸出變壓器中心抽頭串聯(lián)的鐵氧體磁珠(FB)可解決共模穩(wěn)定性問題。

在此電路中,PWDWN 引腳接地,使混頻器處于工作狀態(tài)。DCPI 引腳通過約 0.1μF 的電容接地。不將 DCPI 引腳接地會使器件輸出產(chǎn)生較高的噪聲電平。

R1A 和 R1B 將核心偏置電流設(shè)置為每側(cè) 18.5mA。L1A 和 L1B 提供所需的射頻扼流圈,以避免信號分流,Z2A 和 Z2B 構(gòu)成匹配網(wǎng)絡(luò),用于匹配 AD8343 的差分輸入阻抗與變壓器的差分輸出阻抗。

AD8343 的本地振蕩器引腳和 IO 引腳設(shè)計用于與巴倫和 1:1 巴倫配合工作。寬帶模式下,每側(cè)核心電流設(shè)置為 18mA。Z1、Z1A、Z2A 和 Z2B 構(gòu)成匹配網(wǎng)絡(luò),旨在將 AD8343 的差分輸出阻抗匹配到巴倫的差分輸入阻抗。假設(shè)輸出頻率足夠高,器件的輸入阻抗遠小于偏置電阻值,這樣可使輸入偏置電流消除,且對增益或互調(diào)失真幾乎沒有影響。

在此示例中,輸出信號通過差分匹配網(wǎng)絡(luò)獲取,計算 Z2 和 Z2A/Z2B,然后通過 1:1 巴倫和隔直電容連接到單端輸出。

假設(shè)輸出頻率足夠高,對 AD8343 輸出進行共軛匹配是理想的,這樣可使器件輸出與巴倫差分輸入之間實現(xiàn)共軛匹配。

此電路通過并聯(lián)方式為輸出晶體管集電極提供偏置電流,因為沒有方便的中心抽頭。鐵氧體磁珠與輸出偏置電感串聯(lián),可提供一些阻尼,有助于避免這種輸出巴倫可能出現(xiàn)的常見模式振蕩。這種振蕩會給輸入電路帶來負擔(dān),可能導(dǎo)致輸入電路出現(xiàn)過穩(wěn)定性故障,在寬頻率范圍內(nèi)呈現(xiàn)感性阻抗。

PWDWN 引腳接地,使混頻器處于工作狀態(tài)。DCPI 引腳必須通過約 0.1μF 的電容接地,以抑制內(nèi)部偏置電路產(chǎn)生的噪聲。

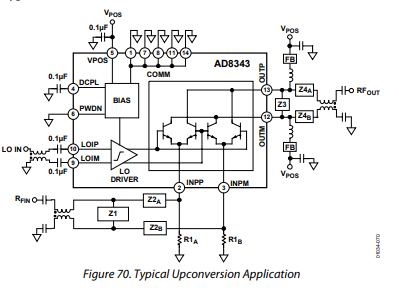

上變頻混頻器

典型的上變頻應(yīng)用如圖 70 所示,這是一個單端輸入到差分轉(zhuǎn)換的上變頻應(yīng)用。兩種配置均通過 1:1 傳輸線巴倫實現(xiàn)。

-

混頻器

+關(guān)注

關(guān)注

10文章

844瀏覽量

47052 -

變頻

+關(guān)注

關(guān)注

1文章

457瀏覽量

34521 -

有源

+關(guān)注

關(guān)注

0文章

150瀏覽量

23064

發(fā)布評論請先 登錄

請問AD8343的S參數(shù)仿真的外圍電路怎樣設(shè)計?

DC1983A,使用LTC5510,1 MHz至6 GHz寬帶高線性有源混頻器的演示板

AD8343 DC至2.5 GHz 、高IP3有源混頻器

DN515 - 高輸入 IP3 混頻器實現(xiàn)堅固型 VHF 接收器

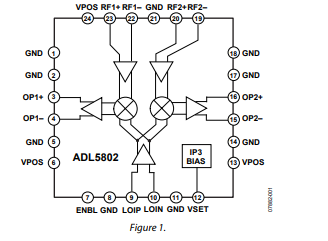

ADL5802:雙通道、高IP3、100 MHz至6 GHz有源混頻器產(chǎn)品手冊

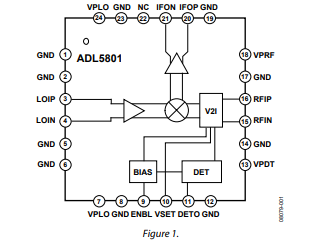

LTC5510:1 MHz至6 GHz寬帶高線性度有源混頻器數(shù)據(jù)表

AD8343:DC-2.5 GHz高頻IP3活動攪拌器數(shù)據(jù)Sheet

HMC485AMS8GE:高IP3 GaAs MMIC I/Q混頻器,帶集成LO放大器,1.7至2.4 GHz初步數(shù)據(jù)表

LTC5576:3 GHz至8 GHz高線性度有源上變頻混頻器數(shù)據(jù)表

LTC5577:300 MHz至6 GHz高信號電平有源下變頻混頻器產(chǎn)品手冊

高性能寬帶有源混頻器AD8343ARUZ 概述

聊聊混頻器IP3的測量以及測試誤差的來源分析

ADL5802雙通道、高IP3、100MHz ~ 6GHz有源混頻器技術(shù)手冊

AD8343 DC至2.5 GHz 、高IP3有源混頻器技術(shù)手冊

AD8343 DC至2.5 GHz 、高IP3有源混頻器技術(shù)手冊

評論