文章來(lái)源:學(xué)習(xí)那些事

原文作者:小陳婆婆

本文通過(guò)分析器件制造中的影響因素,提出了版圖設(shè)計(jì)技術(shù)與匹配原則及其應(yīng)用。

層次化版圖設(shè)計(jì)通過(guò)模塊化分解和系統(tǒng)級(jí)優(yōu)化,顯著提升了設(shè)計(jì)效率、布局優(yōu)化和失配控制。然而,工藝偏差和復(fù)雜設(shè)計(jì)仍是挑戰(zhàn)。結(jié)合Dummy Layer技術(shù)、工藝參數(shù)控制、先進(jìn)設(shè)計(jì)工具及模塊化方法,可有效應(yīng)對(duì)挑戰(zhàn),推動(dòng)集成電路性能與可靠性的持續(xù)提升。本文分述如下:

器件制造中的影響因素

版圖設(shè)計(jì)技術(shù)與匹配原則及其應(yīng)用

器件制造中的影響因素

在MOS場(chǎng)效應(yīng)管的制造過(guò)程中,設(shè)計(jì)尺寸與最終硅片上的實(shí)際尺寸存在差異,主要因素包括:

一、有效尺寸

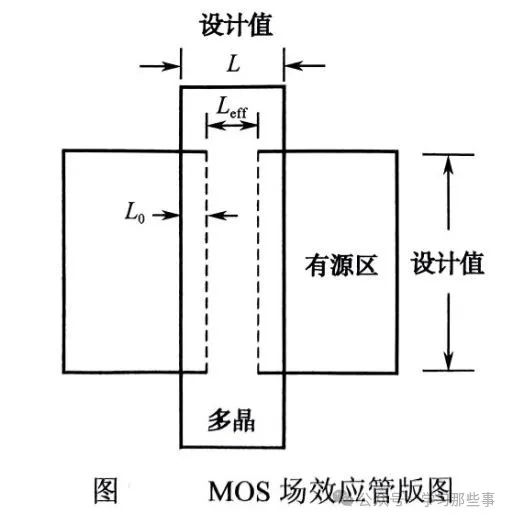

1.有效溝道長(zhǎng)度(Leff)

設(shè)計(jì)值L:多晶硅線寬的設(shè)計(jì)值。

實(shí)際值Leff:由于離子注入、摻雜、退火等工序中的橫向擴(kuò)散,實(shí)際電學(xué)溝道長(zhǎng)度減小,即 Leff=L?ΔL,其中 ΔL 為擴(kuò)散引起的長(zhǎng)度減小量。

2.有效溝道寬度(Weff)

設(shè)計(jì)值W:有源區(qū)的邊長(zhǎng)設(shè)計(jì)值。

實(shí)際值Weff:由于場(chǎng)氧生長(zhǎng)引起的有源區(qū)侵蝕,實(shí)際寬度減小,即 Weff=W?ΔW,其中 ΔW 為工藝引起的寬度減小量。

3.電氣分析依據(jù)

寬長(zhǎng)比:使用有效值之比 Leff/Weff進(jìn)行電路性能分析。

二、匹配設(shè)計(jì)與失配分析

匹配設(shè)計(jì)是模擬集成電路精度的關(guān)鍵,失配分為隨機(jī)失配和系統(tǒng)失配:

1.隨機(jī)失配:

原因:元器件尺寸、摻雜濃度、氧化層厚度的微觀波動(dòng)。

減小方法:電容,失配與面積平方根成反比,容量加倍可減小失配約30%;電阻,失配與寬度成反比,阻值加倍可減小失配50%;MOS管,閾值電壓和跨導(dǎo)的失配與晶體管面積平方根成反比。

2.系統(tǒng)失配:

原因:工藝偏差、接觸孔電阻、擴(kuò)散區(qū)相互影響、機(jī)械壓力和溫度梯度。

實(shí)例分析:多晶硅電阻,寬度偏差0.1μm導(dǎo)致阻值比失配2.4%;雙層多晶電容,刻蝕偏差0.16μm導(dǎo)致電容面積失配1.1%。

三、實(shí)際應(yīng)用中的最佳實(shí)踐

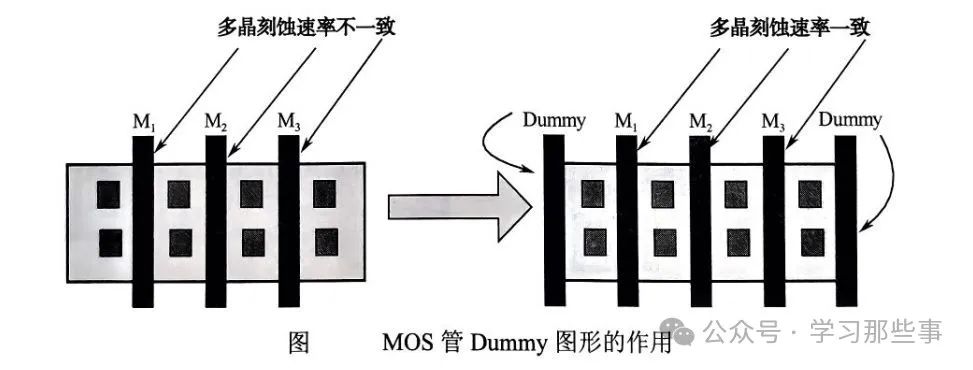

1.MOS管的Dummy技術(shù)

在MOS管設(shè)計(jì)中,Dummy技術(shù)主要用于提高器件的可靠性和一致性。

Dummy Poly的作用

避免柵長(zhǎng)變化:在MOS管兩側(cè)增加Dummy Poly,防止柵極長(zhǎng)度因工藝偏差而受到影響。

保護(hù)環(huán)設(shè)計(jì):NMOS管,先加P型保護(hù)環(huán)連接到地,再加N型保護(hù)環(huán)連接到電源;PMOS管,先加N型保護(hù)環(huán)連接到電源,再加P型保護(hù)環(huán)連接到地。

拆分原則:拆分MOS管時(shí),應(yīng)保證偶數(shù)根,Source端與四周保護(hù)環(huán)就近連接。

實(shí)例分析

保護(hù)環(huán)連接:保護(hù)環(huán)的設(shè)計(jì)有助于減小噪聲和工藝偏差對(duì)MOS管性能的影響。

Dummy Poly布局:通過(guò)合理布局Dummy Poly,可以平衡MOS管周?chē)墓に嚄l件,提高器件的一致性。

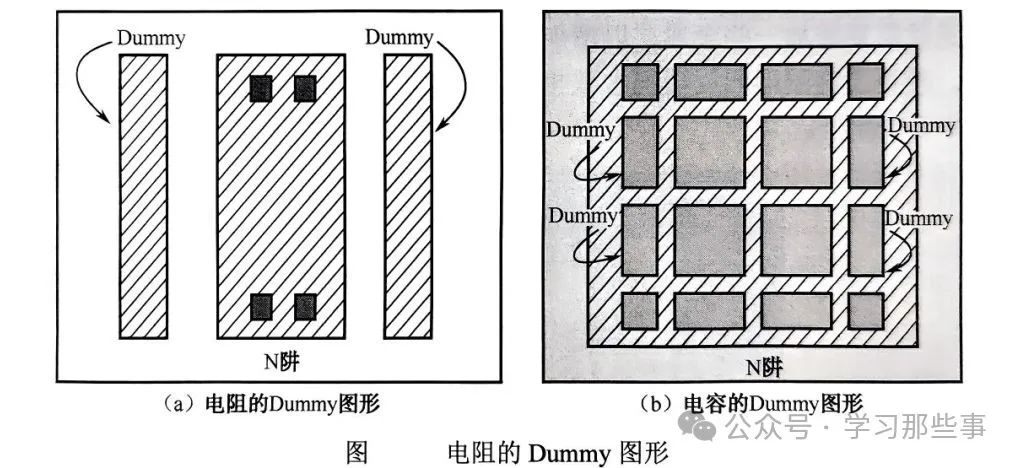

2.電阻和電容的Dummy技術(shù)

電阻和電容的Dummy技術(shù)主要用于減小噪聲和工藝偏差的影響。

電阻的Dummy技術(shù):N阱使用,在多晶或擴(kuò)散區(qū)電阻下面增加N阱,連接高電位與襯底反偏,以減輕噪聲對(duì)電阻的影響;金屬覆蓋,在N阱電阻上面覆蓋金屬并連接高電位,以降低光照使電阻阻值下降的影響。

電容的Dummy技術(shù):N阱阻擋,用N阱阻擋來(lái)自襯底的噪聲,N阱接高電位,襯底反偏;布局優(yōu)化,在電容周?chē)黾覦ummy電容,保證電容陣列的一致性。

版圖設(shè)計(jì)技術(shù)與匹配原則及其應(yīng)用

一、版圖設(shè)計(jì)技術(shù)

版圖設(shè)計(jì)技術(shù)旨在減小系統(tǒng)失配,提高元器件的匹配性能

1.單元元器件復(fù)制技術(shù)

原理:匹配的兩個(gè)元器件由某一個(gè)元器件單元的多個(gè)復(fù)制版本串聯(lián)或并聯(lián)構(gòu)成。

優(yōu)勢(shì):降低工藝偏差和歐姆接觸電阻不匹配的影響。

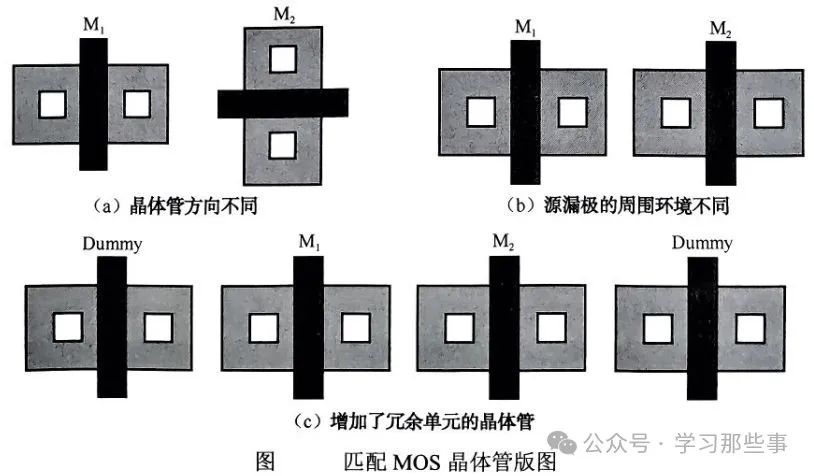

2.冗余單元增加

原理:在元器件周?chē)黾尤哂鄦卧WC周?chē)h(huán)境的一致性。

實(shí)例:如上圖(c)通過(guò)增加冗余單元減小了晶體管的不匹配。

3.元器件距離控制

原理:使匹配元器件之間的距離盡量接近,減小擴(kuò)散區(qū)之間的相互影響。

優(yōu)勢(shì):提高元器件的匹配性能。

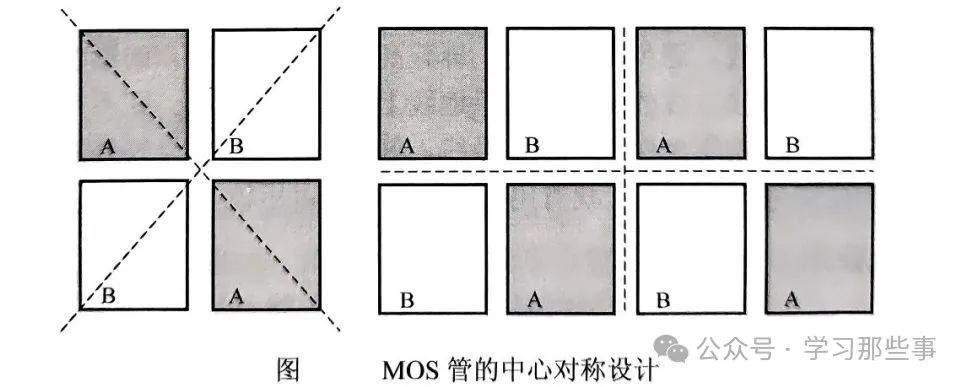

4.公用重心設(shè)計(jì)法

原理:使匹配元器件的“重心”重合,減小線性梯度的影響。

實(shí)例:上圖采用重心重合的MOS管設(shè)計(jì)。

5.元器件隔離

原理:匹配元器件與其他元器件保持一定距離,減小擴(kuò)散區(qū)之間的相互影響。

優(yōu)勢(shì):提高元器件的匹配精度。

二、 匹配原則

匹配原則旨在提高元器件的匹配性能:

1.靠近放置

原理:將匹配的器件靠近放置,以減小工藝偏差的影響。

優(yōu)勢(shì):提高元器件的匹配精度。

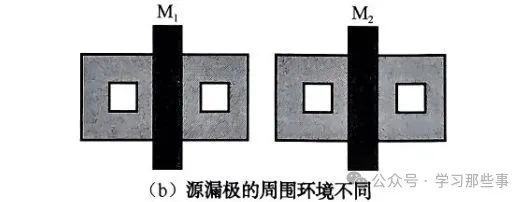

2.方向一致

原理:保持器件的方向一致,以提高匹配性能。

實(shí)例:圖(b)中晶體管方向一致但周?chē)h(huán)境不同,仍存在一定不匹配。

3.對(duì)稱(chēng)結(jié)構(gòu)

原理:采用對(duì)稱(chēng)結(jié)構(gòu),減小管子的失配。

優(yōu)勢(shì):提高電路的性能和可靠性。

4.布線最小化

原理:減少寄生電容,提高電路性能。

優(yōu)勢(shì):減小噪聲對(duì)關(guān)鍵信號(hào)的影響。

三、應(yīng)用場(chǎng)景與最佳實(shí)踐

1.應(yīng)用場(chǎng)景

改善匹配性:通過(guò)添加Dummy圖案,使芯片的各個(gè)區(qū)域在工藝過(guò)程中受到更加均勻的處理。

防止刻蝕過(guò)度或不足:Dummy圖案作為刻蝕阻擋層,幫助控制刻蝕的深度和范圍。

降低寄生電容和電感:通過(guò)合理設(shè)計(jì)Dummy圖案,降低寄生電容和電感。

提高芯片的可靠性:Dummy圖案幫助緩解應(yīng)力,提高芯片的可靠性。

2.最佳實(shí)踐

分析DRC報(bào)告:根據(jù)DRC報(bào)告確定需要添加Dummy的區(qū)域。

選擇合適的工具:使用Calibre等EDA工具添加Dummy。

檢查和優(yōu)化:插入Dummy后,再次運(yùn)行DRC檢查,確保新的版圖滿(mǎn)足所有的設(shè)計(jì)規(guī)則。

LVS驗(yàn)證:完成Dummy插入的版圖需要再次進(jìn)行LVS驗(yàn)證。

-

場(chǎng)效應(yīng)管

+關(guān)注

關(guān)注

47文章

1185瀏覽量

66415 -

MOS管

+關(guān)注

關(guān)注

109文章

2623瀏覽量

70624 -

版圖設(shè)計(jì)

+關(guān)注

關(guān)注

0文章

14瀏覽量

8849 -

可靠性測(cè)試

+關(guān)注

關(guān)注

1文章

118瀏覽量

14498

原文標(biāo)題:可靠性測(cè)試結(jié)構(gòu)設(shè)計(jì)——層次化版圖設(shè)計(jì)

文章出處:【微信號(hào):bdtdsj,微信公眾號(hào):中科院半導(dǎo)體所】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

MOS管器件制造中的影響因素

MOS管器件制造中的影響因素

評(píng)論