概述

AD9508提供時鐘扇出能力,針對能使系統性能達到優質的低抖動進行設計。這款器件能滿足時鐘數據轉換器等應用所需的相位噪聲和低抖動要求,可優化這些應用的性能。

數據表:*附件:AD9508 1.65GHz時鐘扇出緩沖器,集成輸出分頻器和延遲調整技.pdf

它集成4個獨立的差分時鐘輸出,每一個輸出都支持多種邏輯電平類型。包括LVDS (1.65 GHz)、HSTL (1.65 GHz)和1.8 V CMOS (250 MHz)。在1.8 V CMOS輸出模式下,差分輸出轉換為兩個CMOS單端信號。無論工作電源電壓如何改變,CMOS輸出始終為1.8 V邏輯電平。

每路輸出都有一個可編程分頻器,可以旁路該分頻器或者設置最高1024的整數分頻比。此外,AD9508還支持輸出相位在輸出之間進行粗調。

上電時,還可對器件進行各種固定配置的引腳編程,從而無需進行SPI或I^2^C編程。

AD9508提供24引腳LFCSP封裝,可以采用2.5 V或3.3 V單電源供電。溫度范圍為?40°C至+85°C。

應用

特性

- 1.65 GHz差分時鐘輸入/輸出

- 10位可編程分頻器,1至1024整數分頻比

- 高達4個差分輸出或8個CMOS輸出

- 用于上電時進行硬連線編程的引腳綁定功能

- 寬帶隨機抖動:<115 fs rms

- 加性輸出抖動:41fs rms(12 KHz至20 MHz)

- 出色的輸出間隔離

- 所有輸出自動同步

- 欲了解更多特性,請參考數據手冊

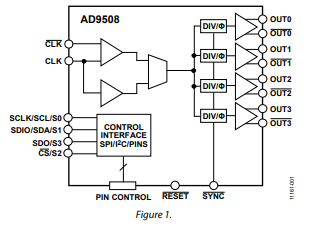

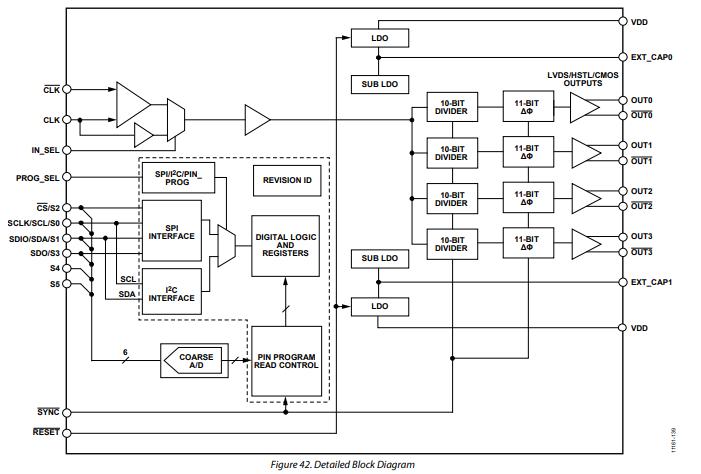

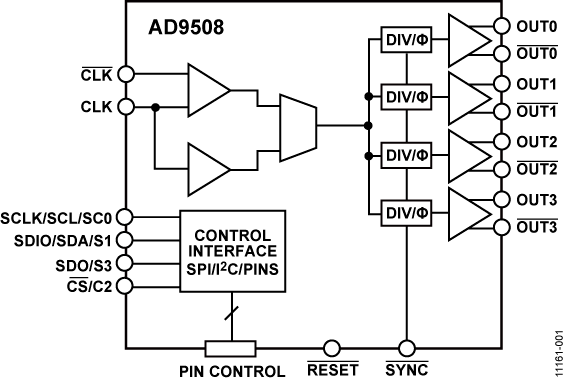

框圖

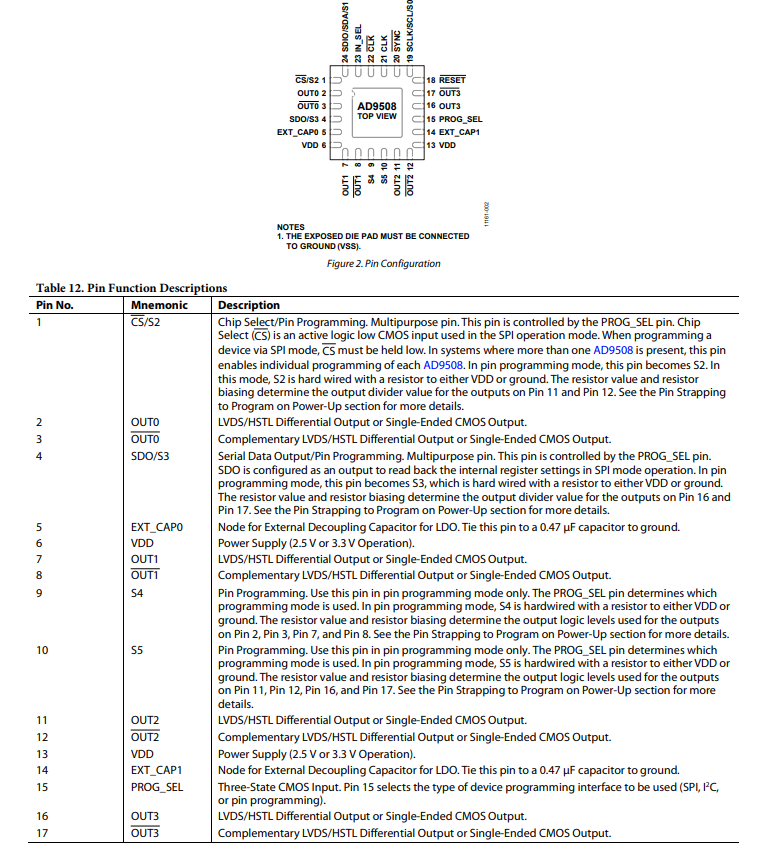

引腳配置描述

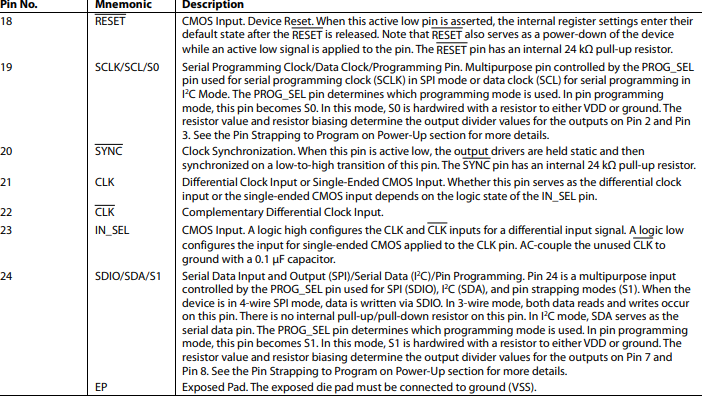

典型性能特征

操作理論

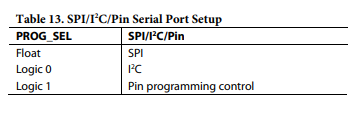

編程模式選擇

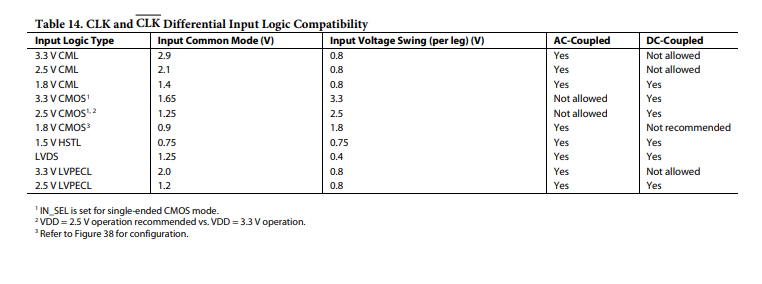

AD9508 可以接受施加到CLK和**overline{CLK}**引腳的差分輸入時鐘,或者單端1.8V(交流耦合)、2.5V 或 3.3V CMOS 時鐘(施加到CLK引腳)。輸入時鐘信號是時鐘分配部分的輸入,該部分具有可編程分頻器和相移調整功能。時鐘分配部分的工作頻率最高可達1650MHz。

在SPI或**I^{2}**C控制模式下,分頻器范圍為1到1024,相移調整的分辨率為11位。然而,在引腳編程模式下,分頻器范圍限制為最大16分頻,并且無相移調整功能。

輸出可配置為多達四個LVDS/HSTL差分輸出,或多達八個1.8V CMOS單端輸出。此外,不同輸出的輸出電流可針對輸出驅動強度進行調整。

該器件可由3.3V或2.5V外部電源供電;不過,芯片上的內部電源由一個1.8V LDO供電,從而在功耗最低的情況下實現高性能。

AD9508支持SPI和**I^{2}**C協議,并且可以通過引腳連接選擇對器件進行編程。活動接口取決于PROG_SEL引腳的邏輯狀態。有關編程模式選擇的詳細信息,請參見“串行控制端口”和“加電時引腳連接編程”部分。

時鐘輸入

IN_SEL引腳用于控制所需的輸入時鐘配置。當IN_SEL引腳設置為單端輸入模式時,器件期望在CLK引腳上接收到1.8V(交流耦合)、2.5V或3.3V CMOS兼容邏輯電平。將未使用的**overline{CLK}**引腳通過0.1μF電容旁路接地。

請注意,如果使用2.5V邏輯電平作為單端輸入時鐘模式,建議選擇2.5V電源選項,而非3.3V電源,以避免可能出現的占空比失真。當3.3V工作模式下的開關閾值電平(VDD/2或1.65V)升高且輸入信號緩慢上升并在閾值處下降時,可能會出現占空比失真。

不建議在單端CMOS邏輯配置中使用1.8V CMOS邏輯電平,這是因為輸入閾值電壓的變化過大。不過,差分輸入時鐘模式可用于1.8V CMOS輸入,圖38展示了1.8V CMOS輸入時鐘的推薦配置。

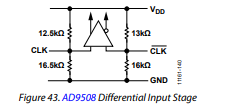

當IN_SEL引腳設置為差分輸入時鐘模式時,AD9508的輸入內部自偏置。內部輸入有一個電阻分壓器,其共模電平比實際輸入信號的共模電平低約30mV,以避免在輸入信號停止時輸入電路發生振蕩。等效差分輸入電路見圖43。

在差分模式下,輸入可以交流耦合或直流耦合。單端輸入邏輯兼容性見表14。用戶可以通過交流或直流耦合到差分輸入的一側,并通過電容將另一側旁路接地,來實現差分模式下的單端輸入。

-

緩沖器

+關注

關注

6文章

2056瀏覽量

47040 -

分頻器

+關注

關注

43文章

492瀏覽量

51169 -

時鐘

+關注

關注

11文章

1901瀏覽量

133242

發布評論請先 登錄

ADI發布新款時鐘緩沖器和分頻器IC AD9508

1.65GHz的時鐘輸出分頻器和延遲Fanout Buffer調整ad9508數據表

AD9508 1.65 GHz時鐘扇出緩沖器,集成輸出分頻器和延遲調整

AD9510:1.2 GHz時鐘分配IC,PLL內核,分頻器,延遲調整,8路輸出

AD9512:1.2 GHz時鐘分配IC,1.6 GHz輸入,分頻器,延遲調整,五輸出數據表

EVAD9508 AD9508評估板

CDCM1804 1:3 LVPECL時鐘緩沖器+附加LVCMOS輸出和可編程分頻器數據表

AD9508 1.65GHz時鐘扇出緩沖器,集成輸出分頻器和延遲調整技術手冊

AD9508 1.65GHz時鐘扇出緩沖器,集成輸出分頻器和延遲調整技術手冊

評論