什么是環(huán)形振蕩器

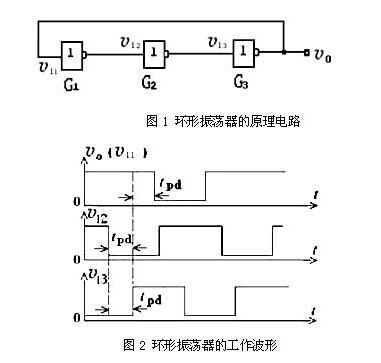

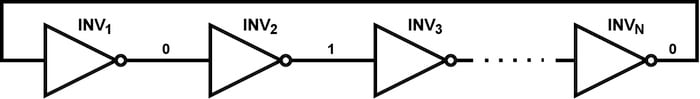

環(huán)形振蕩器,是由三個非門或更多奇數(shù)個非門輸出端和輸入端首尾相接,構(gòu)成環(huán)狀的機(jī)器。

以三個非門為例,即非門A輸出端連接到非門B輸入端,非門B輸出端連接到非門C輸入端,非門C輸出端到連接非門A輸入端,在其中任何一個連接的位置都可以引出輸出信號。

環(huán)形振蕩器原理

環(huán)形振蕩器是利用門電路的固有傳輸延遲時間將奇數(shù)個反相器首尾相接而成,該電路沒有穩(wěn)態(tài)。因?yàn)樵陟o態(tài)(假定沒有振蕩時)下任何一個反相器的輸入和輸出都不可能穩(wěn)定在高電平或低電平,只能處于高、低電平之間,處于放大狀態(tài)。

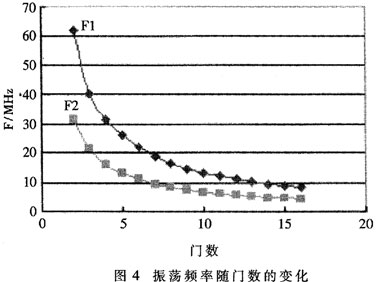

假定由于某種原因v11產(chǎn)生了微小的正跳變,經(jīng)G1的傳輸延遲時間tpd后,v12產(chǎn)生了一個幅度更大的負(fù)跳變,在經(jīng)過G2的傳輸延遲時間tpd后,使v13產(chǎn)生更大的正跳變,經(jīng)G3的傳輸延遲時間tpd后,在vo產(chǎn)生一個更大的負(fù)跳變并反饋到G1輸入端。可見,在經(jīng)過3tpd后,v11又自動跳變?yōu)榈碗娖剑俳?jīng)過3tpd之后,v11又將跳變?yōu)楦唠娖健H绱酥芏鴱?fù)始,便產(chǎn)生自激振蕩。如圖2所示,可見振蕩周期為T=6tpd

環(huán)形振蕩器的實(shí)用電路

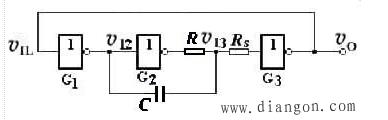

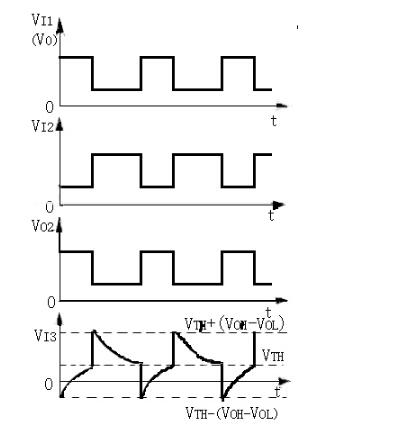

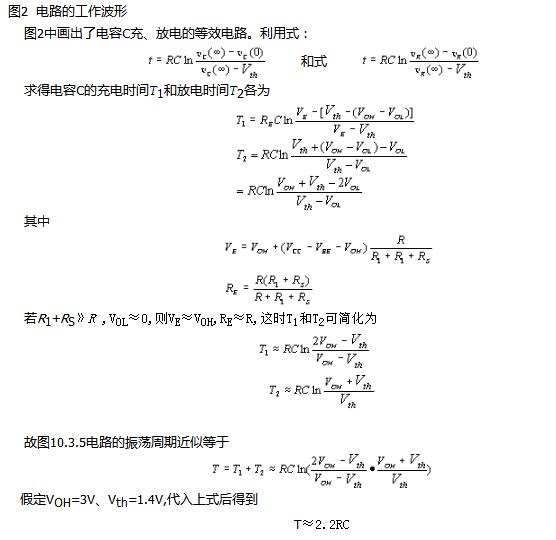

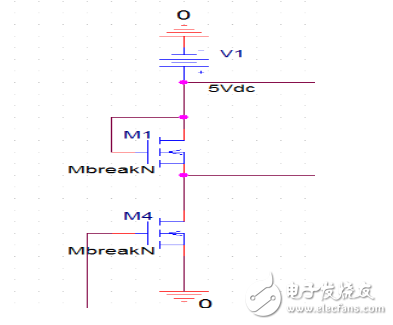

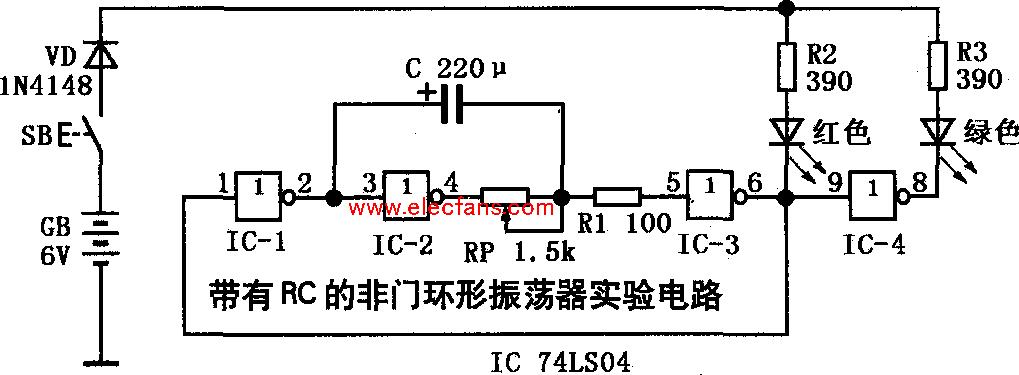

如圖1,為了進(jìn)一步加大RC和G2的傳輸延遲時間,在實(shí)用電路中將電容C 的接地端改接G1的輸出端。如圖2所示。例如當(dāng)v12處發(fā)生負(fù)跳變時,經(jīng)過電容C使v13首先跳變到一個負(fù)電平,然后再從這個負(fù)電平開始對電容C充電,這就加長了v13從 開始充電到上升為VTH的時間,等于加大了v12到v13的傳輸延遲時間。

圖4 環(huán)形振蕩器的實(shí)用改進(jìn)電路圖

通常RC電路產(chǎn)生的延遲時間遠(yuǎn)遠(yuǎn)大于門電路本身的傳輸延遲時間,所以在計(jì)算振蕩周期時可以只考慮RC電路的作用而將門電路固有的傳輸延遲時間忽略不計(jì)。

另外,為防止v13發(fā)生負(fù)跳變時流過反 相器G3輸入端鉗位二極管的電流過大,還在G3輸入端串接了保護(hù)電阻RS。電路中各點(diǎn)的電壓波形如圖2所示。

式T≈2.2RC可用于近似估算振蕩周期。但使用時應(yīng)注意它的假定條件是否滿足,否則計(jì)算結(jié)果會有較大的誤差。

環(huán)形振蕩器應(yīng)用

這種振蕩器的特點(diǎn)是線路簡單,起振容易,如果不加延遲網(wǎng)絡(luò)則不需要阻容元件,便于集成化,缺點(diǎn)是沒有延遲網(wǎng)絡(luò)頻率不便于靈活選擇,要實(shí)現(xiàn)低頻振蕩需要很多的非門因而不易實(shí)現(xiàn),另外由于門電路延遲時間有一定誤差,制作時頻率不太準(zhǔn)確。

如果加上阻容網(wǎng)絡(luò),則與同樣需要阻容元件的對稱多諧振蕩器或非對稱多諧振蕩器相比,所需芯片面積和成本不占優(yōu)勢。主要應(yīng)用于集成電路內(nèi)部集成的要求不高的高頻振蕩,以及普通數(shù)字電路中的簡易振蕩器。

-

環(huán)形振蕩器

+關(guān)注

關(guān)注

1文章

12瀏覽量

8786

發(fā)布評論請先 登錄

環(huán)形振蕩器,環(huán)形振蕩器工作原理是什么?

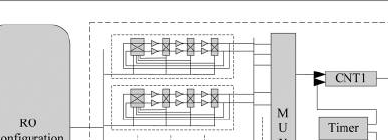

基于CPLD的片內(nèi)環(huán)形振蕩器的設(shè)計(jì)方案

環(huán)形振蕩器設(shè)計(jì)

一種頻率穩(wěn)定的改進(jìn)型CMOS環(huán)形振蕩器

一種頻率穩(wěn)定的改進(jìn)型CMOS環(huán)形振蕩器

環(huán)形振蕩器物理不可克隆函數(shù)詳解

環(huán)形振蕩器介紹_反相器構(gòu)成環(huán)形振蕩器

環(huán)形振蕩器的Multisim仿真實(shí)例電路原理圖免費(fèi)下載

可調(diào)可重構(gòu)的環(huán)形振蕩器物理不可克隆函數(shù)設(shè)計(jì)

通過環(huán)形振蕩器、555 定時器和 Arduino 進(jìn)行數(shù)字方波發(fā)生器設(shè)計(jì)

基于多級反饋環(huán)形振蕩器的真隨機(jī)數(shù)發(fā)生器設(shè)計(jì)

環(huán)形振蕩器原理及應(yīng)用_環(huán)形振蕩器的實(shí)用電路

環(huán)形振蕩器原理及應(yīng)用_環(huán)形振蕩器的實(shí)用電路

評論