歡迎來到《電源設計小貼士集錦》系列文章

本期,我們將介紹隔離單端初級電感轉換器 (SEPIC)的詳細知識

如果有人問您應使用哪種拓撲來實現隔離式低功耗輸出,那么您可能首先會想到反激式拓撲。雖然反激式拓撲是一種出色的拓撲結構,具有低成本、低元件數量和易于增加更多輸出等優點,但它仍有幾項缺陷。與反激式變壓器漏電感相關的場效應晶體管 (FET) 和整流器振鈴會產生電磁干擾 (EMI)、增加元件應力并降低效率。此外,當存在多個輸出時,難以獲得良好調節的電壓,尤其是在負載變化較大的情況下。下面了解一下另一種方法,即隔離單端初級電感轉換器 (SEPIC)如何減輕反激式拓撲的一些問題。

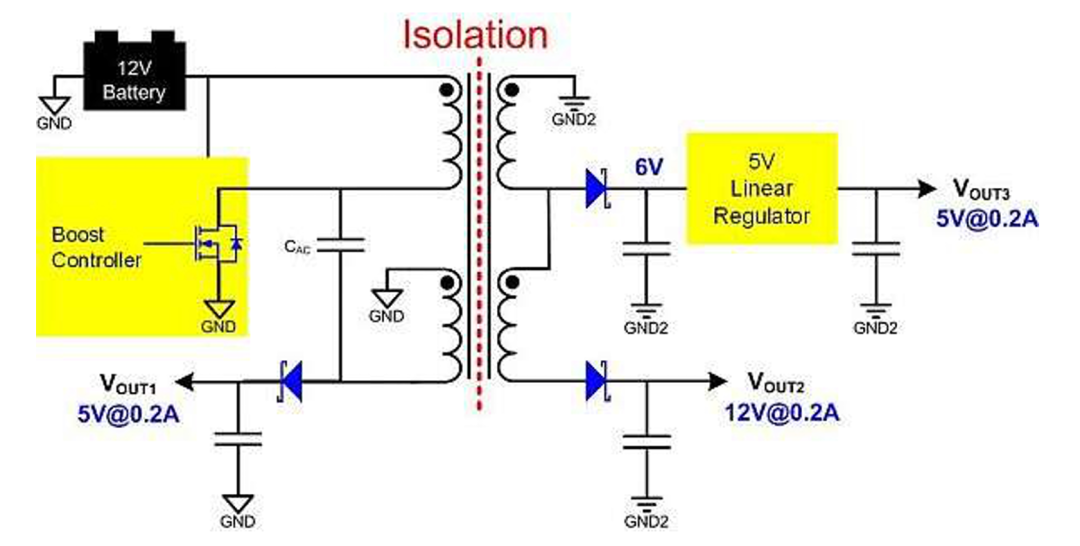

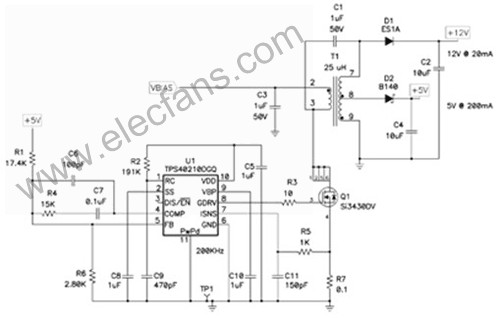

SEPIC是非隔離式拓撲。不過與反激式拓撲一樣,您可以輕松添加額外變壓器繞組來產生隔離式輸出。圖 1 簡化原理圖顯示了一個標準 SEPIC 轉換器,該轉換器在左側生成一個非隔離式輸出,在右側額外生成兩個隔離式輸出。第一個隔離式繞組提供標稱 6V 輸出,作為 5V 線性穩壓器的輸入。第二個隔離式繞組堆疊在第一個繞組之上,產生非穩壓 12V 輸出。

您需要在 VOUT1 的變壓器繞組和隔離式繞組(VOUT2、VOUT3)之間實現緊密耦合,因為這些繞組中的能量同時傳輸到全部三個輸出。這些繞組之間的漏電感只會降低它們的電壓調節性能。不過,SEPIC 的初級繞組和 VOUT1 繞組之間不需要緊密耦合。之所以能夠實現超小 FET 振鈴,是因為當升壓 FET 關斷時,電容器 CAC 為泄漏能量進入 VOUT1 提供了一條低阻抗路徑。由于 SEPIC 的初級繞組電壓波形的振鈴比反激式拓撲小得多,因此改善了輸出電壓調節性能,特別是在經常發生尖峰峰值檢測的極端交叉負載條件下。

圖 1:具有額外繞組的 SEPIC 轉換器提供隔離式輸出

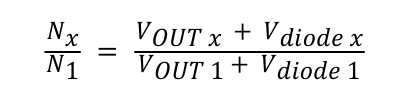

在所有 SEPIC 中,初級繞組與 VOUT1 繞組之間的匝數比必須為 1:1。但所有其他輸出都不受此匝數比的限制,您可以對其進行調整以提供任何所需的輸出電壓,可以使用方程式 1 輕松計算出輸出電壓:

方程式 1

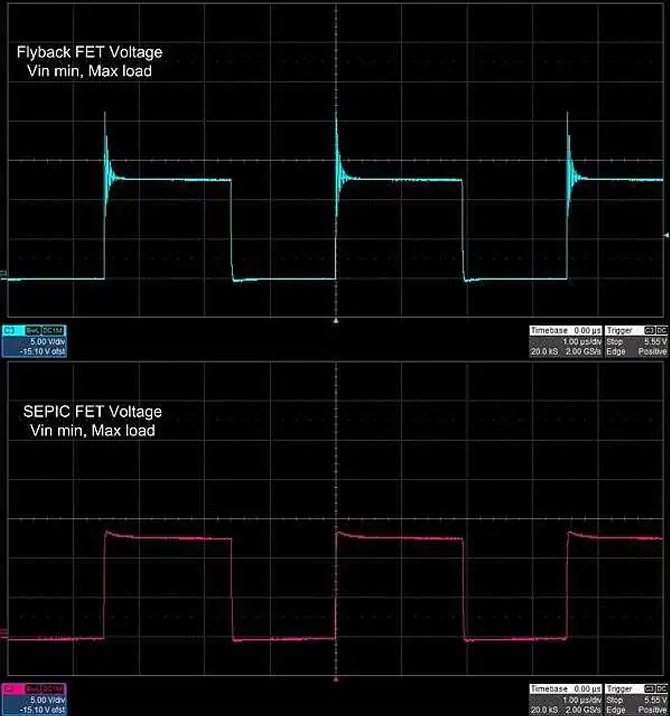

圖 2 顯示了 SEPIC 和反激式轉換器之間的FET 電壓振鈴差異。只需移除 CAC 即可從 SEPIC 電路獲得反激式 FET 電壓波形,從而將其轉換為反激式電路。消除 FET 上的振鈴可顯著降低傳導到隔離式輸出的非耦合能量,從而改善調節性能。

圖 2:SEPIC FET 上的電壓振鈴比反激式低,因此可降低應力并改善輸出電壓調節性能

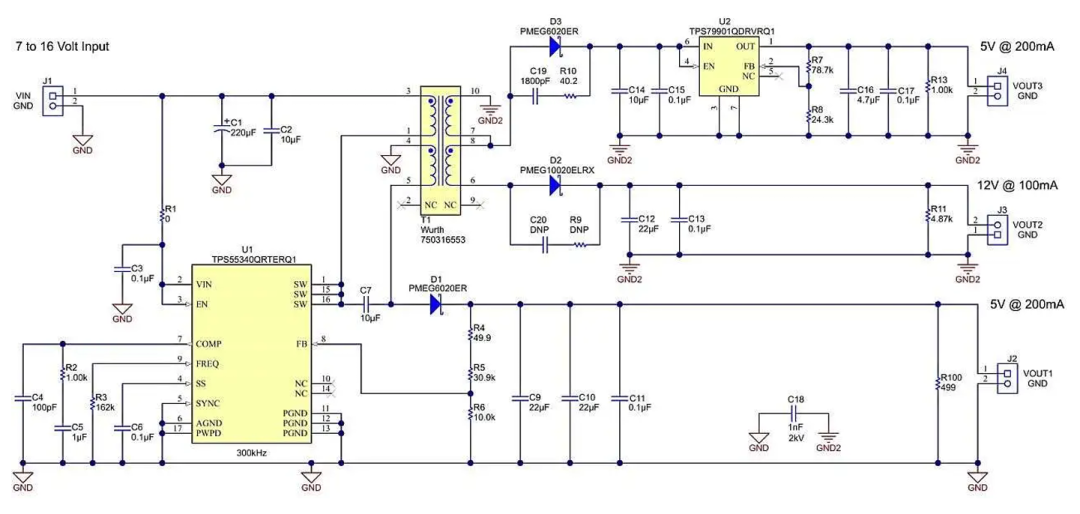

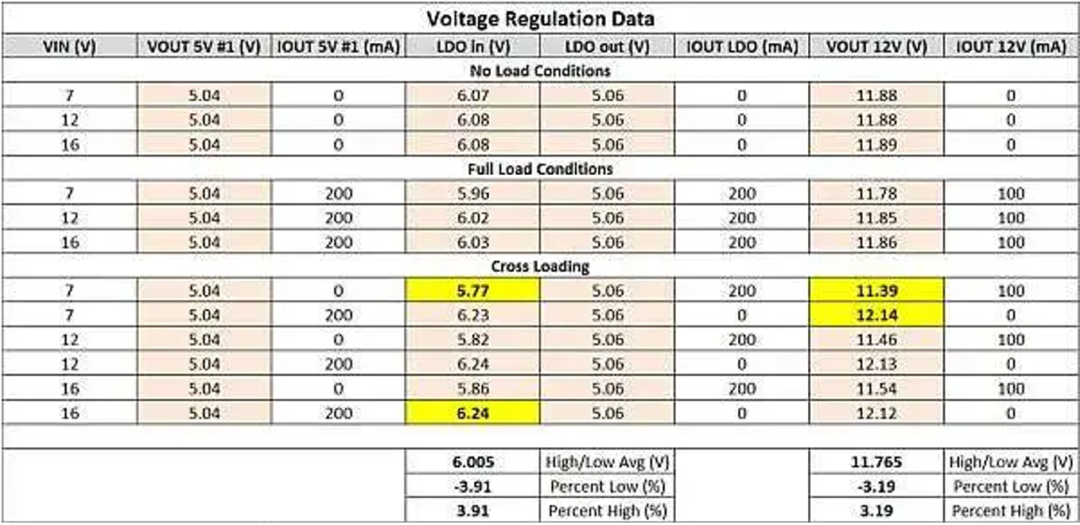

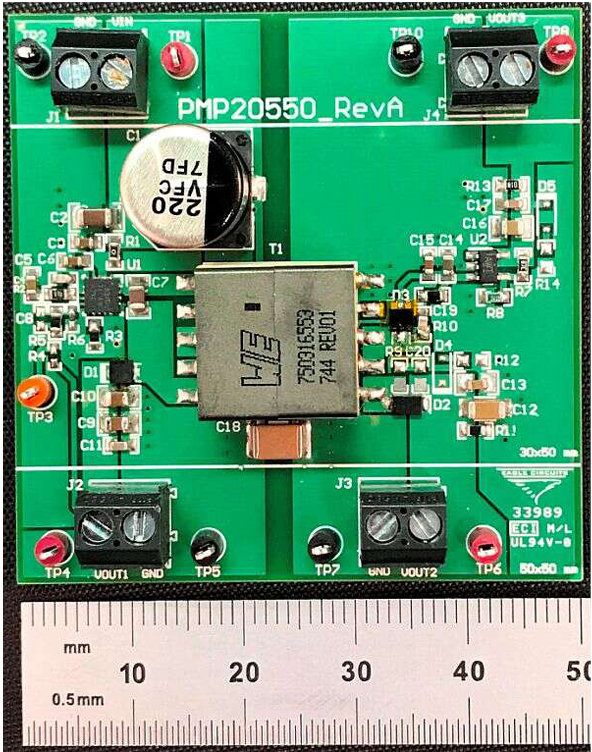

圖 3 顯示了用于獲取圖 4 中調節數據的測試電路原理圖,而圖 5 顯示了實際硬件的照片。此設計使用初級側反饋在 VOUT1 上實現穩定電壓。隔離式輸出依賴于變壓器緊密耦合和小型預負載的組合來獲得合理的電壓調節。由于線性穩壓器保持隔離式 5V 輸出恒定,因此其最小和最大輸入是首要問題。如果線性穩壓器的輸入過低,則輸出電壓會下降。相反,如果線性穩壓器的輸入過高,則將消耗過多功率。

隔離式輸出的調節數據顯示,在極端交叉負載條件下,會出現最壞情況下的最小和最大電壓。當隔離式繞組為最大負載且 VOUT1 處于空載狀態時,隔離式繞組上的電壓最小。當隔離式繞組處于空載狀態且 VOUT1 為最大負載時,隔離式繞組上的電壓最大。根據測試數據,我測得調節變化小于±4%。盡管這些結果并不代表所有設計,但這表明,類似設計可以合理實現±5%的電壓調節,而反激式更可能至少高出幾個百分點。

通過實施同步整流器,可以大大改善反激式的交叉調節。但是,這需要使用成本更高的 FET 和額外的驅動電路。您可以將相同技術應用于隔離式 SEPIC 轉換器,但用于非隔離式輸出的整流器也需要保持同步。

圖 3:具有雙路隔離式輸出的實際 SEPIC 設計

圖 4:測得的電壓調節數據

圖 5:原型電路硬件

隔離式 SEPIC 轉換器可能不是用于增加隔離式輸出電壓的首選,但與反激式轉換器相比,它對于漏電感相關振鈴的抗干擾度更高,因此可以改善輸出電壓調節性能。這樣可能無需額外進行后置調節,從而節省成本。

-

轉換器

+關注

關注

27文章

8982瀏覽量

151029 -

整流器

+關注

關注

28文章

1617瀏覽量

93346 -

晶體管

+關注

關注

77文章

9993瀏覽量

140928 -

SEPIC

+關注

關注

1文章

134瀏覽量

45472

原文標題:源來如此 | 隔離 SEPIC

文章出處:【微信號:tisemi,微信公眾號:德州儀器】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

深度解析隔離單端初級電感轉換器

深度解析隔離單端初級電感轉換器

評論