文章來源:學習那些事

原文作者:前路漫漫

本主要講解了芯片封裝中銀燒結工藝的原理、優勢、工程化應用以及未來展望。

燒結工藝

燒結是將礦粉、熔劑與燃料按照精確的配比方案進行調配,通過機械攪拌或氣流混合等方式實現均勻分散。在燃料劇烈燃燒營造的高溫環境中,部分原料發生熔化或軟化的物理變化,同時伴隨復雜的化學反應,諸如氧化物的還原、碳酸鹽的分解等。此過程中產生的液相物質在溫度下降時逐漸凝固,通過顆粒間的黏結與再結晶,最終形成致密的塊狀物體。對于兩種不同金屬而言,它們能夠在遠低于各自熔點的溫度區間,依據特定比例熔合形成共熔合金,這一臨界溫度被定義為低共熔點,其數值取決于金屬成分的相互作用。

芯片封裝燒結

在芯片封裝領域,燒結工藝作為核心互連手段,具體實施時需在芯片與載體(包括基片或管殼)之間精準置入合金焊料薄片。將組件置于真空腔室或充滿氮氣、氬氣等保護氣體的環境中,通過梯度升溫至合金的共熔點,促使焊料由固態轉變為液態。液態合金憑借表面張力與浸潤特性,迅速鋪展覆蓋芯片襯底的焊接層金屬以及載體的焊接面,形成原子級別的緊密接觸。在此期間,焊料中的活性成分與金屬表面發生擴散、溶解及化合反應,生成具有特定晶體結構的金屬間化合物。當溫度冷卻至共熔點以下,液態合金與金屬間化合物協同固化,在芯片與載體間構建起低電阻的歐姆接觸,完成高性能的電氣互連。

銀燒結技術優勢

銀燒結技術,業界又稱低溫連接技術,其性能優勢體現在多個維度:首先,燒結形成的連接層以純銀為主,具備高達 63×10? S/m 的電導率與 429 W/(m?K) 的熱導率,可有效降低互連電阻與熱阻;其次,銀的 961℃高熔點使其在長期服役中,相較熔點低于 300℃的軟釬焊材料,能規避因溫度循環引發的疲勞裂紋擴展,可靠性提升數倍;再者,燒結材料體系豐富,按銀顆粒物理形態可細分為觸變性銀漿、自支撐銀膜及流動性銀粉,按尺寸劃分為微米級(1-100μm)、納米級(1-100nm)及混合級(兼具微米骨架與納米活性);最后,銀的化學穩定性賦予其卓越的抗硫化、抗電化學腐蝕能力,配合極低的蠕變速率,確保在高溫高濕環境下仍維持連接界面的完整性。

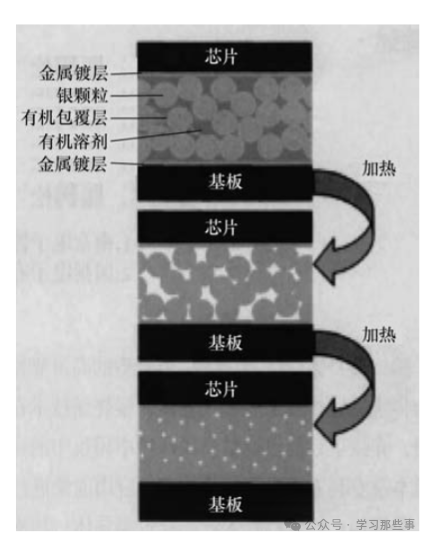

燒結原理示意圖

納米銀顆粒特性與應用困境

納米級銀顆粒因量子尺寸效應,表面原子占比激增導致熔點顯著下降,部分納米銀的初始燒結溫度可低至 150℃。處于熔融態的納米顆粒通過液相毛細力驅動,發生頸縮、融合與 Ostwald 熟化過程,最終形成具有塊體銀強度的燒結體。然而,產業化應用面臨雙重挑戰:工藝層面,傳統熱壓燒結需施加 5-50 MPa 壓力,既限制自動化產線適配性,又存在芯片碎裂風險;雖發展出無壓燒結與微波閃燒等新工藝,但 250-350℃的燒結溫度仍高于多數聚合物封裝材料的耐熱極限,無法替代 Sn-Pb 焊料的中溫工藝窗口。安全層面,納米銀顆粒(10?? m 量級)可穿透人體角質層,經皮膚吸收后可能富集于肝臟、腎臟等器官,目前缺乏完善的職業暴露防護標準,制約了其大規模工業應用。

銀燒結材料優化與機制

為抑制微米 / 納米銀顆粒的團聚傾向,常引入分散劑、黏結劑等有機添加劑構建穩定體系。在燒結過程中,有機物經歷三個階段變化:低溫段(<150℃)溶劑揮發,中溫段(150-300℃)高分子分解,高溫段(>300℃)殘余碳氧化,最終在連接層中僅留存純度>99.9% 的銀相。該技術的本質是基于銀原子的體擴散與表面擴散機制:在溫度激活下,銀原子跨越顆粒界面遷移,通過晶格重組形成冶金結合。當前研究聚焦納米銀漿的界面工程,通過表面修飾降低燒結活化能,以期實現 180℃以下的無壓互連,推動電子封裝向高集成、高可靠方向發展。

納米級銀顆粒的燒結歷程呈現出顯著的階段性特征。初始階段以顆粒間的物理接觸為起點,在原子級尺度上,銀顆粒表面活性位點相互作用形成燒結頸。此階段主導原子遷移的表面擴散機制,源于納米顆粒極高的比表面積——每單位質量的顆粒暴露著海量表面原子,這些原子因配位不飽和而具備高化學活性,自發向接觸區域匯聚,促使燒結頸緩慢生長。隨著燒結進程推進至中間階段,原子遷移模式轉向體擴散與晶界擴散。銀原子跨越顆粒內部晶格或沿晶界路徑,持續填充燒結頸區域。在此期間,顆粒間距以納米級精度逐步縮減,孤立的顆粒通過燒結頸的擴展相互連接,構建起三維貫通的孔隙網絡。該網絡結構的演變直接關聯材料性能提升:隨著原子重排與鍵合增強,燒結層密度從松散顆粒態向致密結構過渡,其力學強度與導電導熱性能呈指數級增長。燒結后期聚焦于孔隙的精細化演變。原本連續的孔洞在表面張力驅動下發生球化,隨后通過 Ostwald 熟化機制逐步縮小。這一過程中,小孔洞因曲率驅動的原子蒸氣壓差異被逐漸消除,大孔洞則持續收縮。當工藝參數匹配理想狀態時,最終形成接近理論密度的微觀結構,僅殘留亞微米級孤立孔隙。驅動這一復雜過程的能量源包含多重因素。表面能作為核心驅動力,與顆粒尺寸呈現反比關系——納米級銀顆粒因尺寸縮減至1-100 nm,其表面能密度可達塊體銀的數十倍,形成強大的熱力學驅動力。此外,外部施加的壓力、體系內的化學勢梯度以及顆粒接觸產生的局部應力場,均協同促進原子的定向遷移。這些驅動力的疊加效應,在微觀層面決定著銀原子擴散路徑與速率。

經燒結形成的連接層展現出獨特的多孔結構特性。盡管存在微米級孔隙網絡,但其導電率仍能維持純銀的90%(孔隙率10%時),熱導率提升至軟釬焊材料的3倍,熱阻降至后者的1/15。這種性能優勢在功率模塊應用中轉化為顯著的壽命提升:銀燒結互連結構的功率循環次數可達軟釬焊的2-3倍,同時層厚減少70%,有效緩解了傳統焊接工藝的熱阻瓶頸。然而,銀燒結工藝的工程化應用面臨參數調控的復雜挑戰。傳統熱壓燒結需施加40 MPa壓力,該值已接近硅芯片材料的臨界承壓能力(53.6 MPa),極易在芯片表面形成應力集中區,引發裂紋或電學性能劣化。同時,壓力維持系統與自動化產線的兼容性較差,推動了無壓燒結技術的發展。無壓工藝雖犧牲部分致密度(孔隙率略增),但憑借銀原子的自擴散特性,仍能實現優異的導電可靠性,尤其適用于小尺寸芯片與低功率密度封裝場景。

溫度參數對燒結質量的非線性影響

溫度參數對燒結質量的影響呈現非線性特征。銀漿料中的有機添加劑需經歷分階段分解:100℃以下完成溶劑揮發,200-300℃區間發生高分子鏈的氧化裂解。只有當有機物完全脫除后,銀顆粒方能建立直接冶金接觸。研究表明,在恒定壓力下,200-280℃溫度區間內剪切強度隨溫度上升顯著提高,超過該范圍后增幅趨緩。值得注意的是,不同粒徑的銀顆粒(納米級 vs 微米級)對應不同的最佳溫度窗口,需通過工藝設計精確匹配。

時間維度下的燒結動力學特征

時間維度上,燒結動力學曲線呈現典型的“S”型特征。初期幾秒至數十秒內,顆粒快速融合形成穩定骨架,剪切強度實現80%以上的增長;后續延長時間雖可繼續提升致密度,但邊際效益遞減。這種動力學特性要求工程師在可靠性與生產效率間尋求平衡——過度延長燒結時間不僅增加能耗,還可能引發界面金屬間化合物的過度生長。

表面工程在銀燒結中扮演關鍵角色。為抑制銅基底的高溫氧化,常采用“鎳阻擋層+貴金屬鍍層”的復合結構:底層鎳層(厚度0.5-2 μm)通過擴散屏障效應延緩銅原子遷移,頂層銀或金鍍層(0.1-1 μm)為銀漿提供高活性燒結界面。鍍層粗糙度需與銀顆粒尺寸精密匹配:當粗糙度Ra值控制在銀顆粒平均粒徑的1/3-1/2時,可實現最佳浸潤效果與機械嵌合。這種多尺度界面優化策略,成為突破銀燒結工藝瓶頸的核心技術路徑。

銀燒結與軟釬焊的環境工藝對比

銀燒結工藝與軟釬焊的真空回流焊在環境選擇上存在本質差異。常規銀燒結作業通常以空氣為介質,這一設定源于銀漿內部有機成分的特性——在燒結進程中,需借助氧氣參與氧化反應,促使有機物質燒蝕分解,故而對環境中的氧含量存在硬性需求。而當銀燒結工藝引入真空回流焊模式時,則依托真空燒結爐構建精密可控的氣氛環境,通過有序執行預熱、排氣、深度抽真空、梯度升溫、緩速降溫及保護性進氣等操作環節,配合定制化的溫度曲線與氣體流量控制策略,實現對燒結全過程的精準調控。

真空燒結優勢

相較于傳統焊接工藝,真空燒結技術展現出三重顯著優勢:其一,因完全摒棄助焊劑的使用,徹底規避了助焊劑殘留引發的清潔工序及潛在腐蝕風險;其二,通過抽真空手段將爐內氧含量降至極低水平,從根源上抑制金屬氧化物的生成,保障焊接界面的純凈度;其三,真空環境下,焊料內部及界面吸附的氣體在燒結完成前即沿邊緣充分逸散,確保焊接面呈現無氣泡的致密狀態。對比非真空加壓燒結工藝,二者核心分歧聚焦于焊料形態:非真空工藝依賴含豐富有機載體的銀漿體系,需經高溫氧化燒蝕完成有機物脫除;而真空工藝多采用預制焊片,其成分以金屬合金為主,無有機物揮發需求,從而簡化工藝路徑。

燒結焊料選取的一般原則

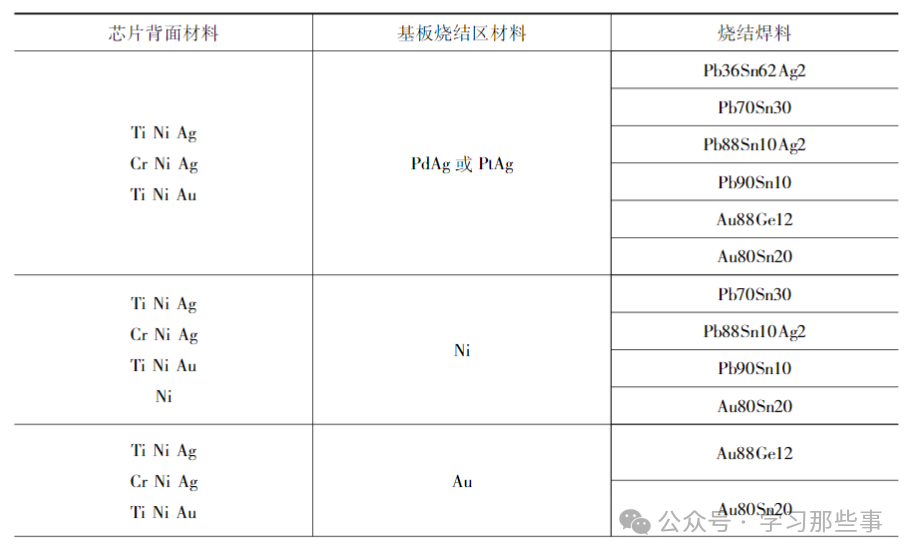

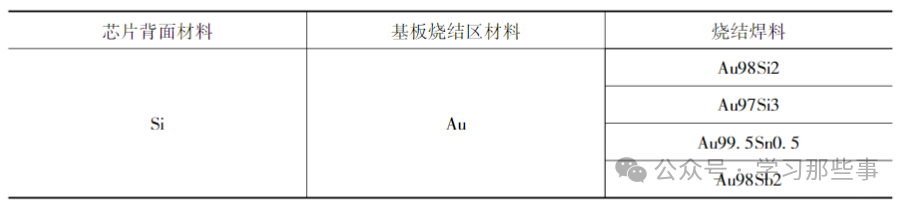

銀燒結工藝的工程化應用

燒結焊料的選型需緊密貼合應用場景特性。含銀基焊料憑借相似金屬界面的浸潤優勢,與鍍銀端面展現出良好的接合匹配性;含金、銦元素的合金焊料則對鍍金表面具備更強的親和能力;金錫合金因固有硬度高、延展性差(延伸率低)的特性,在大面積芯片焊接中易引發應力集中,適用性受限;針對背面材質為硅(Si)的芯片,優選鍍金基片作為載體,并對鍍層厚度提出量化要求(通常需≥X μm),在此場景下,金銻、金硅系焊料因熱膨脹系數匹配度高、界面反應可控,成為工藝首選。不同焊料的適配準則詳見表3-2所歸納的材質-應用對應關系矩陣。

在銀燒結工藝實踐中,工藝參數與材料狀態對成品性能存在顯著影響。統計數據顯示,芯片面積每增加10%或燒結層厚度提升5μm,剪切強度平均下降8%-12%,該現象歸因于應力分布不均與擴散路徑延長。此外,基片、載體、焊料及芯片背面的污染(如油脂、塵埃殘留)會形成擴散屏障,阻礙合金原子的跨界面遷移,導致燒結界面結合力下降。長期存放的材料(超過30天)因表面氧化層增厚(氧化物厚度>50nm),即便經預處理,殘留氧化膜仍會在焊料熔融后形成微米級空洞,降低連接層致密度。在此情境下,向爐腔引入體積分數0.5%-2%的氫氣,可通過H?+MeO→H?O+Me反應還原部分金屬氧化物,改善界面純凈度。

工藝實施層面,壓力調控是關鍵環節。在芯片表面施加1-5MPa壓力可使界面間隙從20μm縮減至5μm以下,顯著減少空洞形成。但直接施壓易造成芯片表面劃痕或裂紋(損傷概率隨壓力超2MPa呈指數上升),工程中普遍采用等面積保護硅片(厚度0.2-0.5mm)作為緩沖層,既傳遞壓力又避免直接接觸損傷。鑒于燒結過程中氣流擾動(如真空切換或氣體吹掃)可能導致芯片偏移(位移量>100μm時焊接失效),需使用高精度夾具定位。高純石墨夾具(純度>99.95%)因具備150W/(m·K)導熱率、1500℃熱穩定性及0.5%熱膨脹系數,能在維持溫度均勻性的同時提供可靠夾持力。

燒結流程遵循“預熱-保溫-冷卻”三段式曲線:預熱階段以5-10℃/min速率升至焊料共晶點以下50℃,消除濕氣與應力;保溫階段維持高于共晶點30-50℃(典型值如銀基焊料280-320℃),持續10-30min確保充分擴散;冷卻階段以8-12℃/min降至室溫。需強調的是,銀燒結并非簡單共晶過程,其微觀組織由Ag?Sn、Ag-Cu固溶體等多種金屬間化合物交織而成,經再結晶形成蜂窩狀致密結構,較傳統釬焊多出晶界強化與固溶強化機制。

質量檢測方面,因銀燒結層空洞尺寸集中于0.5-5μm,常規X光(分辨率>10μm)與超聲掃描(盲區>2μm)難以識別。目前依賴芯片推剪試驗(剪切速率0.5mm/min)量化結合力,實測數據顯示,銀燒結層抗剪強度可達80-120MPa,遠超芯片(硅基材料抗剪強度30-50MPa),導致90%以上失效模式表現為芯片本體碎裂而非焊層脫粘。

可靠性評估聚焦熱應力管理。由于硅(CTE 2.6ppm/℃)與銀(CTE 18ppm/℃)的膨脹系數差異,在-40℃至150℃循環測試中,界面熱應力可達50-80MPa。與具備10%-20%蠕變應變能力的軟釬焊料不同,銀燒結層(蠕變率<0.1%)缺乏應力緩沖,需通過材料匹配降低風險。工程實踐表明,采用CTE介于5-8ppm/℃的中間層材料(如鎢銅合金),配合仿真優化芯片-焊層-基板的疊層結構,可將熱應力峰值降低40%以上。

而燒結銀的強度較大但比較薄,不像軟釬焊料也可以有一定的蠕性形變,能吸收應力,從而使得上下表面的應力差值不那么大,而減少對芯片的損害,所以燒結銀對材料強度相對較小的硅基芯片,在使用這種工藝時要綜合考慮材料的CT匹配,從選材到結構上綜合考量,先做仿真應力計算,優選材料,包括塑封料。基于此銀燒結工藝與第三代寬禁帶半導體形成天然適配。以SiC功率模塊為例,其200℃以上工作結溫遠超硅基器件(175℃上限),而銀燒結層961℃熔點可確保長期高溫穩定性。實測數據顯示,SiC模塊經銀燒結封裝后,功率密度提升3倍,熱阻降低60%,在電動汽車OBC、光伏逆變器等場景展現出替代傳統焊接的潛力。此外,無鉛銀基材料符合RoHS標準,其250-350℃燒結溫度與現有回流焊設備兼容,進一步加速了產業應用進程。

未來展望

回溯技術演進軌跡,銀及金屬燒結工藝早期憑借超高焊接強度與穩定性,深度嵌入軍用電子高可靠封裝體系。伴隨新能源汽車功率模塊需求爆發,銀燒結技術以顛覆性優勢脫穎而出:其構建的互連層導電率達63 MS/m,熱導率突破420 W/(m·K),相較傳統釬焊實現熱阻降低80%、功率密度提升3倍。盡管當前工藝已步入產業化成熟期,設備端真空熱壓系統單臺成本超200萬元,材料側納米銀漿單價達3000元/克,較Sn-Pb焊料溢價超20倍。但技術革新正重塑成本曲線:國內團隊開發的微波閃燒結設備將能耗降低60%,納米銀粉水相合成法使原料成本下降40%。

在第三代半導體革命浪潮中,SiC器件200℃+的結溫工況與銀燒結層961℃熔點形成天然適配。

面向未來,封裝技術的競爭焦點已從單一材料性能轉向系統級協同優化。研究顯示,通過梯度熱膨脹系數設計——在芯片與基板間引入鎢銅緩沖層,可使界面熱應力降低72%。這種跨尺度材料工程思維,預示著封裝創新將邁向"性能-成本-可靠性"三維平衡的新階段。當銀燒結工藝突破設備國產化與材料規模化瓶頸,其有望重構功率半導體封裝的產業版圖。

-

工藝

+關注

關注

4文章

678瀏覽量

29308 -

焊接

+關注

關注

38文章

3402瀏覽量

61098 -

芯片封裝

+關注

關注

11文章

576瀏覽量

31313

原文標題:銀燒結

文章出處:【微信號:bdtdsj,微信公眾號:中科院半導體所】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

低溫無壓燒結銀在射頻通訊上的5大應用,除此之外,燒結銀還有哪些應用呢?歡迎補充

150℃無壓燒結銀最簡單三個步驟

芯片封裝測試流程詳解ppt

LED燈珠的生產工藝及封裝工藝

晶圓級封裝用半燒結型銀漿粘接工藝

碳化硅SiC芯片封裝:銀燒結與銅燒結設備的技術探秘

芯片封裝中銀燒結工藝詳解

芯片封裝中銀燒結工藝詳解

評論