概述

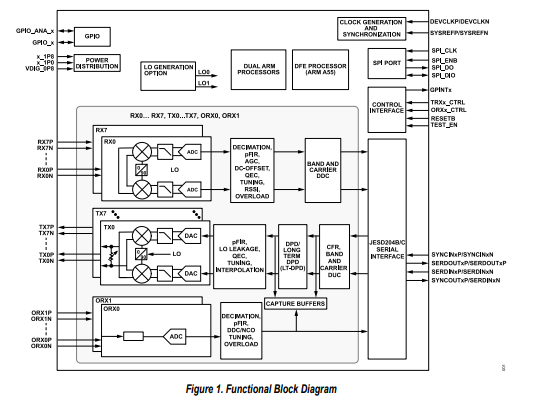

ADRV9040是一款高度集成的片上系統(tǒng)(SoC)射頻(RF)捷變收發(fā)器,配有集成式數(shù)字前端(DFE)。SoC包含8個(gè)收發(fā)器、2個(gè)用于監(jiān)測(cè)發(fā)射器通道的觀測(cè)接收器、8個(gè)接收器、集成LO和時(shí)鐘合成器,以及數(shù)字信號(hào)處理功能。SoC滿(mǎn)足蜂窩基礎(chǔ)設(shè)施應(yīng)用(包括小型蜂窩基站無(wú)線(xiàn)電、宏3G/4G/5G系統(tǒng)和大規(guī)模MIMO基站)所需的高射頻性能和低功耗。

數(shù)據(jù)表:*附件:ADRV9040具有DFE、400MHz iBW射頻收發(fā)器的8T8R SoC技術(shù)手冊(cè).pdf

Rx和Tx信號(hào)路徑采用零中頻(ZIF)架構(gòu),提供適合連續(xù)和非連續(xù)多載波基站應(yīng)用的寬帶寬和動(dòng)態(tài)范圍。ZIF架構(gòu)具有低功耗+射頻和帶寬靈活等優(yōu)點(diǎn)。由于沒(méi)有混疊和帶外圖像,因而不需要抗混疊和圖像濾波器。這樣就減小了系統(tǒng)尺寸和成本,同時(shí)支持與頻帶無(wú)關(guān)的解決方案。

該器件還包括兩個(gè)寬帶寬觀測(cè)路徑接收器子系統(tǒng),用于監(jiān)測(cè)發(fā)射器輸出。該SoC子系統(tǒng)包括自動(dòng)和手動(dòng)衰減控制、直流失調(diào)校正、正交誤差校正 (QEC) 以及數(shù)字濾波功能。此外,還集成了提供一系列數(shù)字控制選項(xiàng)的GPIO。

雙LO功能、額外的LO分頻器和寬帶寬操作支持多頻段功能。這樣就在可調(diào)諧范圍內(nèi)有4個(gè)單獨(dú)的頻帶曲線(xiàn)1,從而盡可能提高用例靈活性。

SoC具有完全集成的數(shù)字前端(DFE)功能,包括載波數(shù)字上/下變頻(CDUC和CDDC)、削峰(CFR)、數(shù)字預(yù)失真(DPD)、閉環(huán)增益控制(CLGC)和電壓駐波比(VSWR)監(jiān)控。

ADRV9040的CDUC功能對(duì)目標(biāo)頻帶內(nèi)的單獨(dú)分量載波進(jìn)行濾波和放置。CDDC功能具有8個(gè)并行路徑,對(duì)每個(gè)載波進(jìn)行單獨(dú)處理,再通過(guò)串行數(shù)據(jù)接口發(fā)送。

CDUC和CDDC降低了非連續(xù)載波配置中的SERDES接口數(shù)據(jù)速率。與基于FPGA的等效實(shí)現(xiàn)方案相比,這種集成設(shè)計(jì)還降低了功耗。

ADRV9040的CFR引擎降低了輸入信號(hào)的峰均比(PAR),支持實(shí)現(xiàn)更高效率的傳輸線(xiàn)路升級(jí),同時(shí)降低了基帶處理器的處理負(fù)荷。

SoC還包含完全集成的DPD引擎,用于功率放大器(PA)線(xiàn)性化。DPD支持高效功率放大器,可減少基站無(wú)線(xiàn)電的功耗,以及與基帶處理器接口所需的SERDES通道數(shù)量。DPD引擎包含一個(gè)長(zhǎng)期專(zhuān)用的DPD (LT-DPD)模塊,可為GaN PA提供支持。ADRV9040利用其LT-DPD模塊解決了GaN PA的電荷捕獲特性;因此改善了輻射和EVM性能。SoC包括一個(gè)ARM Cortex-A55四核處理器,可獨(dú)立提供DPD、CLGC和VSWR監(jiān)控功能。專(zhuān)用處理器與DPD引擎一起提供行業(yè)出色的DPD性能。

串行數(shù)據(jù)接口包括八個(gè)串行器通道和八個(gè)解串器通道。該接口支持JESD204B和JESD204C標(biāo)準(zhǔn),支持固定和浮點(diǎn)數(shù)據(jù)格式。浮點(diǎn)格式使內(nèi)部自動(dòng)增益控制(AGC)對(duì)基帶處理器可見(jiàn)。

ADRV9040可直接由0.8V、1.0V和1.8V穩(wěn)壓器供電,并通過(guò)一個(gè)標(biāo)準(zhǔn)SPI串行端口進(jìn)行控制。全面的節(jié)電模式可盡量降低正常使用時(shí)的功耗。該器件采用27mm × 20mm、736引腳球柵陣列封裝。

特性

- 8個(gè)差分發(fā)送器(Tx)

- 8個(gè)差分接收器(Rx)

- 2個(gè)觀察接收器(ORx)

- 單頻段和多頻段(N x 2T2R/4T4R)能力

- 可調(diào)范圍^1^內(nèi)4個(gè)波段輪廓

- 調(diào)諧范圍:650 MHz至6000 MHz

- 400MHz iBW DPD支持

- 通過(guò)硬件加速電荷捕捉糾正算法實(shí)現(xiàn)GaN PA支持

- 支持JESD204B/JESD204C數(shù)字接口

- 適用于所有LO和基帶時(shí)鐘的多芯片相位同步

- 完全集成的N部射頻頻率合成器

- 簡(jiǎn)化系統(tǒng)散熱解決方案

- 所有區(qū)塊實(shí)現(xiàn)13W功耗^2^

- 110°C最高結(jié)溫,工作溫度最高達(dá)125°^3^

- 完全集成的DFE(DPD、CDUC、CDDC、CFR)引擎,免除FPGA的需要,SERDES通道速率減半

- DPD自適應(yīng)引擎,實(shí)現(xiàn)功率放大器的線(xiàn)性化

- CDUC/CDDC——每個(gè)Tx/Rx通路最多8個(gè)分量載波(CC)

- 多級(jí)CFR引擎

- 完全集成的時(shí)鐘頻率合成器

應(yīng)用

- 3G/4G/5G TDD/FDD小型蜂窩、大規(guī)模MIMO和宏基站

功能框圖

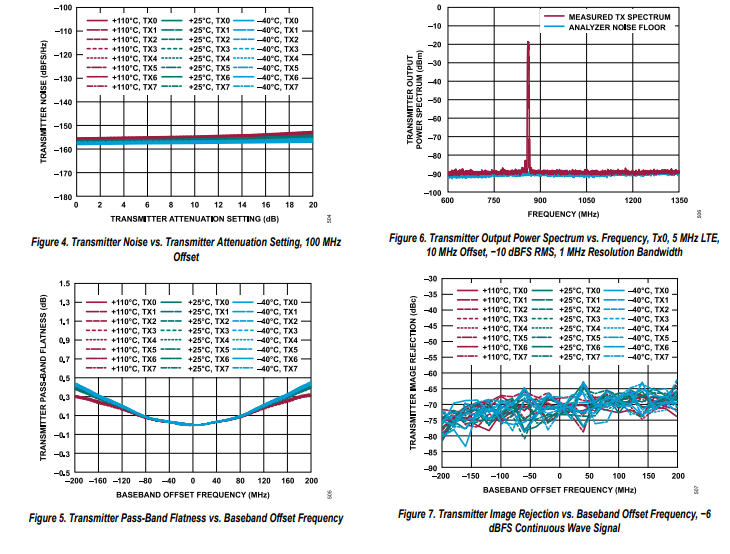

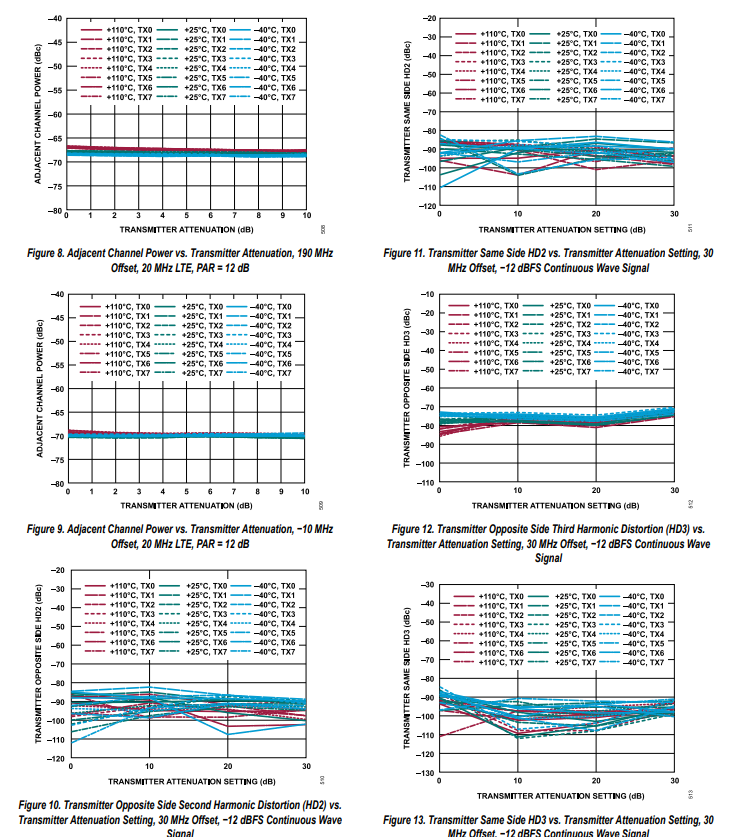

典型性能特性

850兆赫茲頻段

溫度設(shè)置指的是芯片溫度。除非另有說(shuō)明,所有本振(LO)頻率均設(shè)置為850兆赫茲 。除非另有說(shuō)明,觀測(cè)接收機(jī)測(cè)量采用5898.24兆赫茲的采樣頻率。對(duì)于衰減設(shè)置高于20分貝的接收機(jī),其線(xiàn)性度性能測(cè)量受限。

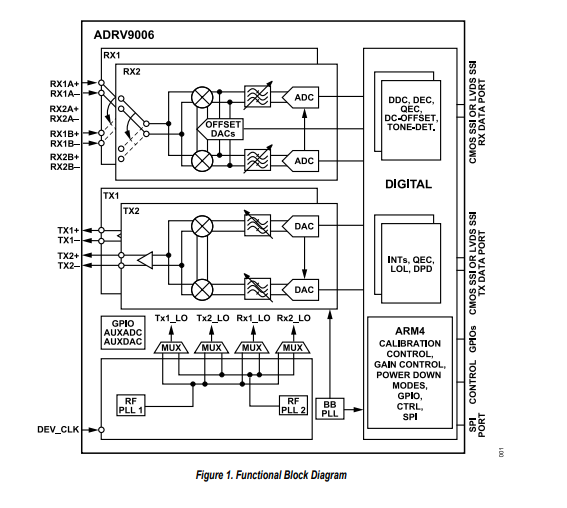

概述

ADRV9040是一款高度集成的射頻收發(fā)器,能夠針對(duì)各種應(yīng)用進(jìn)行配置。該器件集成了射頻、混頻信號(hào)和數(shù)字模塊所需的所有發(fā)射器、射頻接收器和觀測(cè)接收器功能,可在單芯片中實(shí)現(xiàn)。它符合3GPP 3G4G/5G蜂窩標(biāo)準(zhǔn),適用于時(shí)分雙工(TDD)模式。

一個(gè)觀測(cè)接收器通道監(jiān)測(cè)發(fā)射器輸出,并提供跟蹤校正功能,如直流失調(diào)、正交誤差和增益平衡。該觀測(cè)接收器通道可在各種溫度和輸入信號(hào)條件下進(jìn)行測(cè)量。固件隨器件一同提供,可實(shí)現(xiàn)初始化和校準(zhǔn)功能,無(wú)需用戶(hù)干預(yù)。此外,該器件還包括測(cè)試模式,允許系統(tǒng)設(shè)計(jì)人員在調(diào)試和優(yōu)化無(wú)線(xiàn)電配置時(shí)使用。

ADRV9040包含八個(gè)高速串行接口(SERDES)鏈路,用于發(fā)射機(jī)和觀測(cè)接收器通道之間的四對(duì)高速鏈路共享。

發(fā)射器

ADRV9040包含四個(gè)獨(dú)立的發(fā)射機(jī)通道。每個(gè)發(fā)射機(jī)通道提供數(shù)字處理、混頻信號(hào)和射頻模塊,以實(shí)現(xiàn)直接轉(zhuǎn)換系統(tǒng),同時(shí)共享一個(gè)通用頻率合成器。SERDES鏈路輸出的數(shù)字?jǐn)?shù)據(jù)通過(guò)一個(gè)數(shù)字處理模塊,該模塊包括可編程半帶濾波器、插值級(jí)和射頻濾波器,以及可編程FIR濾波器,其變量間隔采樣率可達(dá)24倍。

數(shù)字輸出連接到數(shù)模轉(zhuǎn)換器(DAC),DAC采樣率為244.140625 MSPS或389.3616 MHz。在同相(I)和正交(Q)通道中,在基帶混頻器信號(hào)鏈中執(zhí)行數(shù)字校正。

混頻轉(zhuǎn)換后,I和Q信號(hào)經(jīng)過(guò)濾波,以消除采樣偽影,并饋送到上變頻混頻器。每個(gè)發(fā)射機(jī)提供一個(gè)寬衰減調(diào)整范圍,以幫助設(shè)計(jì)人員優(yōu)化信號(hào)與噪聲比(SNR)。

接收器

ADRV9040包含四個(gè)獨(dú)立的接收器通道。每個(gè)通道包含接收射頻信號(hào)并將其轉(zhuǎn)換為數(shù)字?jǐn)?shù)據(jù)所需的所有模塊,該數(shù)字?jǐn)?shù)據(jù)由基帶處理器進(jìn)行后續(xù)處理。每個(gè)接收器提供I和Q混頻器,以將接收到的信號(hào)下變頻至基帶進(jìn)行數(shù)字化。

有兩種增益控制選項(xiàng),如下所示:

- 用戶(hù)可以使用其基帶處理器實(shí)現(xiàn)自己的增益控制算法,采用手動(dòng)增益控制模式。

- 用戶(hù)可以使用片上AGC(自動(dòng)增益控制)。

通過(guò)將每個(gè)增益控制設(shè)置映射到特定的衰減級(jí)別,在接收信號(hào)路徑中優(yōu)化性能。此外,每個(gè)通道獨(dú)立執(zhí)行信號(hào)功率測(cè)量功能。直流失調(diào)跟蹤和所有通道的連續(xù)測(cè)量用于自動(dòng)校準(zhǔn)。

接收器包括模數(shù)轉(zhuǎn)換器(ADC)和可調(diào)節(jié)采樣率,可從先進(jìn)先出(FIFO)緩沖器接收信號(hào)。這些設(shè)置可以通過(guò)串行端口接口(SPI)進(jìn)行配置。

抽取濾波器由數(shù)字濾波器塊實(shí)現(xiàn)。通過(guò)改變數(shù)字濾波器塊的系數(shù)來(lái)調(diào)整抽取率,以產(chǎn)生所需的輸出數(shù)據(jù)速率。所有接收器輸出都連接到SERDES模塊,在那里進(jìn)行格式化和串行化,以便傳輸?shù)交鶐幚砥鳌?/p>

觀測(cè)接收器

ADRV9040提供獨(dú)立的觀測(cè)接收器輸入。與接收器通道不同,觀測(cè)接收器通道采用直接采樣。射頻ADC消除了對(duì)本地振蕩器(LO)的需求,該本地振蕩器通常具有緩沖級(jí)。該通道包含一個(gè)可編程衰減器,在模擬域中提供約16 dB的衰減。

參考時(shí)鐘輸入

ADRV9040需要連接到器件的兩個(gè)不同時(shí)鐘。時(shí)鐘輸入必須在61.44 MHz和491.52 MHz之間,因?yàn)樵撔盘?hào)會(huì)生成射頻本地振蕩器(LO)和內(nèi)部采樣時(shí)鐘。

合成器

ADRV9040包含多個(gè)分?jǐn)?shù)N分頻鎖相環(huán)(PLL),用于生成信號(hào)路徑的射頻本地振蕩器(LO)和所有內(nèi)部時(shí)鐘源。該組PLL包括兩個(gè)射頻PLL、兩個(gè)SERDES PLL、一個(gè)內(nèi)部時(shí)鐘PLL和一個(gè)系統(tǒng)時(shí)鐘PLL。每個(gè)PLL都可獨(dú)立控制,因此無(wú)需外部合成器來(lái)設(shè)置頻率。

射頻合成器

兩個(gè)射頻合成器使用分?jǐn)?shù)N分頻PLL生成多個(gè)接收器和發(fā)射器通道的射頻本地振蕩器(LO)。分?jǐn)?shù)N分頻壓控振蕩器(PLL)結(jié)合了四芯內(nèi)部電壓控制振蕩器(VCO)和環(huán)路濾波器,能夠生成低相位噪聲信號(hào),而無(wú)需外部組件。多個(gè)器件上的射頻本地振蕩器(LO)可以進(jìn)行相位同步,以支持有源天線(xiàn)系統(tǒng)和波束成形應(yīng)用。

SERDES合成器

SERDES合成器使用單芯VCO分?jǐn)?shù)N分頻PLL來(lái)生成SERDES物理層所需的時(shí)鐘速率。

-

soc

+關(guān)注

關(guān)注

38文章

4392瀏覽量

222810 -

RF

+關(guān)注

關(guān)注

65文章

3175瀏覽量

169011 -

射頻收發(fā)器

+關(guān)注

關(guān)注

4文章

264瀏覽量

25831

發(fā)布評(píng)論請(qǐng)先 登錄

RadioVerse生態(tài)系統(tǒng)中的寬帶收發(fā)器分享!

ADRV9010:集成四路射頻收發(fā)器,帶觀察路徑數(shù)據(jù)表

ADRV9004:雙窄/寬帶射頻收發(fā)器初步數(shù)據(jù)表

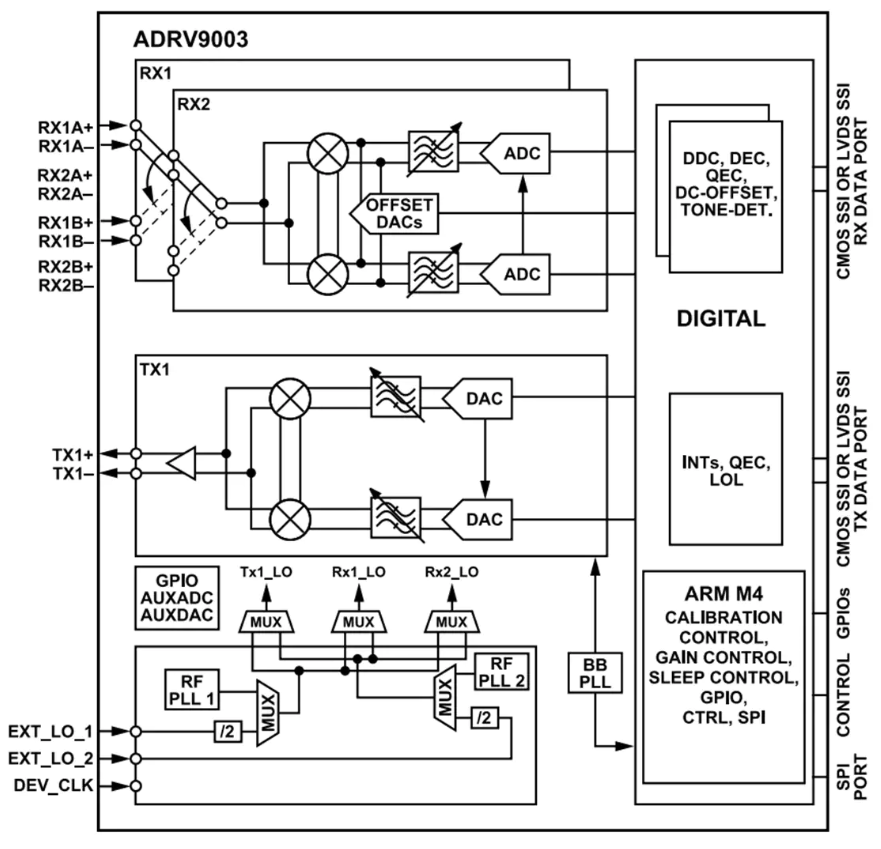

ADRV9003:窄帶/寬帶射頻收發(fā)器初步數(shù)據(jù)表

ADRV9029:集成四路射頻收發(fā)器,帶觀察路徑數(shù)據(jù)表

ADRV9026:集成四路射頻收發(fā)器,帶觀察路徑數(shù)據(jù)表

ADRV9002:雙窄/寬帶射頻收發(fā)器初步數(shù)據(jù)表

ADRV9002射頻收發(fā)器英文手冊(cè)

具有800MHz IBW LTE的射頻采樣DAC

74AVC8T245-Q100具有可配置電壓轉(zhuǎn)換的8位雙電源轉(zhuǎn)換收發(fā)器規(guī)格書(shū)

74AVC8T245具有可配置電壓轉(zhuǎn)換的8位雙電源轉(zhuǎn)換收發(fā)器規(guī)格書(shū)

ADI ADRV9040 具有數(shù)字前端DFE、400MHz iBW射頻收發(fā)器的8T8R SoC

ADRV9006雙通道窄帶和寬帶RF收發(fā)器技術(shù)手冊(cè)

Analog Devices Inc. ADRV9003窄帶/寬帶射頻收發(fā)器數(shù)據(jù)手冊(cè)

ADRV9040具有DFE、400MHz iBW射頻收發(fā)器的8T8R SoC技術(shù)手冊(cè)

ADRV9040具有DFE、400MHz iBW射頻收發(fā)器的8T8R SoC技術(shù)手冊(cè)

評(píng)論