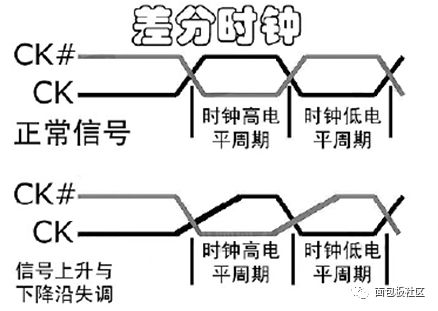

關鍵技術之一:差分時鐘

差分時鐘是DDR的一個非常重要的設計,是對觸發時鐘進行校準,主要原因是DDR數據的雙沿采樣。由于數據是在時鐘的上下沿觸發,造成傳輸周期縮短了一半,因此必須要保證傳輸周期的穩定以確保數據的正確傳輸,這就對CK的上下沿間距有了精確的控制的要求。

一般說來,因為溫度、電阻性能的改變等原因,CK上下沿間距可能發生變化,此時與其反相的CK#就起到糾正的作用,因為,CK上升沿快下降沿慢,CK#則是上升沿慢下降沿快。也就是,與CK反相的CK#保證了觸發時機的準確性。

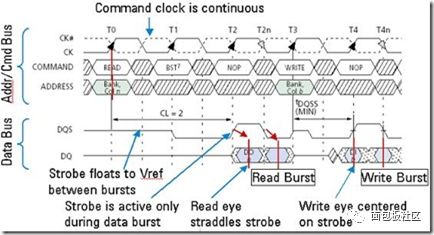

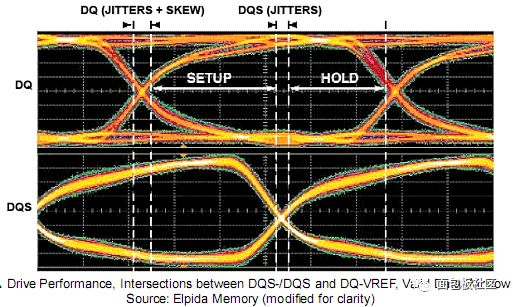

關鍵技術之二:數據選取脈沖(DQS)

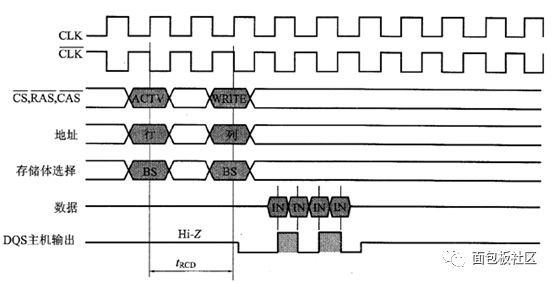

DQS是DDR SDRAM中的另一項關鍵技術,它的功能是用來在一個時鐘周期內準確的區分出每個傳輸周期,并便于接收方準確接收數據。每一顆芯片都有一個DQS信號線,它是雙向的,在寫入時它用來傳送由芯片發來的DQS信號,讀取時,則由內存生成DQS向芯片發送。因此可以認為DQS就是數據的同步信號。

我們知道DDR之前的SDR就是使用clock來同步的,因此理論上,DQ的讀寫時序完全可以由clock來同步。但是,由于速度提高之后,可用的時序余量越來越小,而引入DQS是為了降低系統設計的難度和可靠性,也就是可以不用考慮DQ和clock之間的直接關系,只用分組考慮DQ和DQS之間的關系,很容易同組同層處理。

DQ和DQS只是組成了源同步時序的傳輸關系,可以保證數據在接收端被正確的所存,但是IC工作時,內部真正的同步時鐘是clock而不是DQS,數據要在IC內部傳輸存儲同樣需要和clock(內部時鐘比外部時鐘慢)去同步,所以就要求所有的DQ信號還是同步的,而且和clock保持一定的關系,所以就要控制DQS和clock之間的延時了。

在寫入時,以DQS的高/低電平期中部為數據周期分割點,而不是上/下沿,但數據的接收觸發仍為DQS的上/下沿。

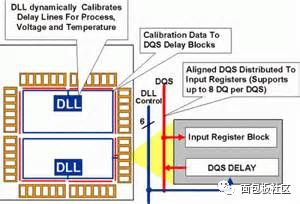

關鍵技術之三:延遲鎖定回路(DLL)

第三個關鍵技術是DLL技術,也就是延遲鎖定回路。需要這種技術的原因是,內外時鐘的不同步問題。內外時鐘不同步在SDRAM中就存在了,不過因為它的工作/傳輸頻率較低,所以內外同步問題并不突出。

但是,DDR SDRAM對時鐘的精確性有著很高的要求,而DDR SDRAM有兩個時鐘,一個是外部的總線時鐘,一個是內部的工作時鐘,在理論上DDR SDRAM這兩個時鐘應該是同步的,但由于種種原因,比如溫度、電壓波動而產生延遲使兩者很難同步,更何況時鐘頻率本身也有不穩定的情況。我們熟悉的DDR SDRAM的tAC就是因為內部時鐘與外部時鐘有偏差而引起的,它很可能造成因數據不同步而產生錯誤。

怎么解決呢?實際上,因為不同步就是一種正/負延遲,如果延遲不可避免,那么若是設定一個延遲值,如一個時鐘周期,那么內外時鐘的上升與下降沿還是同步的。鑒于外部時鐘周期也不會絕對統一,所以需要根據外部時鐘動態修正內部時鐘的延遲來實現與外部時鐘的同步,這就是DLL的任務。

DLL主要的目的就是生成一個延遲量給內部時鐘,來補充正負不同步造成的正負延遲。

有了這些技術就構成了內存帝國的最基本的元素,之后的DDR2,DDR3和DDR4以及即將推出的DDR5將以此為基礎,內存的功耗及頻率得到一次又一次的飛躍。

-

dll

+關注

關注

0文章

116瀏覽量

46207 -

DDR

+關注

關注

11文章

732瀏覽量

66857 -

內存

+關注

關注

8文章

3125瀏覽量

75294

原文標題:DDR的概念解讀-三大關鍵技術

文章出處:【微信號:gh_bee81f890fc1,微信公眾號:面包板社區】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

關于DDR的三大關鍵技術解析

關于DDR的三大關鍵技術解析

評論