NavisPro層次化SoC設計規(guī)劃方案

產(chǎn)品簡介

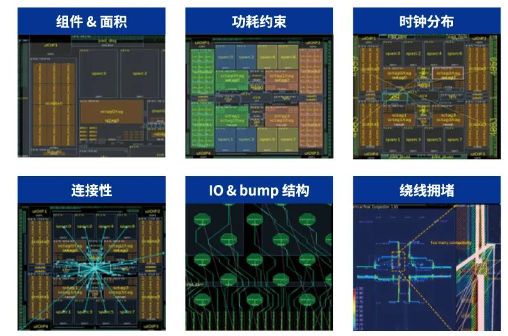

NavisPro可提供整體性設計規(guī)劃解決方案,支持在RTL設計階段完成芯片評估和布局規(guī)劃,幫助芯片設計師在布局規(guī)劃早期階段預測并預防物理實現(xiàn)問題。

RTL布局規(guī)劃是SoC設計物理實現(xiàn)過程的第一步,NavisPro同時支持top-down和bottom-up設計方法,與傳統(tǒng)的子系統(tǒng)劃分和芯片級整合流程一致。

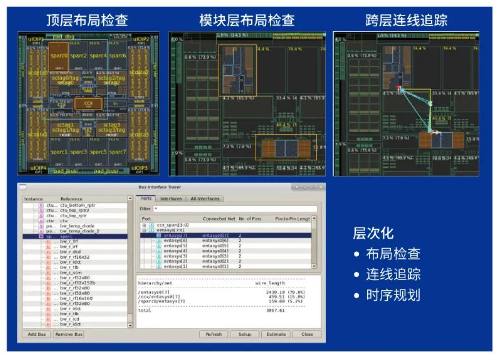

層次化布局設計方法解決了SoC設計的復雜性問題。NavisPro支持交互式物理層次劃分和每一個子系統(tǒng)pin的自動布局,pin的分布作為子系統(tǒng)版圖的關鍵約束,直接決定了全芯片繞線擁堵的范圍。

此外,準確評估子系統(tǒng)之間的總線互連時序?qū)τ跁r序收斂至關重要。NavisPro提供不同設計層次之間的net跟蹤功能,不同層次之間互聯(lián)net的時序估算對芯片級時序評估非常關鍵。

產(chǎn)品優(yōu)勢

·經(jīng)業(yè)界驗證的SoC設計規(guī)劃解決方案

·多層次設計規(guī)劃(RTL/Gate/Blackbox)

·靈活的設計抽象管理

·豐富而實用的功能方便解決實際工程問題

·自動區(qū)塊引腳分配和總線互連規(guī)劃

·獨立RTL設計規(guī)劃解決方案

·輸入數(shù)據(jù)設置省時省力

·大幅減少設計選代次數(shù)從而縮短設計周期

技術規(guī)格

·以約束驅(qū)動的RTL布局規(guī)劃

-Bump陣列構造

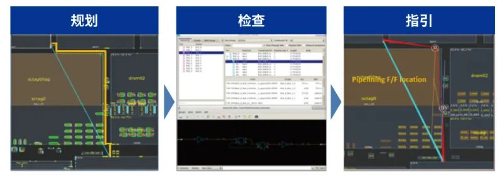

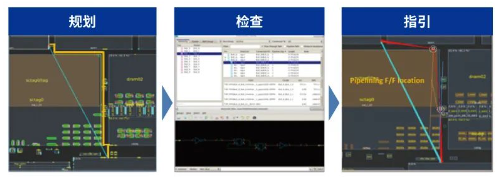

-總線互連探查

-互連延遲估算

-自動化pipeline寄存器布局

-全局繞線擁堵分析

-自動和手動pin分配

-Block布局/形狀和芯片面積評估

·設計和約束探索

-RTL設計探索

-低功耗設計探索

-時鐘樹結構探索

·靈活的top-down和bottom-up布局規(guī)劃

產(chǎn)品應用

·RTL芯片評估

·RTL布局規(guī)劃

應用實例

以約束驅(qū)動的RTL布局規(guī)劃

總線互連規(guī)劃

總線互連規(guī)劃

層次化布局規(guī)劃

-

芯片

+關注

關注

459文章

52355瀏覽量

438757 -

soc

+關注

關注

38文章

4363瀏覽量

222194 -

SoC設計

+關注

關注

1文章

151瀏覽量

19142 -

RTL

+關注

關注

1文章

389瀏覽量

60903 -

概倫電子

+關注

關注

1文章

112瀏覽量

9018

原文標題:層次化SoC設計規(guī)劃方案 - NavisPro

文章出處:【微信號:khai-long_tech,微信公眾號:概倫電子Primarius】歡迎添加關注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

打造EDA全流程解決方案,概倫電子收購博達微

微捷碼發(fā)布增強版層次化設計規(guī)劃解決方案

Magma推出面向大型SoC的增強版層次化設計規(guī)劃解決方案

EDA企業(yè)概倫電子擬科創(chuàng)板上市

EDA企業(yè)概倫電子啟動科創(chuàng)板輔導

概倫電子精準高效標準單元庫EDA解決方案NanoCell

概倫電子NanoDesigner產(chǎn)品的技術優(yōu)勢

EDA上云,概倫電子攜手鴻之微開啟芯片設計加速度

概倫電子與阿里云深化合作加速推動EDA上云

概倫電子攜半導體參數(shù)測試與全自動解決方案即將亮相SEMICON CHINA

概倫電子亮相第61屆電子設計自動化盛會DAC

概倫電子2024年度榮譽盤點

概倫電子邀您相約SEMICON CHINA 2025

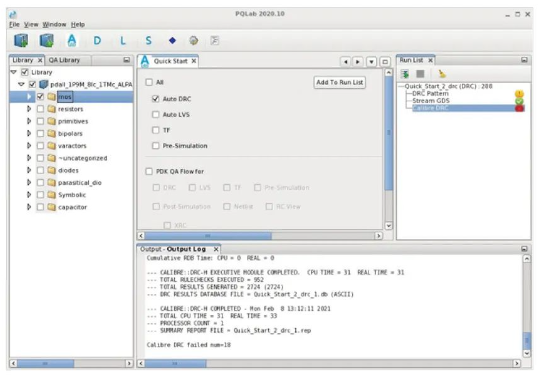

概倫電子先進PDK驗證平臺PQLab介紹

概倫電子層次化SoC設計規(guī)劃方案NavisPro介紹

概倫電子層次化SoC設計規(guī)劃方案NavisPro介紹

評論