來源:數字站

本文參考B站尤老師JESD204B視頻,圖片來自JESD手冊或者ADI/TI官方文檔。

01對比LVDS與JESD204

JESD204B是邏輯器件和高速ADC/DAC通信的一個串行接口協議,在此之前,ADC/DAC與邏輯器件交互的接口大致分為如下幾種。

低速串行接口(I2C、SPI)、低速并行接口(包含時鐘信號和并行數據信號,例如AD9226、AD9280等)、LVDS接口(在低速并行接口的基礎上將數據線和時鐘線變為差分信號,速度可以達到幾百MHz)、最后演變為JESD204高速串行總線。

前兩種接口的ADC和DAC比較常見,不管是單片機還是FPGA,都使用的比較多,不再贅述。接下來講解LVDS接口的劣勢,為什么高速ADC會演變為JESD204。

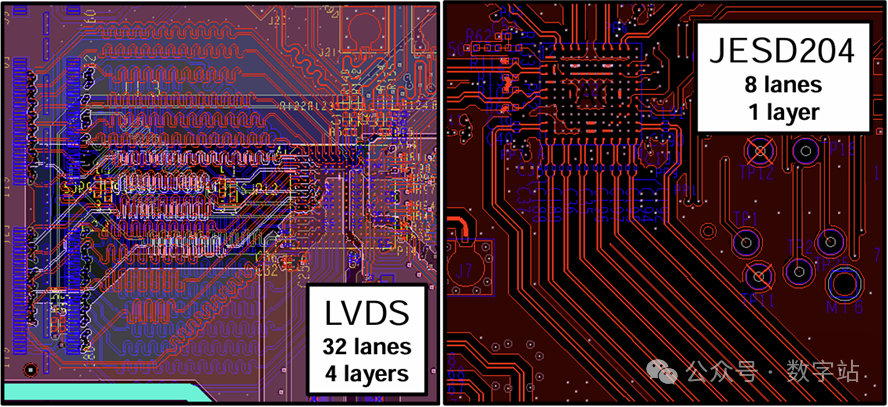

首先是PCB布局布線的難度,如下所示,相同的16位DAC,LVDS接口需要使用16對差分數據線,而JESD204B接口只需要使用4對差分線(帶寬與LVDS接口一致)。

圖1 數據線的差別

上述兩種接口的PCB布線如下所示,由于數據線之間還要嚴格等長,LVDS需要使用4層布線,而JESD204B只需要一層布線即可。

圖2 PCB布線

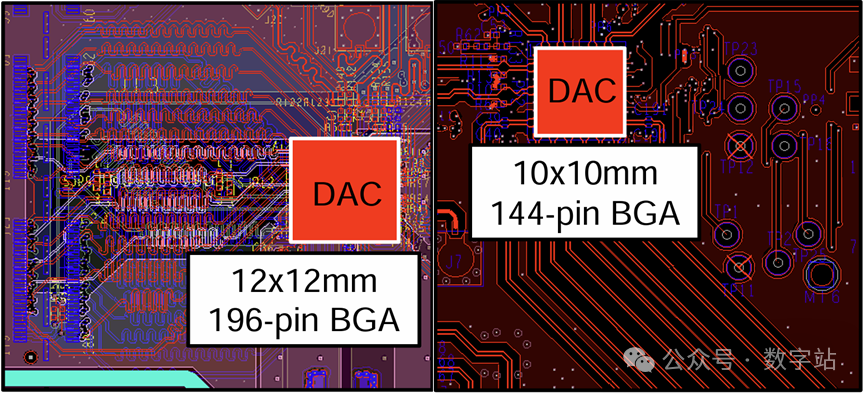

同時由于芯片數據引腳減少,芯片的尺寸也可以做得更小,縮減PCB的面積,如下所示。

圖3 芯片面積縮小

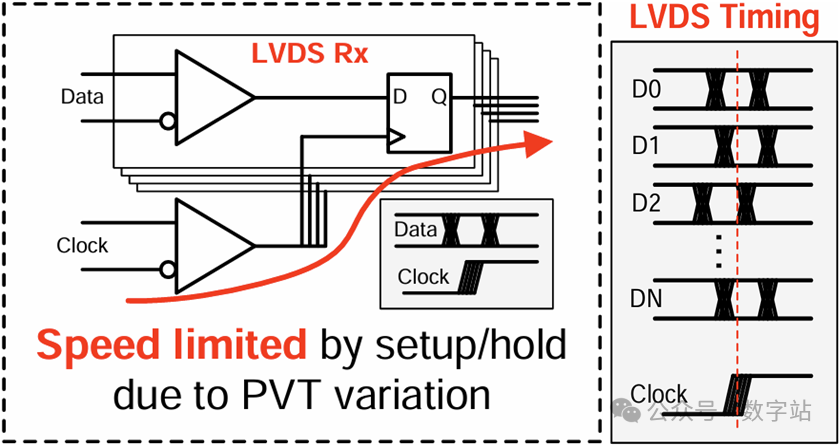

LVDS接口的時序如下圖所示,在時鐘信號的邊沿采集并行數據總線的狀態,容易引起信道偏斜。要求各數據線之間嚴格等長,在時鐘邊沿能夠穩定采集所有數據線的狀態,在使用LVDS接口的器件時,一般都需要去通過idelaye去調節時鐘和數據線的相位關系。

但如果數據線之間本身就沒有對齊,當時鐘頻率較高時,整個系統很可能調試不出結果。鐘頻率越高,數據線對齊的要求越嚴格,時鐘頻率增加到某些值時,PCB走線可能已經無法完成對齊。

圖4 LVDS接口的時序

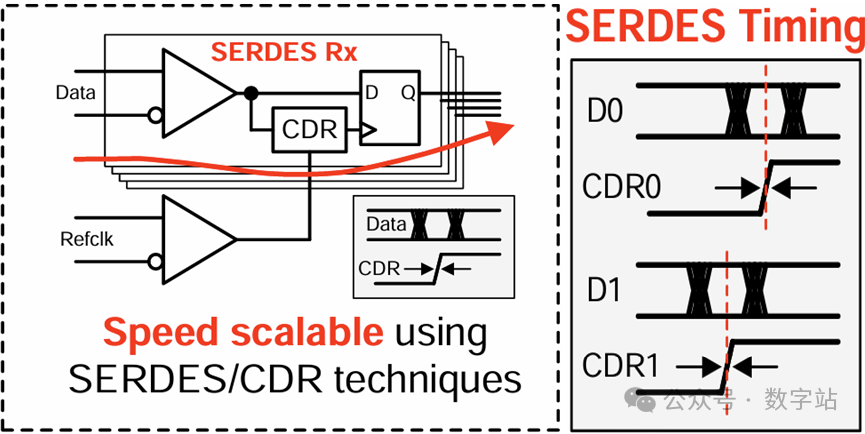

JESD204接口是在高速Serdes的基礎上封裝得到的,因此數據傳輸的原理是一樣的。如下圖所示,JESD204接口并沒有隨路時鐘信號,接收端通過CDR技術去調節參考時鐘和數據之間的相位關系,每路串行數據均有對應CDR,各組數據線的PCB走線之間不需要等長對齊。

圖5 JESD204接口接收數據時序

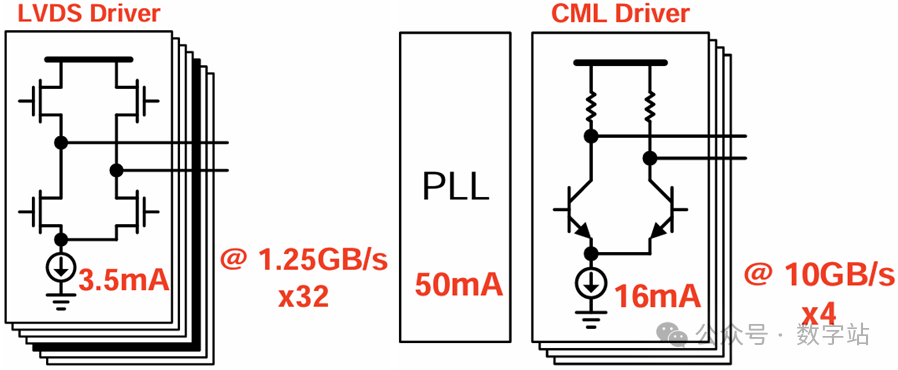

當然JESD204相對于LVDS也是有劣勢的,JESD204并不能取代LVDS。由于JESD204的接收端需要鎖相環給CDR提供參考時鐘,因此JESD204的功耗一般會比LVDS高。

圖6 JESD204與LVDS接口功耗

另外JESD204的接收端有緩沖器來實現多通道數據同步,數據傳輸延遲也會比LVDS大很多,因此在一些對延時比較敏感的系統中,可能還是得使用LVDS。

02JESD204的結構

JESD204從發布開始至今有四個版本,分別為JESD204、JESD204A、JESD204B、JESD204C,目前使用最多的是JESD204B,各個版本之間的差異如下所示。

表1 各個版本的功能

| 功能 | JESD204 | JESD204A | JESD204B | JESD204C |

|---|---|---|---|---|

| 線速率(Gbps) | 3.125 | 3.125 | 12.5 | 34.25 |

| 多lane | 不支持 | 支持 | 支持 | 支持 |

| 多lane同步 | 不支持 | 支持 | 支持 | 支持 |

| 多器件同步 | 不支持 | 支持 | 支持 | 支持 |

| 確定性延時 | 不支持 | 不支持 | 支持 | 支持 |

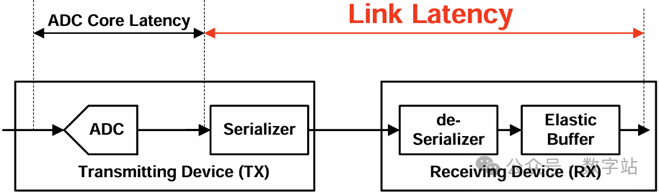

其中支持確定性延遲是JESD204B的特點,JESD204B鏈路的確定性延遲定義為串行數據從發送器(ADX或FPGA)的并行幀數據輸入傳播至接收器(DAC或接收端FPGA)并行幀數據輸出所需的時間。

圖7 鏈路延遲

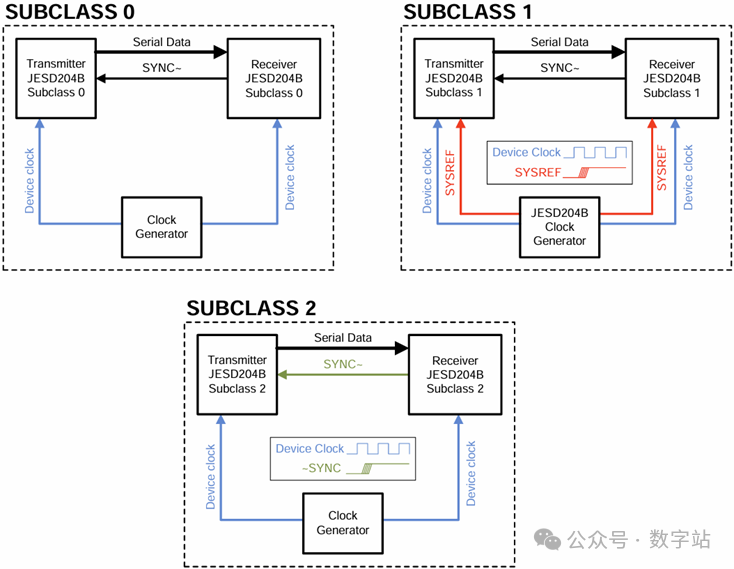

JESD204包含3種工作模式,如下所示。其中子類0是JESD204A的工作模式,不支持確定性延遲。子類1通過sysref和sync實現確定性延遲,子類2通過sync實現確定性延遲。子類1的結構最為復雜,也是JESD204B使用最廣泛的模式。

圖8 子類的連接方式

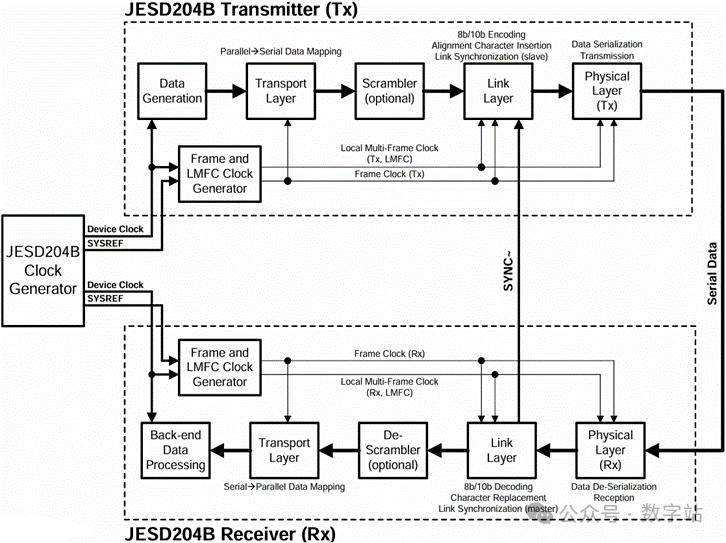

子類1的框圖如下所示,時鐘芯片同時給發送端和接收端提供sysref和Device Clock,接收端和發送端通過sysref去產生與Device Clock同步的幀時鐘和多幀時鐘LMFC。在鏈路建立階段接收端通過拉低SYNC信號,去同步多lane數據,具體細節在后文的JESD204B確定性延遲章節進行講解。

圖9 子類1的結構

上圖的發送端可以是ADC或者FPGA,接收端可以是FPGA或者DAC,從而實現ADC或者DAC與FPGA的數據傳輸。不管是發送端還是接收端,主要包含Transport Layer、Scrambler、Link Layer、Physical Layer等幾部分。

物理層包含了完成高速并/串轉換的SDRDES 模塊,時鐘及時鐘數據恢復模塊(CDR),也規定了接口的物理電器特性如下表所示。

表2 接口的物理電器特性

| 參數 | LV-OIF-Sx15 | LV-OIF-6G-SR | LV-OIF-11G-SR |

|---|---|---|---|

| 線速率 | 312.5M~3.125Gbps | 312.5M~6.375Gbps | 312.5M~12.5Gbps |

| 差分電壓 | 500~1000 (mV) | 400~750 (mV) | 360~770 (mV) |

| 誤碼率 | ≤ 1e-12 | ≤ 1e-15 | ≤ 1e-15 |

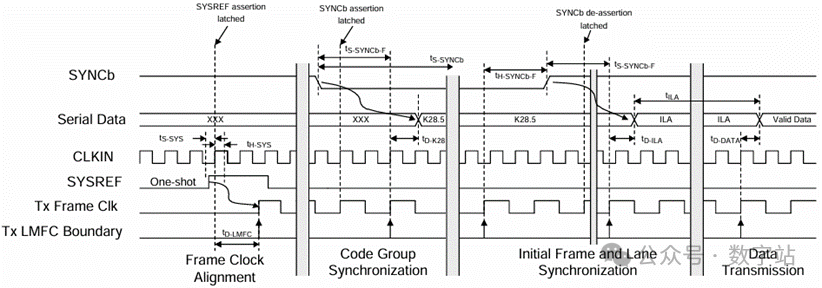

Link Layer主要包括8B10B編解碼、數據鏈路的建立(幀和通道對齊)、使用符號位鏈路監控。鏈路建立的過程如下所示,具體實現在后文與確定性延時一起講解。

圖10 鏈路建立

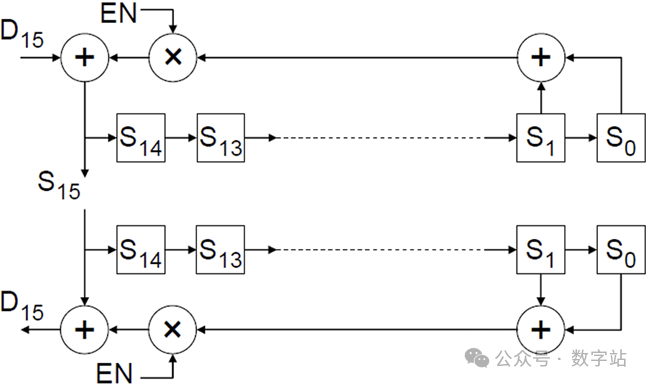

加擾(Scrambler) 用于去除數據相關性,例如各個幀同時發送相同的數據,從而減小造成的系統干擾和減小電磁兼容性問題。加擾多項式為X15+X14+1,對應框圖如下所示。

圖11 加擾多項式

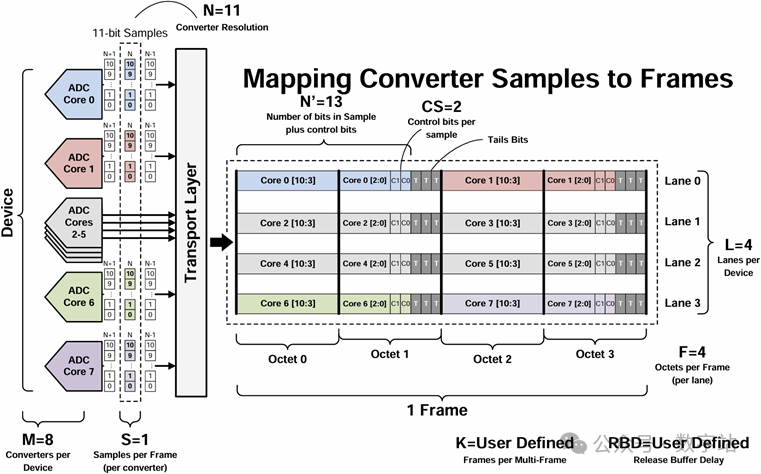

傳輸層(Transport Layer)的功能是將AD/DA的采集到的數據映射到非擾碼的八字結的過程。如下圖是一個傳輸層,需要理解一些參數的含義。

L:每顆ADC或者DAC芯片的高速收發器數量。

M:每顆芯片包含ADC或DAC通道數量。

F:每個高速收發器的每個frame包含幾個字節的數據。

S:每個frame周期內芯片的采樣點個數。

CS:每個采樣點含有多少bit控制位。

圖12 傳輸層

上圖表示該芯片包含8路(M=8)分辨率為11(N=11)的ADC,8路ADC的數據通過4路(L=4)高速收發器傳輸,每個采樣點包含2位(CS=2)控制位。

ADC每個采樣點的數據需要經過兩個時鐘才能輸出,因此在計算高速收發器線速率時,ADC分辨率其實可以等效為16位。

假設ADC采樣率為X,則單個時鐘ADC的采樣數據為XM16bit,然后需要經過8B10B編碼,編碼后的數據量為(XM16)/0.8bit = XM20bit,最后通過4路高速收發器輸出,每路高速收發器的線速率為XM20/4 = XM5bps。

當采樣率為100MHz時,每路收發器線速率為100M85=4000Mbps。

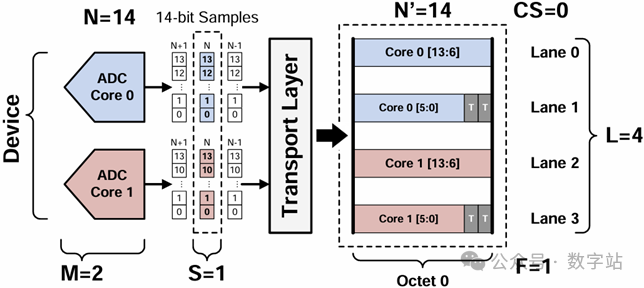

ADS42JB49的傳輸層如下圖所示,2路14位ADC通過4路高速收發器傳輸數據,通過上述方式計算每路高速收發器線速率為X216/0.8/4=X*10bps。

圖13 ADS42JB49的傳輸層

下文著重講解JESD204B子類1的數據鏈路建立過程和確定性延時相關知識。

-

adc

+關注

關注

99文章

6608瀏覽量

547666 -

lvds

+關注

關注

2文章

1076瀏覽量

66857 -

高速接口

+關注

關注

1文章

55瀏覽量

14906 -

JESD204B

+關注

關注

5文章

79瀏覽量

19453

原文標題:初始JESD204B高速接口協議(JESD204B一)

文章出處:【微信號:HXSLH1010101010,微信公眾號:FPGA技術江湖】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

JESD204B的系統級優勢

JESD204B串行接口時鐘的優勢

FPGA高速數據采集設計之JESD204B接口應用場景

FPGA高速數據采集設計之JESD204B接口應用場景

如何讓JESD204B在FPGA上工作?FPGA對于JESD204B需要多少速度?

JESD204B協議有什么特點?

JESD204B協議介紹

JESD204B的優勢

JESD204B協議概述

基于JESD204B高速數據傳輸協議 通過DDC魔法乘以ADC的虛擬通道數

JESD204B SystemC module 設計簡介(一)

一文詳解JESD204B高速接口協議

一文詳解JESD204B高速接口協議

評論