01.引言

在當今快速發展的數字時代,高速傳輸已成為電子設備的基本要求。隨著數據傳輸速率的不斷提升,信號完整性(Signal Integrity,簡稱SI)問題變得越來越重要。信號完整性是高速互連系統設計的基石,高速系統的信號完整性直接關系到數據傳輸的可靠性和系統的整體性能。因此,深入理解信號完整性的基本原理和測試方法對于確保高速系統的穩定運行至關重要。

02.信號完整性基本概念

1信號完整性的定義

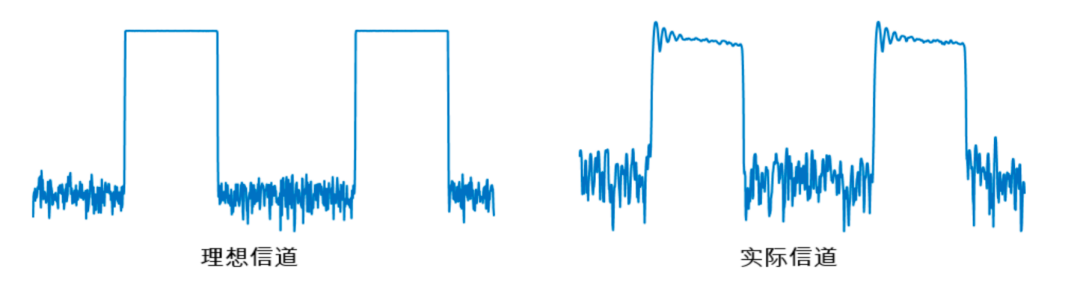

信號完整性(Signal Integrity,SI)是指一個信號在電路中產生正確的響應的能力。在長距離、高比特率的信號傳輸中,由于多種效應的影響,信號的可信度會降低。因此,高速互連系統里的數據傳輸對信號完整性的要求越來越高。

2信號完整性測試的重要性

在高速數據傳輸中,信號完整性測試的重要性不言而喻。如果信號在傳輸過程中出現問題,如衰減、反射、失真等,將會導致數據傳輸錯誤,甚至系統崩潰。因此,通過信號完整性測試,可以確保信號在傳輸過程中保持正確的形態和幅度,從而提高數據傳輸的可靠性和穩定性。

3影響信號完整性的核心因素

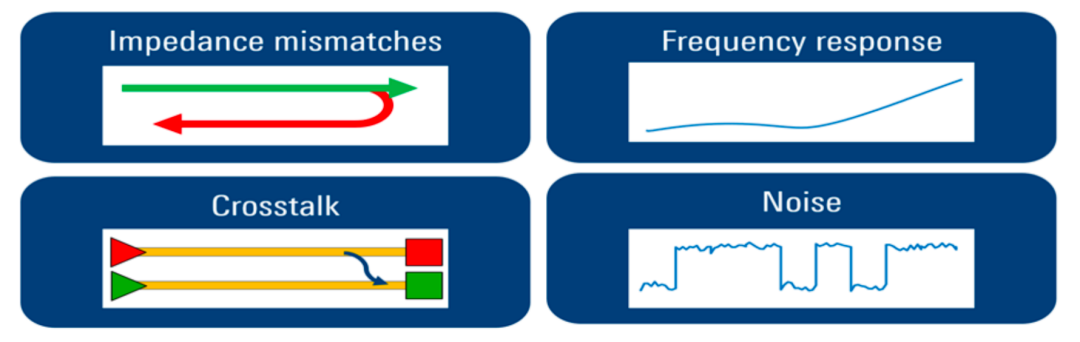

信號在傳輸過程中會受到多種因素的影響,導致信號的失真和降級。這些因素包括阻抗失配、衰減/損耗、串擾和抖動噪聲等。

1、阻抗失配

物理表現:當信號通過傳輸線遇到阻抗突變(如過孔、連接器或線寬變化)時,部分能量會反射回源端,形成振鈴(Ringing)或過沖(Overshoot)。

影響:反射信號與原始信號疊加導致接收誤判邏輯狀態(如將“0”誤判為“1”)。

2、衰減/損耗

插入損耗(Insertion Loss)隨頻率升高快速增長,例如在10 GHz時,FR4板材的損耗可達-2 dB/inch。

物理表現:

趨膚效應(Skin Effect):高頻電流集中在導體表面,增加導體的有效電阻。

介質損耗(Dielectric Loss):高頻電場使PCB基板材料(如FR4)分子極化,產生熱量并削弱信號。

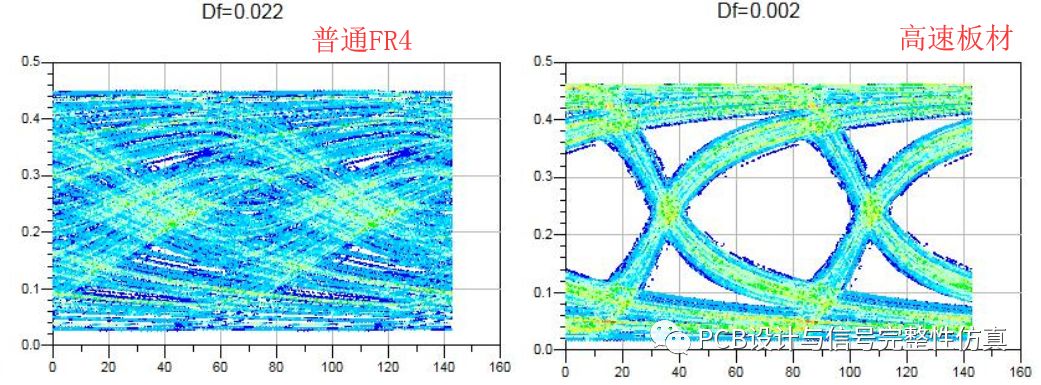

影響:信號高頻分量衰減導致上升時間延長,眼圖閉合。

3、串擾(Crosstalk)

串擾強度與走線間距的平方成反比,例如PCB間距增加1倍,串擾降低約4倍。

影響:

近端串擾(NEXT):干擾信號與主信號在同一端口出現。

遠端串擾(FEXT):干擾信號在傳輸線遠端疊加。

成因:相鄰走線間的互容(Capacitive Coupling)和互感(Inductive Coupling)所導致。

4、抖動噪聲(Jitter)

抖動通常由RJ和DJ組成。由抖動造成的噪聲會干擾信號的傳輸,導致信號質量下降。

分類:

隨機抖動(RJ):由熱噪聲等隨機因素引起,符合高斯分布。

確定性抖動(DJ):由周期性干擾(如電源噪聲、時鐘偏移)引起。

影響:總抖動超過信號單位間隔(UI)的20%時,誤碼率會顯著上升。

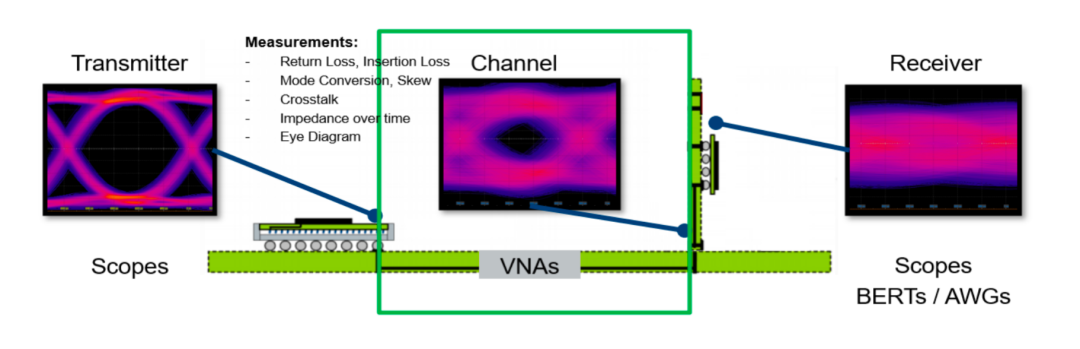

03.高速互連系統的構成

高速互連系統通常由發射機(Tx)、接收機(Rx)和通道(Channel)三個關鍵部分組成。發射機負責將數字信號轉換為適合在通道上傳輸的模擬信號。接收機負責接收通道傳輸的模擬信號,并將其轉換為數字信號。通道是發射機和接收機之間的物理連接,通常由PCB、高速線纜和連接器組成,它主要負責高速信號的傳輸工作。

1發射機

發射機是高速信號傳輸系統的起點,它負責生成并發送信號。在發射機中,信號經過調制、放大等處理后,通過輸出端口發送到通道中。

發射端常用預加重(Pre-emphasis)技術補償高頻損耗。例如PCIe Gen5發射機通過增強第一個比特的幅度來抵消通道衰減。

2通道

通道是信號傳輸的媒介,它可以是PCB上的走線、連接器或電纜等。在通道中,信號會受到衰減、串擾、色散效應和阻抗失配等因素的影響,導致信號失真。

在進行通道設計時,需要充分考慮阻抗匹配、衰減特性以及頻率響應等因素。

3接收機

接收機是高速信號傳輸系統的終點,它負責接收并解碼信號。在接收機中,信號經過放大、濾波等處理后,通過輸入端口送到后續電路中進行處理。

接收端通過集成均衡器(Equalizer)修復信號畸變,如連續時間線性均衡器(CTLE)和決策反饋均衡器(DFE)。

04.信號完整性測量與評估

為了評估高速系統的信號完整性,需要采用一系列測量技術和評估指標。這些技術和指標包括眼圖分析、誤碼率測試(BERT)、頻域S參數以及時域反射特性(TDR)等。

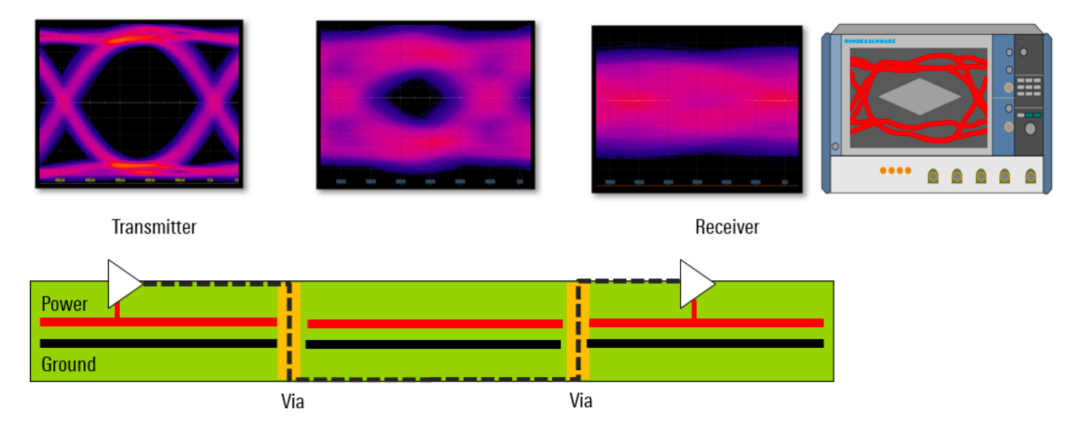

1眼圖分析

眼圖分析是一種常用的信號完整性評估方法。它通過將高速數字信號的1、0和相應轉換疊加在一起,形成類似眼睛的波形,從而評估信號的失真程度。眼圖開口越大,表示信號質量越高;眼圖閉合或模糊則表示信號質量較差。通過眼圖分析,可以直觀地了解信號在整個傳輸鏈路中的失真情況,為優化系統設計提供依據。

2誤碼率測試(BERT)

誤碼率測試是一種通過發送已知模式的信號并檢測接收端錯誤來評估系統性能的方法。在BERT測試中,發射機發送一系列已知模式的信號(如偽隨機二進制序列PRBS),接收機接收并解碼這些信號,然后統計接收到的錯誤碼數。通過計算誤碼率(即錯誤碼數與總碼數之比),可以評估系統的性能穩定性。誤碼率越低,表示系統性能越穩定。

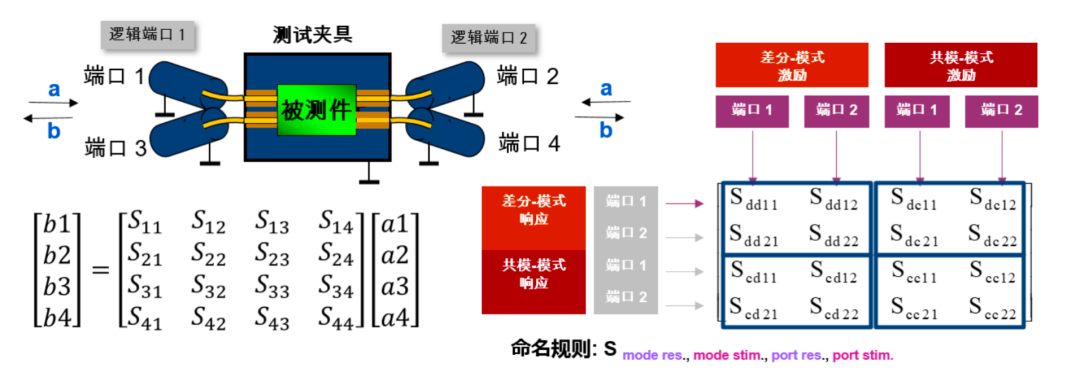

3頻域S參數

散射參數(S參數)是描述網絡端口之間傳輸和反射特性的參數。在高速系統中,S參數可以用于評估通道的性能和阻抗匹配情況。通過測量S參數,可以了解通道的頻率響應、衰減特性以及反射系數等信息。這些信息對于優化通道設計、提高信號完整性具有重要意義。

1Sdd21(差分插入損耗):反映信號從差分端口1到差分端口2的傳輸效率,測量帶寬通常需覆蓋信號基頻(來奎斯特頻率)的1.5-2倍,具體要求視產品標準而定。

2Scd21(共模轉換):衡量差分信號轉換為共模噪聲的能力,這項參數的測量數值通常需要低于-30 dB以抑制EMI影響。

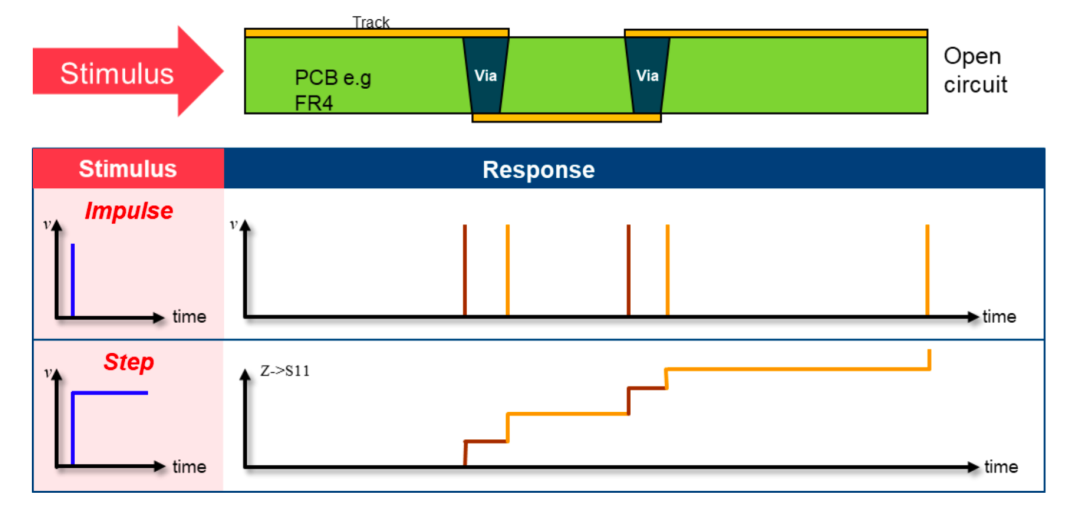

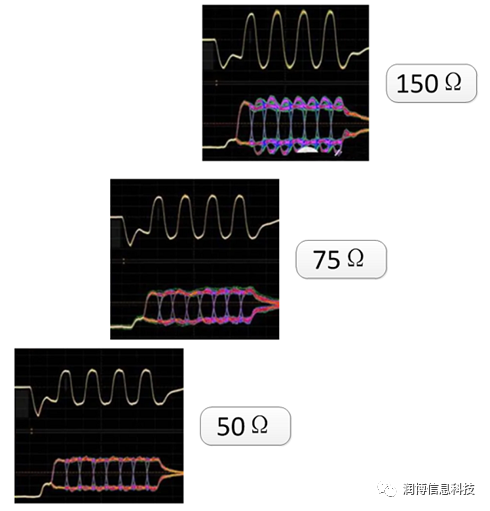

4時域反射特性(TDR)

時域反射是一種用于測量通道阻抗變化和距離信息的方法。在TDR測試中,通過分析反射信號的波形和時間延遲,可以了解通道的阻抗變化和距離信息。TDR測試還可以用于定位通道中的故障點(如開路、短路等),為通道的優化設計提供依據。

05.案例分析與實踐應用

以高速串行通信接口為例,如PCIe5.0/6.0、IEEE 802.3ck/dj等接口對數據傳輸速率有著極高的要求。在設計這些接口時,需要充分考慮信號完整性問題。

具體來說,需要采用阻抗匹配技術來減小反射現象的發生,需要采用預加重/去加重技術來補償高頻成分的衰減。需要采用差分信號傳輸來提高信號的抗干擾能力和信號完整性,同時還需要采用先進的測試技術和評估指標來驗證系統的性能穩定性。

案例一

眼圖閉合

?現象:接收端眼圖水平閉合,誤碼率升高。

?診斷:通道高頻衰減導致上升時間延長。

?解決方法:

發射端啟用預加重(增強前幾個比特的高頻分量)。

接收端配置CTLE均衡器,提升高頻增益。

案例二

PCB近端串擾超標

? 現象:相鄰信號線間串擾達-25 dB,超出設計規格(-30 dB)。

?診斷:走線間距不足(例如僅2倍線寬)。

?解決方法:

重新布線,將間距增至3倍線寬以上。

在走線間插入接地屏蔽線。

案例三

PCB高頻衰減過大

? 現象:趨膚效應和介質損耗導致高頻分量衰減,眼圖閉合。

?診斷:板材選擇不恰當,其在高頻時的損耗太大。

? 解決方法:

使用低損耗PCB板材。

發射端預加重或接收端均衡(如CTLE、DFE)。

總 結

隨著數據傳輸速率的不斷提升和新技術的發展,信號完整性將面臨更多挑戰和機遇。未來,我們需要不斷探索新的測試技術和設計方法,以滿足更高性能的系統需求。以確保高速電子系統的穩定運行和高效傳輸。

工程師通過精確建模(如S參數仿真)、嚴格測試(如眼圖與BER分析、TDR和S參數測試)及針對性優化(如預加重和均衡技術),能夠有效應對高頻衰減、串擾和反射等挑戰。

未來,隨著數據傳輸速率向更高速率演進,信號完整性技術將持續推動通信、計算和消費電子領域的創新。

羅德與施瓦茨業務涵蓋測試測量、技術系統、網絡與網絡安全,致力于打造一個更加安全、互聯的世界。成立90 年來,羅德與施瓦茨作為全球科技集團,通過發展尖端技術,不斷突破技術界限。公司領先的產品和解決方案賦能眾多行業客戶,助其獲得數字技術領導力。羅德與施瓦茨總部位于德國慕尼黑,作為一家私有企業,公司在全球范圍內獨立、長期、可持續地開展業務。

-

接口

+關注

關注

33文章

8968瀏覽量

153361 -

接收機

+關注

關注

8文章

1221瀏覽量

54293 -

發射機

+關注

關注

7文章

513瀏覽量

48488 -

信號完整性

+關注

關注

68文章

1438瀏覽量

96527

原文標題:【一測“高”下】信號完整性測試基礎

文章出處:【微信號:羅德與施瓦茨中國,微信公眾號:羅德與施瓦茨中國】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

信號完整性為什么寫電源完整性?

電源完整性基礎知識

聽懂什么是信號完整性

信號完整性測試基礎知識

信號完整性測試基礎知識

評論