概述

AD6643是一款11位、200 MSPS/250 MSPS、雙通道中頻(IF)接收機,專門針對要求高動態范圍性能、低功耗和小尺寸的電信應用中支持多通道系統而設計。

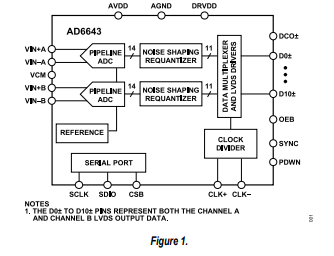

該器件包括兩個高性能模數轉換器(ADC)和噪聲整形再量化器(NSR)數字模塊。每個ADC由多級、差分流水線架構組成,并集成了輸出糾錯邏輯,每個ADC差分流水線的第一級包含一個寬帶寬開關電容采樣網絡。集成基準電壓源可簡化設計考量。占空比穩定器(DCS)補償ADC時鐘占空比的波動,使轉換器保持出色的性能。

數據表:*附件:AD6643雙通道中頻接收機技術手冊.pdf

各ADC的輸出內部連接到NSR模塊。集成NSR電路能夠提高奈奎斯特帶寬內較小頻段的信噪比(SNR)性能。該器件支持兩種不同的輸出模式,通過SPI可以選擇輸出模式。如果使能NSR特性,則在處理ADC的輸出時,AD6643可以在有限的部分奈奎斯特帶寬內實現更高的SNR性能,同時保持11位輸出分辨率。

可以對NSR模塊進行編程,以提供采樣時鐘22%或33%的帶寬。例如,當采樣時鐘速率為185 MSPS時,在22%模式下,AD6643可以在40 MHz帶寬內實現最高75.5 dBFS的SNR;在33%模式下,它可以在60 MHz帶寬內實現最高73.7 dBFS的SNR。

禁用NSR模塊時,ADC數據直接以11位的分辨率提供給輸出端。這種工作模式下,AD6643能夠在整個奈奎斯特帶寬內實現最高66.5 dBFS的SNR。因此,AD6643可以用于電信應用,例如要求更寬帶寬的數字預失真觀測路徑。

經過數字信號處理后,多路復用輸出數據路由至一個11位輸出端口,最大數據速率為400 Mbps (DDR)。這些輸出設置為LVDS,支持ANSI-644電平。

AD6643接收器能夠對很寬的中頻頻譜進行數字化處理。各接收機設計用于同步接收不同的天線。該IF采樣架構與傳統的模擬技術或較低集成度的數字方法相比,能大幅度降低元件的成本和復雜度。

靈活的掉電選項可以明顯降低功耗。器件設置與控制的編程利用三線式SPI兼容型串行接口來完成;該接口提供多種工作模式,支持電路板級系統測試。

AD6643采用64引腳無鉛9 mm × 9 mm引腳架構芯片級封裝(LFCSP_VQ),符合RoHS標準,額定溫度范圍為?40°C至+85°C工業溫度范圍。該產品受美國專利保護。

產品聚焦

- 兩款ADC均采用節省空間的9 mm × 9 mm × 0.85 mm、64引腳LFCSP小型封裝。

- 引腳可選的噪聲整形再量化器(NSR)功能,能夠在185 MSPS下帶寬降低至最大60 MHz時提高信噪比。

- LVDS數字輸出接口針對低成本FPGA系列而配置。

- 采用1.8 V單電源供電。

- 標準串行端口接口(SPI)支持各種產品特性和功能,例如:數據格式化(偏移二進制或二進制補碼)、NSR、掉電、測試模式以及基準電壓模式。

- 片內1到8整數輸入時鐘分頻器和多芯片同步功能支持廣泛的時鐘方案和多通道子系統。

應用

特性

- 每個通道11位、250 MSPS輸出數據速率

- NSR使能時的性能

- NR:74.5 dBFS(55 MHz頻段、最高90 MHz、250 MSPS)

- SNR:72.0 dBFS(82 MHz頻段、最高90 MHz、250 MSPS)

- NSR禁用時的性能

- SNR:66.2 dBFS(最高90 MHz、250 MSPS)

- SFDR:85 dBc(最高185 MHz、250 MSPS)

- 總功耗:706 mW (200 MSPS)

- 1.8 V電源電壓

- LVDS(ANSI-644電平)輸出

- 1至8整數輸入時鐘分頻器(最大輸入頻率625 MHz)

- ADC內部基準電壓源

- 靈活的模擬輸入范圍

- 1.4 V p-p至2.0 V p-p(標稱值1.75 V p-p)

- 差分模擬輸入、400 MHz帶寬

- 95 dB通道隔離/串擾

- 串行端口控制

- 節能的關斷模式

框圖

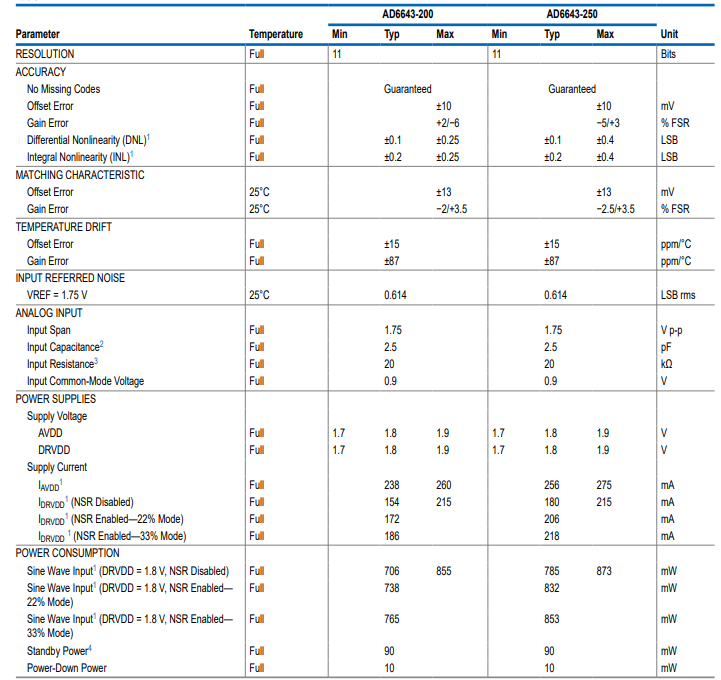

ADC DC規格

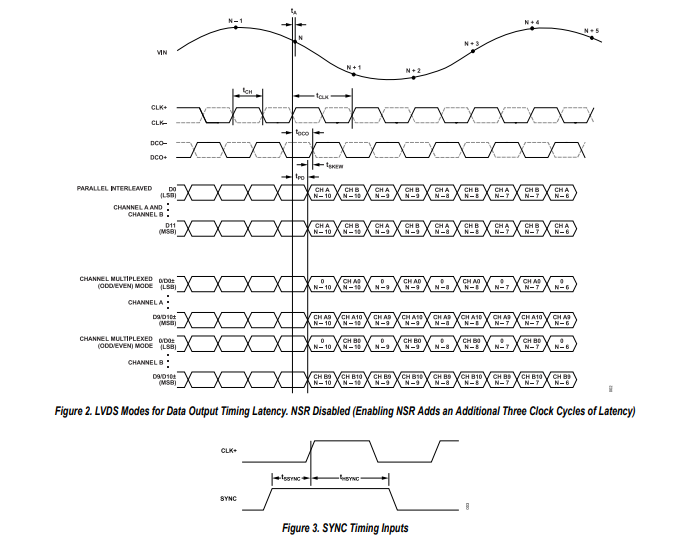

時序圖

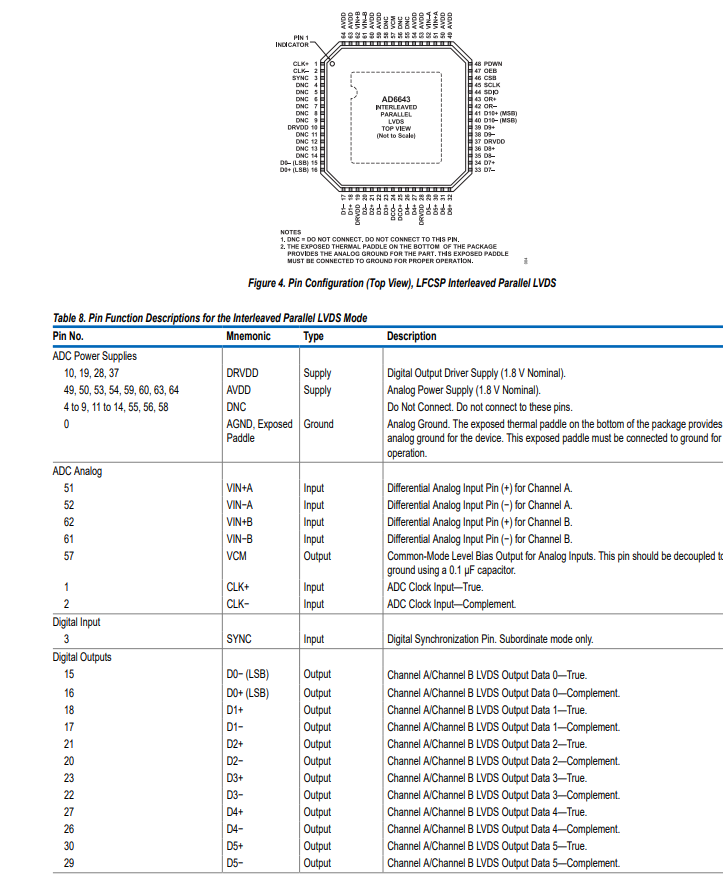

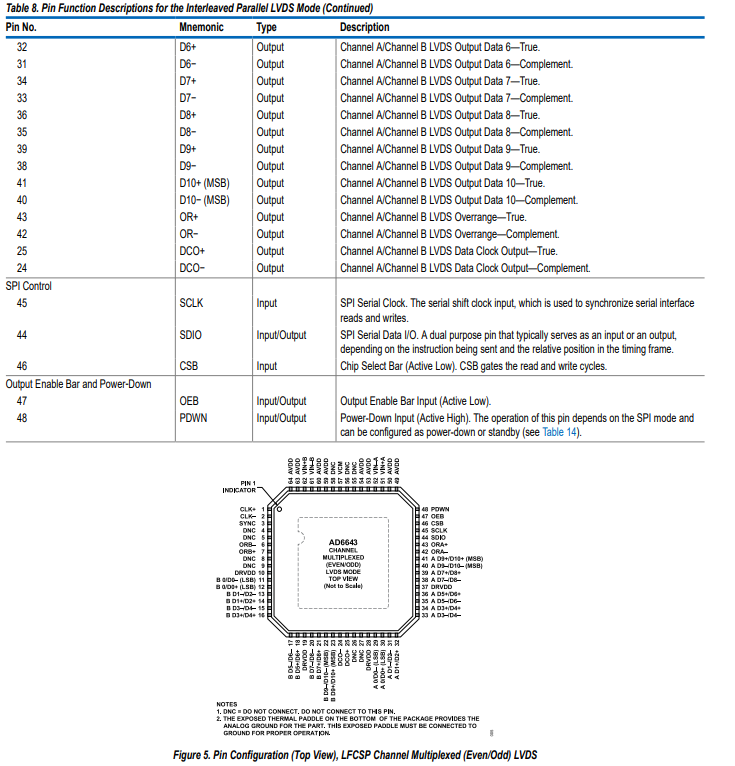

引腳配置描述

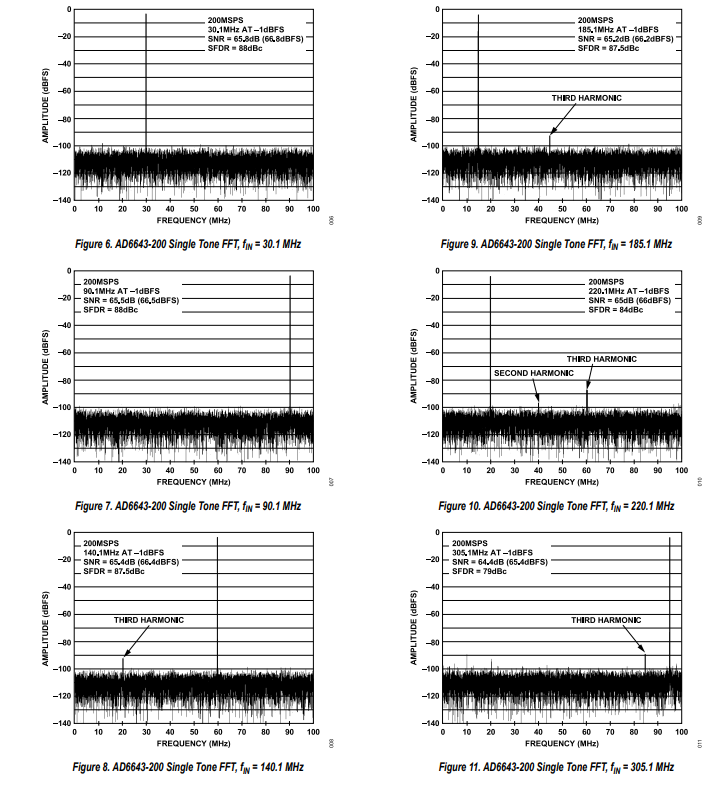

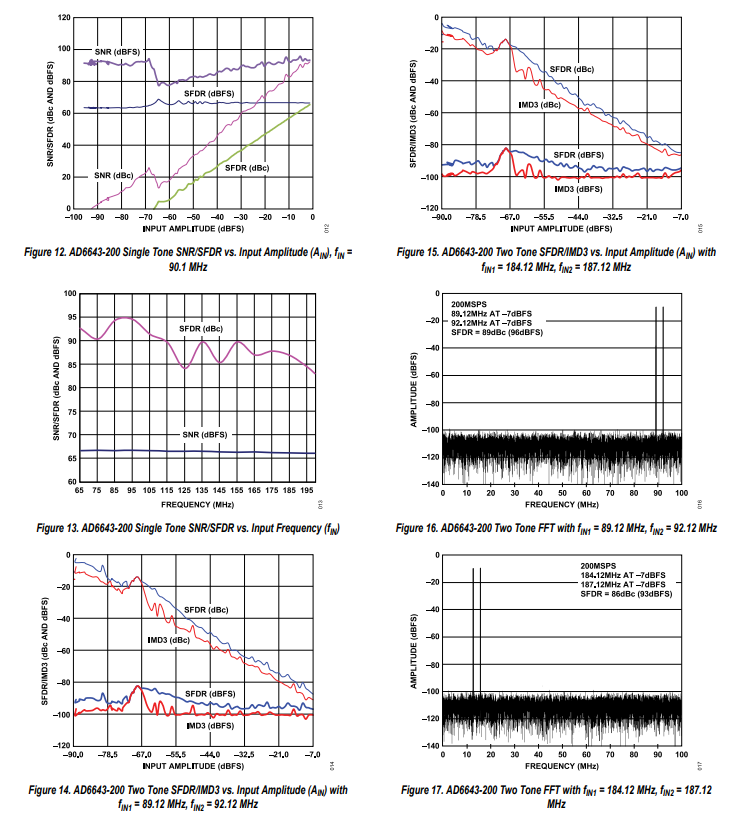

典型性能特征

典型性能特征

AD6643有兩個模擬輸入通道和兩個數字輸出通道。中間頻率(IF)信號在呈現于輸出端口之前,會經過多個處理階段。

ADC架構

AD6643架構由雙前端采樣保持電路組成,其后連接流水線開關電容ADC。每個階段的量化輸出先進行合并,再得到最終的11位數字校正邏輯結果。或者,這11位結果在送入數字校正邏輯之前,可先通過NSR模塊進行處理。

流水線架構使第一級能夠基于新的輸入樣本運行,并讓其余各級對前一個樣本進行處理,在時鐘上升沿進行采樣。

流水線的每一級(最后一級除外)均由一個低分辨率閃存ADC、一個數模轉換器(DAC)以及一個積分誤差放大器(MDAC)組成。MDAC對DAC輸出與下一級流水線中閃存輸入的差值進行放大。每一級中都有一位冗余,用于校正閃存誤差。最后一級僅由一個閃存ADC組成。

每個通道的輸入級包含一個差分采樣電路,可實現交流耦合或單端模式。輸出數據鎖存模塊會阻塞數據、校正誤差,并將數據輸出到外部緩沖器。輸出緩沖器由獨立電源供電,在掉電期間,輸出緩沖器進入高阻態。

AD6643雙接收器可同時對兩個通道進行數字化處理,用于支持通信系統中多樣性接收和數字預失真(DPD)觀測路徑。

雙中頻接收器設計可用于處理同一載波上的不同接收信號,也可使用不同的天線處理不同的載波信號。ADC也可使用不同的天線,在直流至300 MHz的頻率范圍內對輸入進行帶通濾波,以最小的性能損失對400 MHz的模擬輸入進行濾波。不過,這樣做會增加ADC的噪聲和失真。

它具備同步功能,可實現多個通道或多個器件之間的定時同步。通過一個三線制、SPI兼容的串行接口對AD6643進行編程和控制。

模擬輸入注意事項

AD6643的模擬輸入采用差分開關電容電路,針對差分輸入信號處理進行了優化。

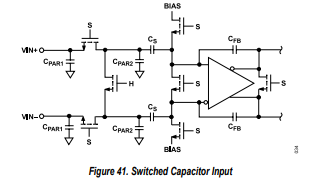

時鐘信號交替切換輸入電路,使其在采樣模式和保持模式間轉換(見圖41)。處于采樣模式時,信號源必須能夠在半個時鐘周期內完成對采樣電容的充電以及設置。

每個輸入端串聯一個小電阻,有助于降低驅動源輸出級所需的峰值瞬態電流。可在輸入端之間并聯一個旁路電容,為動態充電電流提供通路。這種無源網絡會在ADC輸入端形成一個低通濾波器,因此,具體數值取決于應用場景。

為實現最佳動態性能,需匹配驅動VIN+和VIN - 引腳的源阻抗,并使輸入差分平衡。

輸入共模

AD6643的模擬輸入內部無直流偏置。在交流耦合應用中,用戶必須從外部提供此偏置。將器件設置為VCM = 0.5 × AVDD(或0.9 V)可實現最佳性能。

芯片設計中集成了片上共模電壓基準,可通過VCM引腳獲取。建議使用VCM輸出來設置輸入共模。

模擬輸入的最佳共模電壓由VCM引腳電壓(通常為0.5 × AVDD)設定。VCM引腳必須通過0.1 μF電容接地,具體內容見應用信息部分。將此去耦電容放置在靠近引腳處,可縮短電阻和電感回路,從而改善性能。

-

接收機

+關注

關注

8文章

1220瀏覽量

54267 -

IF

+關注

關注

1文章

64瀏覽量

27133 -

ADC

+關注

關注

0文章

207瀏覽量

16845 -

NSR

+關注

關注

0文章

5瀏覽量

1507

發布評論請先 登錄

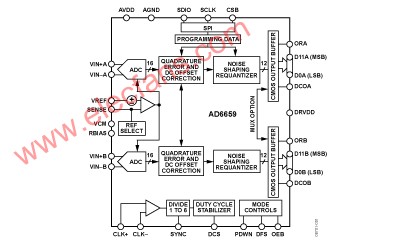

AD6659混合信號雙通道中頻接收機

高性能、雙通道IF采樣接收機

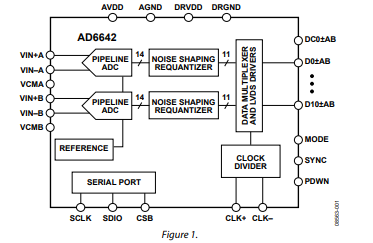

80MHz帶寬雙通道中頻接收機

AD6643 雙通道中頻接收機

CN0140 高性能、雙通道IF采樣接收機

AD6642雙通道中頻接收機技術手冊

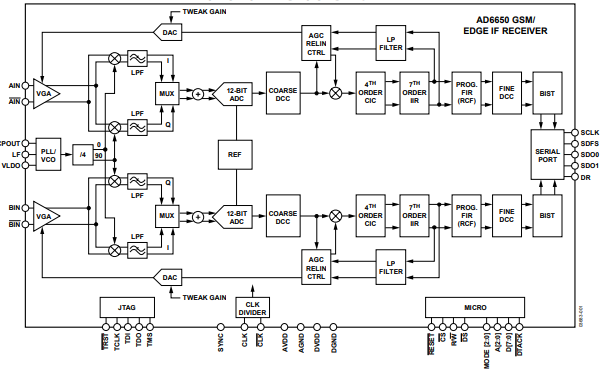

AD6650分集中頻至基帶GSM/EDGE窄帶接收機技術手冊

AD6643雙通道中頻接收機技術手冊

AD6643雙通道中頻接收機技術手冊

評論