概述

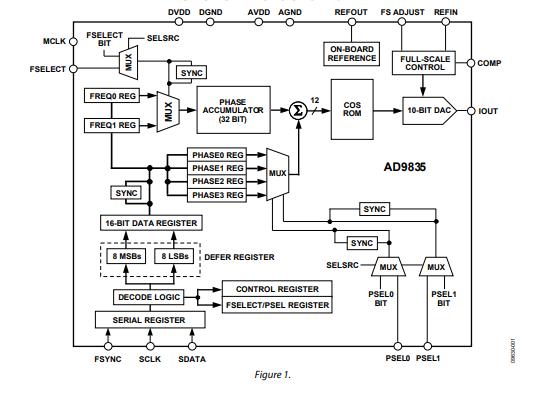

AD9835是一款數(shù)控振蕩器,在單個(gè)CMOS芯片內(nèi)集成了一個(gè)相位累加器、一個(gè)COS查找表以及一個(gè)10位數(shù)模轉(zhuǎn)換器,提供相位調(diào)制和頻率調(diào)制兩種調(diào)制能力。

最高支持50 MHz時(shí)鐘速率。頻率控制精度可達(dá)40億分之一。調(diào)制通過串行接口載入寄存器來實(shí)現(xiàn)。用戶可使用一個(gè)關(guān)斷位在不用時(shí)關(guān)斷AD9835,將功耗降低至1.75 mW。

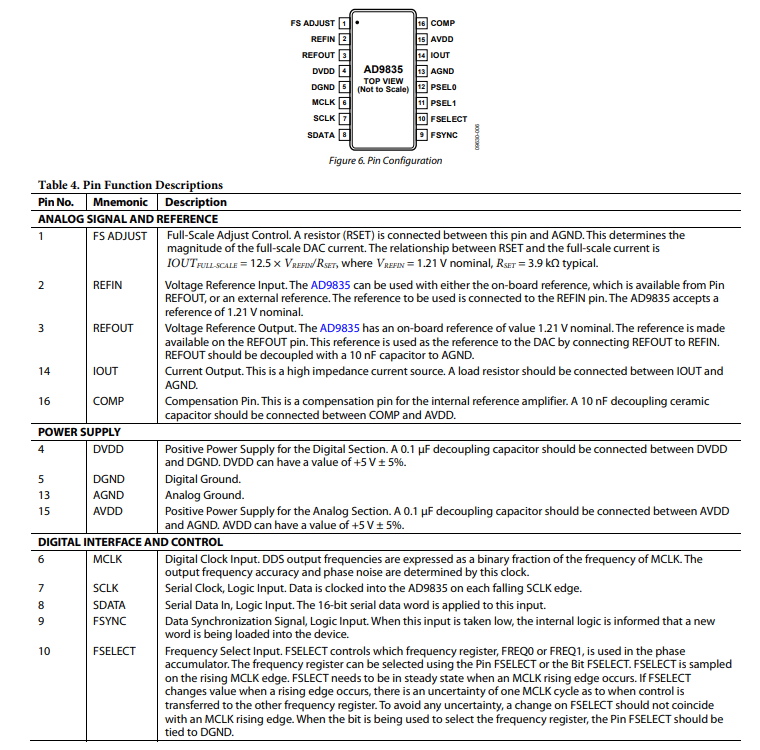

該器件采用16引腳TSSOP封裝。

數(shù)據(jù)表:*附件:AD9835 50MHz直接數(shù)字頻率合成器、波形發(fā)生器技術(shù)手冊(cè).pdf

應(yīng)用

- 頻率激勵(lì)/波形發(fā)生

- 頻率相位調(diào)諧和調(diào)制

- 低功耗RF/通信系統(tǒng)

- 液體和氣流測(cè)量

- 傳感器應(yīng)用:接近度、運(yùn)動(dòng)和缺陷檢測(cè)

- 測(cè)試與醫(yī)療設(shè)備

特性

框圖

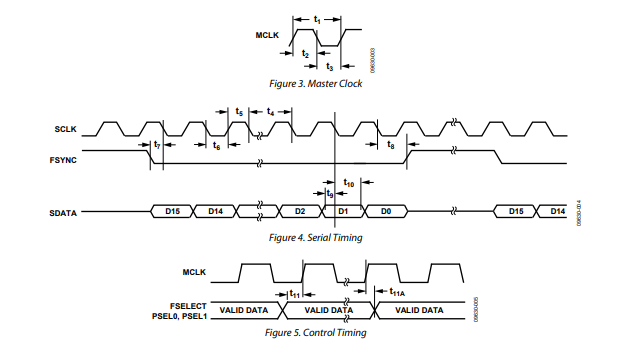

時(shí)序圖

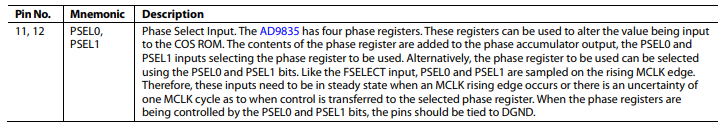

引腳配置描述

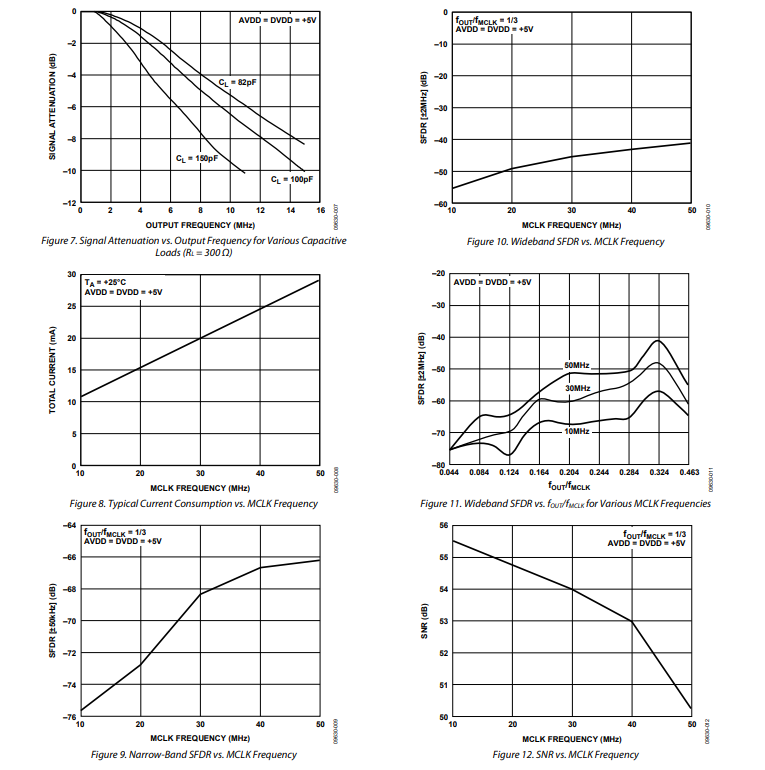

典型性能特征

應(yīng)用信息

AD9835具備的功能使其適用于調(diào)制應(yīng)用。該器件可用于執(zhí)行簡單的調(diào)制,如頻移鍵控(FSK)。更為復(fù)雜的調(diào)制方案,如高斯最小移頻鍵控(GMSK)和正交相移鍵控(QPSK),也可通過AD9835來實(shí)現(xiàn)。

在FSK應(yīng)用中,AD9835的兩個(gè)頻率寄存器會(huì)被加載不同的值,其中一個(gè)頻率代表頻移空間頻率,另一個(gè)則代表標(biāo)記頻率。數(shù)字?jǐn)?shù)據(jù)流中的FSELECT引腳會(huì)使AD9835在這兩個(gè)值之間對(duì)載波頻率進(jìn)行調(diào)制。

AD9835有四個(gè)相位寄存器,這使該器件能夠?qū)崿F(xiàn)相移鍵控(PSK)。在PSK調(diào)制中,載波頻率的相位會(huì)發(fā)生偏移,偏移量與輸入到調(diào)制器的比特流相關(guān)。四個(gè)移位寄存器的存在,簡化了數(shù)字信號(hào)處理器(DSP)與AD9835之間所需的交互。

AD9835也適用于信號(hào)發(fā)生器應(yīng)用。鑒于其低電流消耗特性,該器件適用于可用作本地振蕩器的應(yīng)用。

接地與布局

承載AD9835的印刷電路板在設(shè)計(jì)時(shí),應(yīng)確保模擬部分和數(shù)字部分相互分離并限定在特定區(qū)域內(nèi)。這有助于實(shí)現(xiàn)接地層的分離,而這是一種普遍認(rèn)為能為接地平面提供最佳屏蔽效果的技術(shù)。數(shù)字接地平面和模擬接地平面應(yīng)僅在一處連接。對(duì)于AD9835而言,是唯一需要進(jìn)行AGND(模擬地)到DGND(數(shù)字地)連接的器件,其AGND引腳和DGND引腳應(yīng)進(jìn)行連接。如果在一個(gè)系統(tǒng)中,多個(gè)器件都需要AGND到DGND的連接,那么連接點(diǎn)應(yīng)僅設(shè)置一個(gè),并且應(yīng)盡可能在靠近AD9835的位置建立穩(wěn)定的接地路徑。

應(yīng)避免在器件下方布設(shè)數(shù)字線路,因?yàn)檫@些線路會(huì)引入噪聲。模擬接地平面應(yīng)在AD9835下方鋪設(shè),以防止噪聲耦合。為AD9835供電的電源線應(yīng)盡可能寬,以便降低阻抗,并減少電源線上的尖峰噪聲。像時(shí)鐘信號(hào)這類快速開關(guān)信號(hào),應(yīng)使用數(shù)字接地進(jìn)行屏蔽,以避免其向電路板的其他部分輻射噪聲。

要防止數(shù)字信號(hào)與模擬信號(hào)交叉。電路板兩側(cè)的走線應(yīng)相互垂直,以減少饋通效應(yīng)。在雙層板中,微帶線技術(shù)通常是最佳選擇,但并非總是可行,因?yàn)殡娐钒宓牧硪粋?cè)往往要專門用于接地平面,而信號(hào)則布置在另一側(cè)。

良好的去耦至關(guān)重要。AD9835的模擬電源和數(shù)字電源相互獨(dú)立,分別引出,以盡量減少模擬部分與數(shù)字部分之間的耦合。所有模擬電源和數(shù)字電源都應(yīng)進(jìn)行去耦處理,將AGND和DGND分別與0.1 μF陶瓷電容并聯(lián)10 μF鉭電容 。為實(shí)現(xiàn)最佳的去耦性能,這些電容應(yīng)盡可能靠近器件放置,理想情況是緊貼器件。在使用同一電源為AD9835的AVDD(模擬電源)引腳和DVDD(數(shù)字電源)引腳供電的系統(tǒng)中,建議采用系統(tǒng)電源旁路。推薦在AVDD引腳處采用模擬電源去耦,在DGND引腳與DVDD引腳之間采用數(shù)字電源去耦。

將AD9835與微處理器連接

AD9835具有標(biāo)準(zhǔn)串行接口,可使其直接與多個(gè)微處理器連接。該器件使用外部串行時(shí)鐘將數(shù)據(jù)或控制信息寫入內(nèi)部。串行時(shí)鐘的頻率最高可達(dá)20 MHz。串行時(shí)鐘可以是連續(xù)的,也可根據(jù)需要空閑或保持低電平。每次向AD9835寫入數(shù)據(jù)時(shí),F(xiàn)SYNC(幀同步)信號(hào)都會(huì)被拉低,并保持低電平狀態(tài),直至16位數(shù)據(jù)寫入完成。FSYNC信號(hào)用于將加載到AD9835中的16位信息成幀。

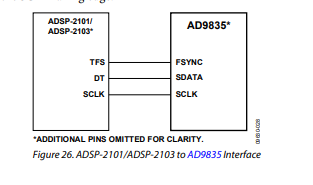

AD9835與ADSP - 21XX接口

圖26展示了AD9835與ADSP - 21xx之間的串行接口。ADSP - 21xx應(yīng)設(shè)置為在SPORT傳輸交替成幀模式(FSTW = 1)下運(yùn)行。ADSP - 21xx應(yīng)按如下方式配置:內(nèi)部時(shí)鐘操作(ISCLK = 1),16位字長(SLEN = 15),內(nèi)部幀同步信號(hào)(ITFS = 1),并生成幀同步信號(hào)(TFSR = 1)。

通過將字寫入Tx寄存器來啟動(dòng)傳輸。數(shù)據(jù)在串行時(shí)鐘的上升沿輸出,并在AD9835中通過SCLK的下降沿進(jìn)行時(shí)鐘控制。

-

波形發(fā)生器

+關(guān)注

關(guān)注

3文章

307瀏覽量

31977 -

AD9835

+關(guān)注

關(guān)注

0文章

8瀏覽量

10097 -

數(shù)控振蕩器

+關(guān)注

關(guān)注

0文章

17瀏覽量

10283 -

數(shù)字頻率合成器

+關(guān)注

關(guān)注

0文章

31瀏覽量

6552

發(fā)布評(píng)論請(qǐng)先 登錄

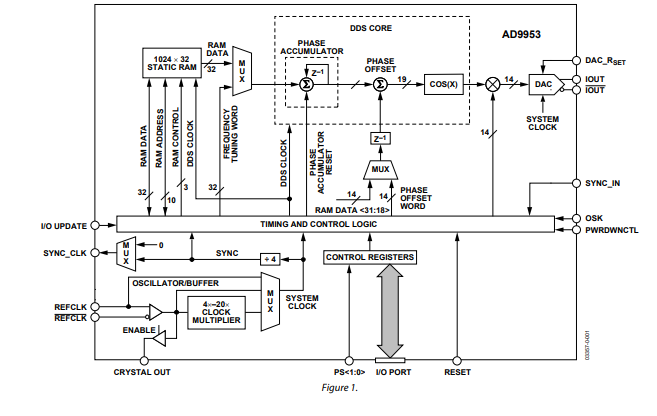

AD9953 400 MSPS、14位DAC、1.8 V CMOS直接數(shù)字頻率合成器技術(shù)手冊(cè)

AD9951 400 MSPS、14位DAC、1.8 V CMOS直接數(shù)字頻率合成器技術(shù)手冊(cè)

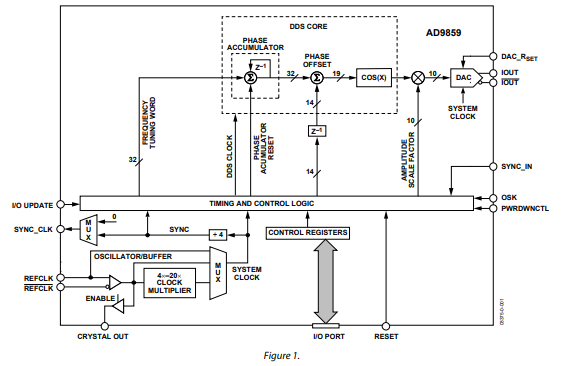

AD9859 400 MSPS、10位DAC、1.8 V CMOS直接數(shù)字頻率合成器技術(shù)手冊(cè)

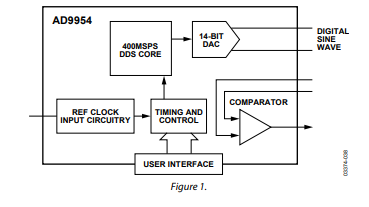

AD9954 400MSPS、14位、1.8V CMOS、直接數(shù)字頻率合成器技術(shù)手冊(cè)

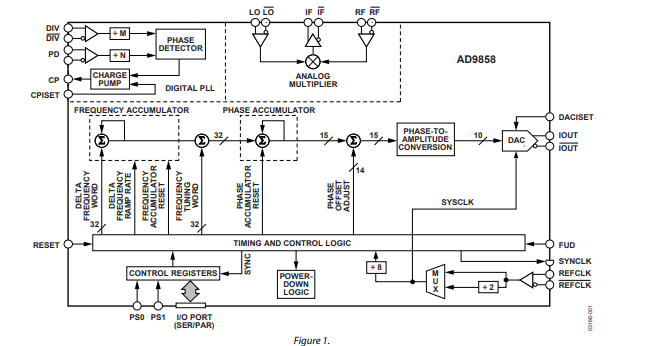

AD9858 1 GSPS直接數(shù)字頻率合成器技術(shù)手冊(cè)

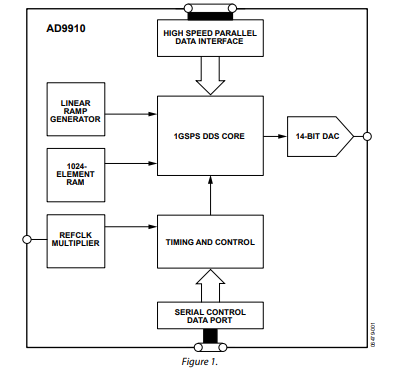

AD9910 1GSPS,14bit,3.3V CMOS直接數(shù)字頻率合成器技術(shù)手冊(cè)

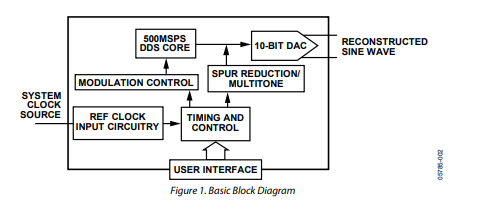

AD9911 500 MSPS直接數(shù)字頻率合成器,內(nèi)置10位DAC技術(shù)手冊(cè)

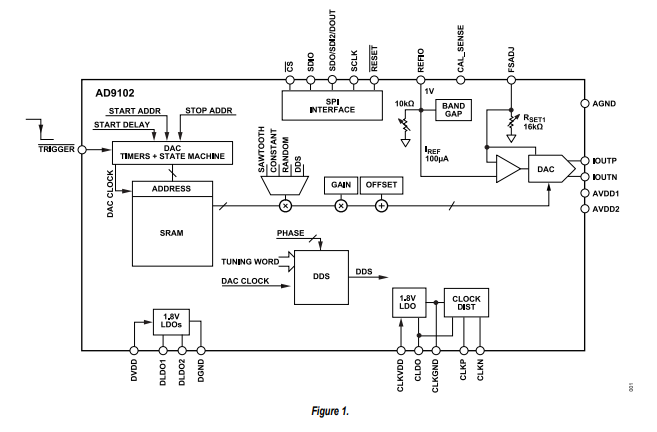

AD9102低功耗、14位、180MSPS、數(shù)模轉(zhuǎn)換器和波形發(fā)生器技術(shù)手冊(cè)

敏捷合成器的技術(shù)原理和應(yīng)用場(chǎng)景

DS878?數(shù)字合成器適合哪些應(yīng)用場(chǎng)景?

AN-423: 直接數(shù)字頻率合成器AD9850的幅度調(diào)制

AN-953: 具可編程模數(shù)的直接數(shù)字頻率合成器(DDS)

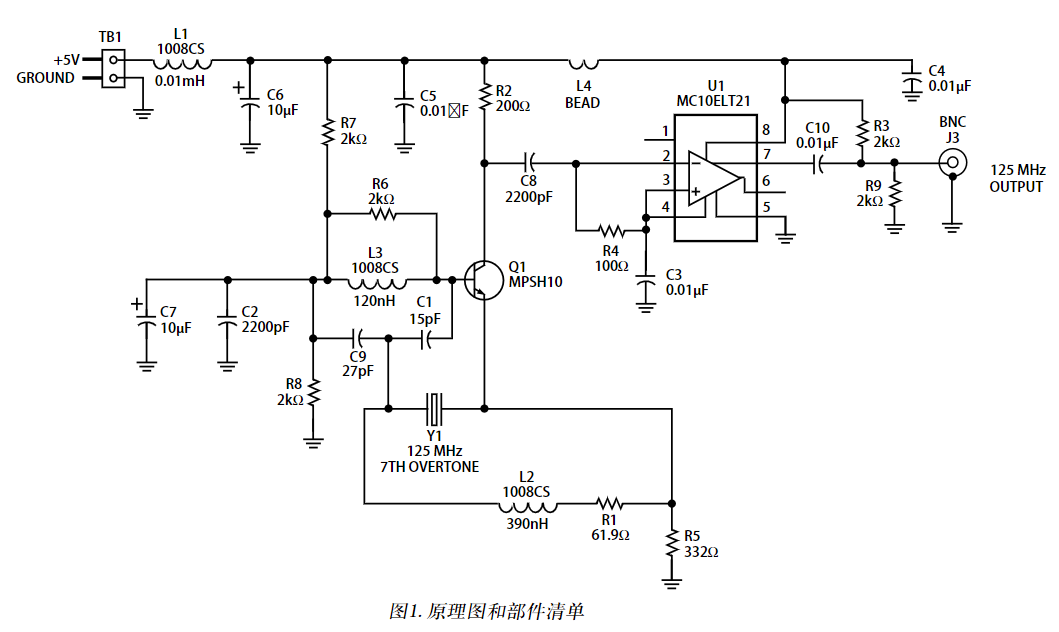

完整的直接數(shù)字頻率合成器 AD9850 的分立、低相位噪聲、125MHz 晶振解決方案

AD9835 50MHz直接數(shù)字頻率合成器、波形發(fā)生器技術(shù)手冊(cè)

AD9835 50MHz直接數(shù)字頻率合成器、波形發(fā)生器技術(shù)手冊(cè)

評(píng)論