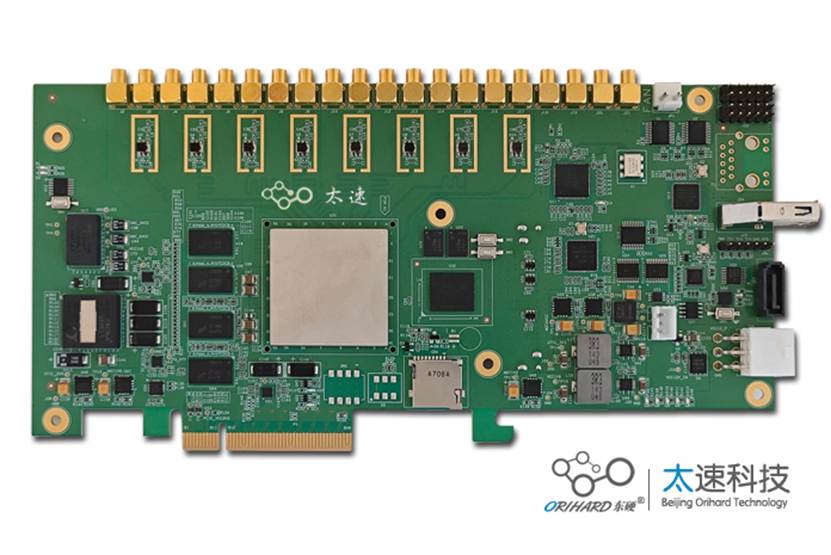

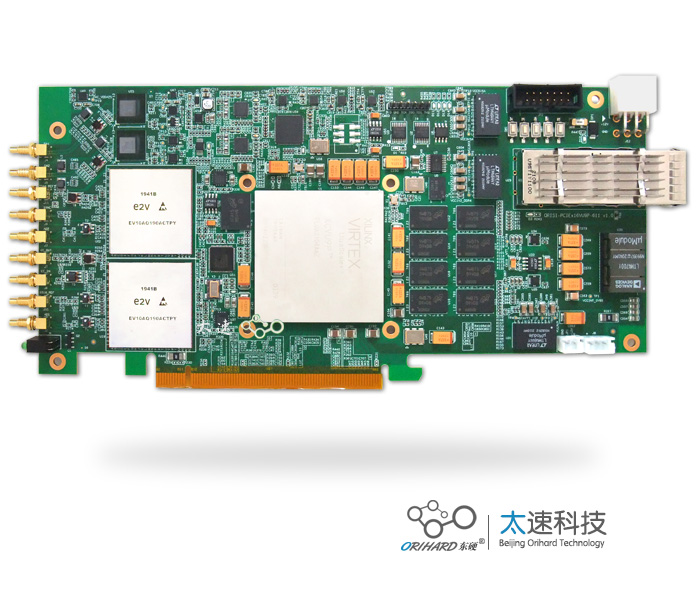

一、板卡概述

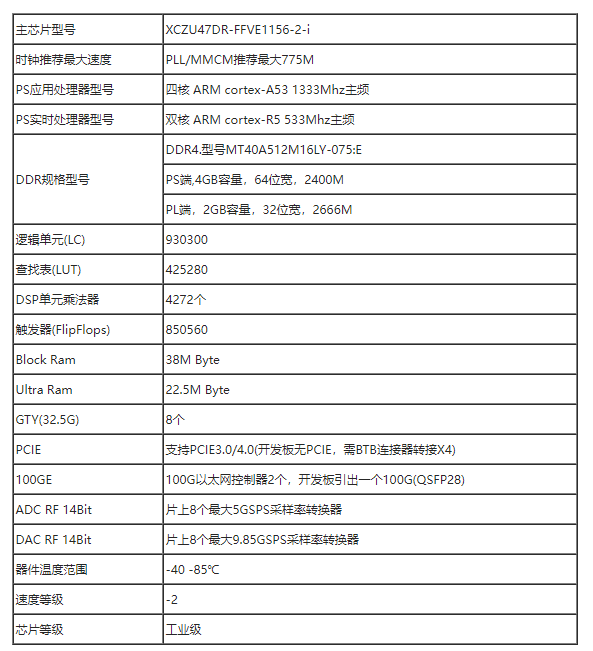

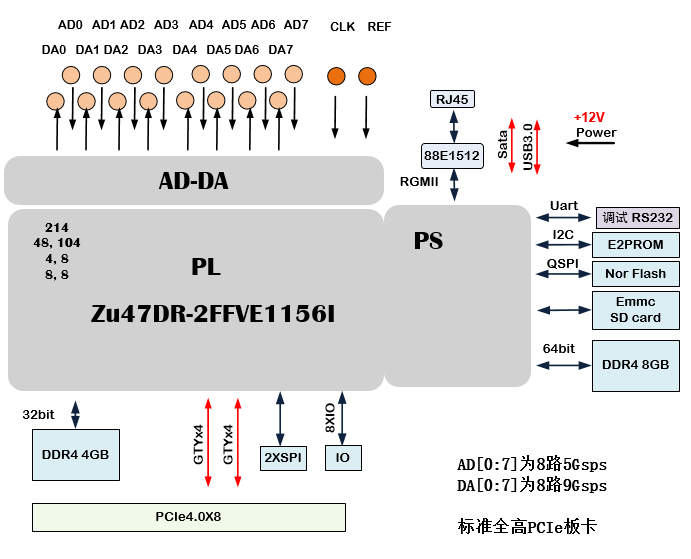

板卡使用Xilinx最新的第三代RFSOC系列,單顆芯片包含8路ADC和DAC,64-bit Cortex A53系列4核CPU,Cortex-R5F實時處理核,以及大容量FPGA。

對主機接口采用PCIe Gen4x8,配合PCIe DMA傳輸,支持高速數據采集和傳輸。

二、產品特性:

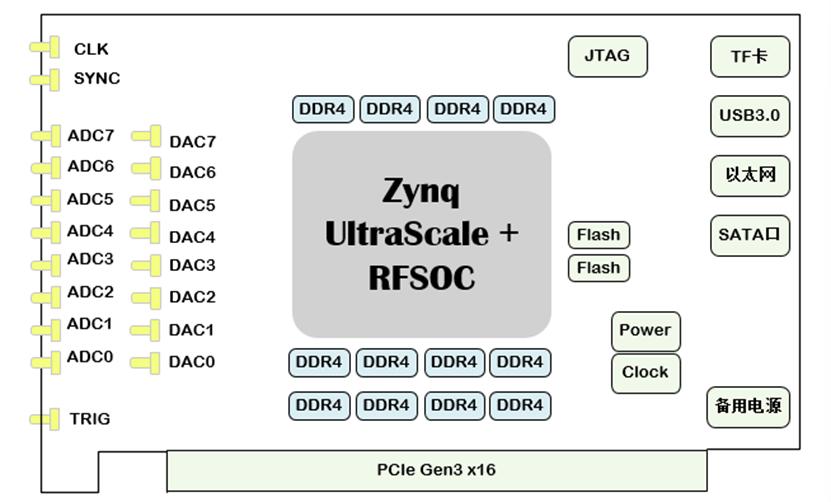

● 基于Zynq RFSoC系列FPGA,支持8路最高5G ADC和8路最高9G的DAC;

● 支持外部時鐘輸入1路, 外觸發,外同步各1路;

● PL 1組64 bit 2400M DDR4,支持PL部分高速存儲和處理。 單組4GB字節容量,PL部分8GB字節容量。

● 支持16個GPIO

PS部分內容:

● PS部分1組64bit位寬DDR4,單組4GB字節

● 可配置的Dual QSPI 加載

● 支持MicroSD卡加載

● 標準PCIe全高半長板型(167 x 111 mm ),適配常見主機、服務器

● PCIe Gen4 x8,高速數據通訊,附帶DMA傳輸例程

軟件開發內容:

接口

AD

DA

ARM AXI

DDR

PCIe

指標

8路

5Gbps

14bit

8路

9.85Gbps 14bit

DMA 傳輸

400MB/s

一組10GB/s,

共2組

PCIeX8 V4.0,8GB/s

PL部分,主要分為:

1,PCIe XDMA部分,PCIe分為寄存器通道和數據DMA通道,寄存器用于板卡控制和狀態監控,。實現參考累加數的PCIe上傳,實現8GB/秒傳輸。

2,DDR4讀寫參考程序。

3,RF硬件控制,用于控制板卡上PLL,ADC和DAC控制。

4,AD數據接口模塊,實現AD數據采集入PL;

5,DA數據接口模塊,實現DDS數據或者AD采集數據環回DA播出。

6,PL端 40路 IO的輸入輸出測試。

PS部分軟件

ARM的DDR讀寫, SD卡,EMMC讀寫,Flash讀寫,網絡和RS232讀寫。

Linux移植,甲方來完成。

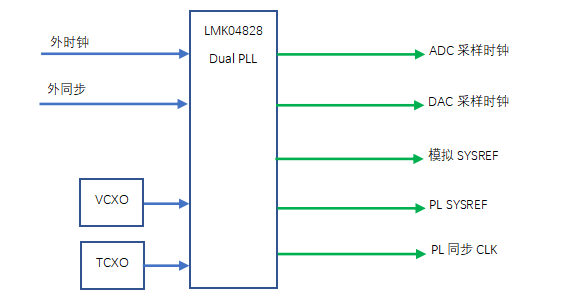

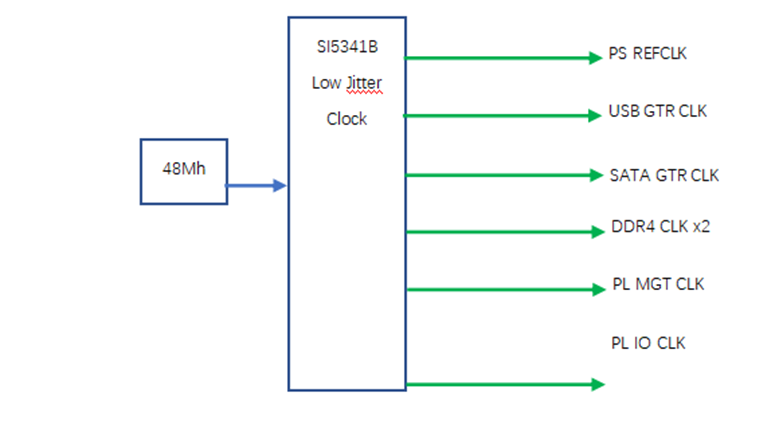

時鐘設計:

板卡時鐘靈活,支持多種應用配置,模擬部分的時鐘,采用LMK04828,雙PLL鎖相環。

如果采用板內時鐘,用TCXO和VCXO雙鎖相環,提供穩定可靠的模擬時鐘。同時也輸出一路給FPGA進行數字處理。

該方案也支持使用外部獨立輸入時鐘,通過LMK04828扇出后輸出給ADC和DAC。

數字部分,使用高集成度的SI5341B,單路芯片輸出PS和PL所需的各路時鐘。

-

接口

+關注

關注

33文章

8990瀏覽量

153639 -

adc

+關注

關注

99文章

6686瀏覽量

549018 -

PCIe

+關注

關注

16文章

1339瀏覽量

85041 -

RFSoC

+關注

關注

0文章

39瀏覽量

2910

發布評論請先 登錄

熱門5G路由器參數對比,華為智選Brovi 5G CPE 5 VS SUNCOMM SDX75

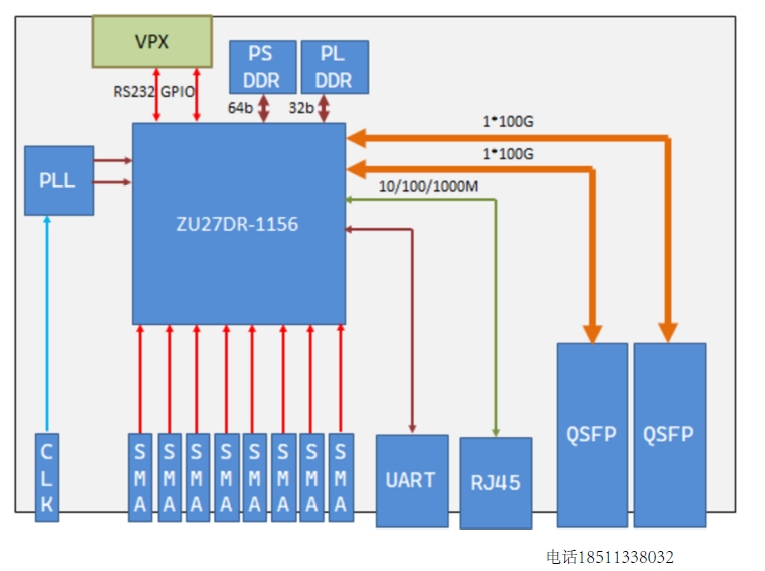

高速數據采集卡設計:887-基于 RFSoC 47DR的8T8R 100Gbps 軟件無線電光纖前端卡

Banana Pi BPI-R4 Pro Wifi7 路由器開發板采用聯發科MT7988A芯片設計,支持4個2.5G網口,支持2個10G光電口,支持4G/5G擴展

高速數據采集卡設計方案:886-基于RFSOC的8路5G ADC和8路9G的DAC PCIe卡

愛立信攜手Telstra、高通刷新5G上行鏈路速度紀錄

ADS8528的8路都能同時達到650KSPS采樣率,還是單路使用時才能達到?

需要將一路RGB信號(R:0~8,G:0~8,B:0~8)轉換成LVDS信號,請問這個LVDS信號有沒有單路和雙路的可以選擇?

CDCDB800/803超低附加抖動、8路輸出PCIe Gen1至Gen5時鐘緩沖器

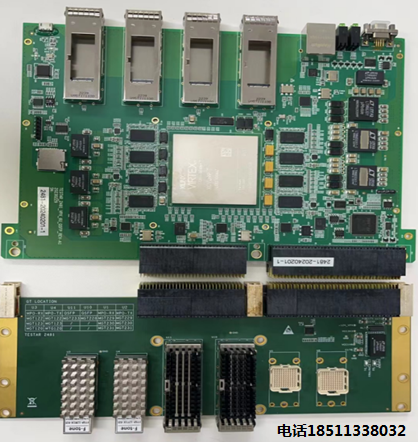

基于ZU19EG的4路100G光纖的PCIe 加速計算卡

基于RFSOC的8路5G ADC和8路9G的DAC PCIe卡

基于RFSOC的8路5G ADC和8路9G的DAC PCIe卡

評論