文章來源:半導體與物理

原文作者:jjfly686

本文介紹了CMOS工藝中第一層互聯(lián)的作用、材料及工藝步驟。

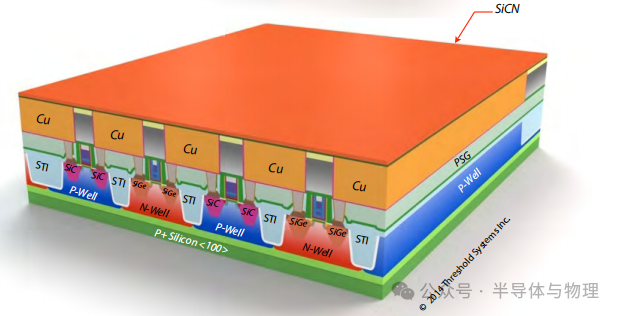

芯片中的晶體管(如NMOS和PMOS)需要通過金屬線連接才能形成完整電路。第一層互聯(lián)(通常稱為M0或Local Interconnect)是直接連接晶體管源極、漏極和柵極的金屬層,位于晶體管上方,距離硅襯底僅幾十納米。它的核心任務是在器件層建立最短、最密集的連接通道,避免信號繞行到高層金屬,從而提升芯片性能和集成密度。

第一層互聯(lián)的結(jié)構(gòu)與作用

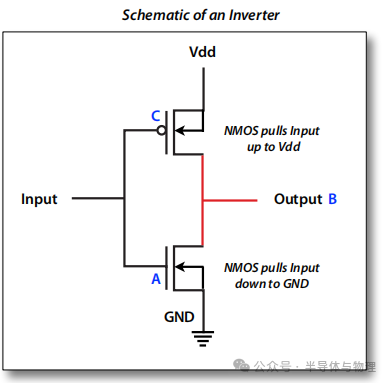

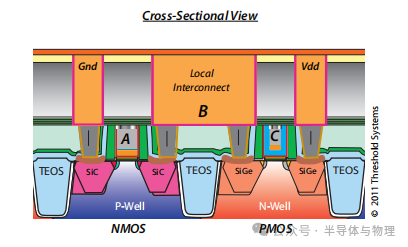

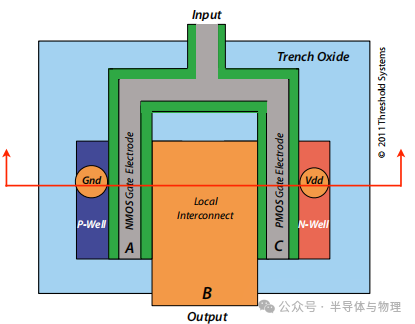

以最簡單的CMOS反相器為例(如下圖),NMOS和PMOS的漏極與源極需要通過金屬線直接相連:

物理結(jié)構(gòu):

NMOS漏極(A)與PMOS源極(C)通過第一層銅線(B)直接連接,形成輸出端;

柵極(Input)通過多晶硅或金屬線接收輸入信號;

電源(Vdd)和地線(GND)通過局部互連分別連接到PMOS和NMOS。

縮短路徑:信號直接在晶體管間傳輸,無需繞行至更高層金屬(如M1-M10),延遲降低15%-20%;節(jié)省面積:在7 nm芯片中,第一層互聯(lián)使邏輯單元面積縮小30%以上;簡化設計:減少布線交叉點,降低電路復雜度。

材料與工藝

第一層互聯(lián)的金屬線寬度通常在10-30 nm(約為頭發(fā)絲的萬分之一),需采用特殊材料和工藝:銅(Cu):電阻率低(1.68 μΩ·cm),但需搭配氮化鉭(TaN)阻擋層防止銅擴散;鈷(Co):在5 nm以下節(jié)點逐步替代銅,填充深寬比>5:1的納米溝槽時無空隙缺陷;阻擋層:2 nm厚的鉭(Ta)或鈦(Ti),增強金屬與介質(zhì)層的結(jié)合力。

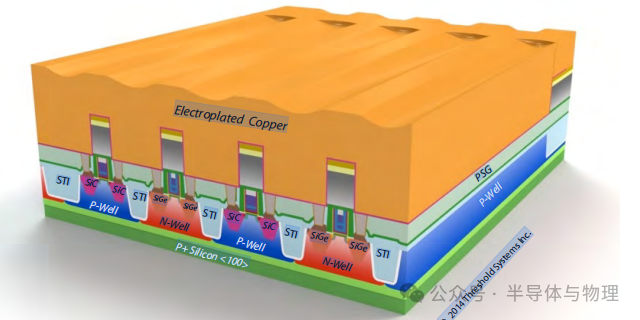

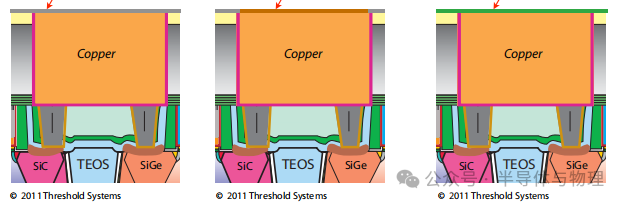

工藝步驟

刻蝕溝槽:在氧化層中刻蝕出納米級凹槽(深度50-100 nm,寬度10-20 nm);沉積阻擋層:用物理氣相沉積(PVD)或原子層沉積(ALD)生成2 nm厚的TaN;銅種子層與電鍍:PVD沉積銅種子層,電鍍填充銅;化學機械拋光(CMP):磨平表面,確保金屬線平坦化。

-

芯片

+關注

關注

459文章

52494瀏覽量

440652 -

CMOS

+關注

關注

58文章

6021瀏覽量

238838 -

NMOS

+關注

關注

3文章

365瀏覽量

35654 -

晶體管

+關注

關注

77文章

10019瀏覽量

141617

原文標題:CMOS第一層互聯(lián)

文章出處:【微信號:bdtdsj,微信公眾號:中科院半導體所】歡迎添加關注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

分享一個按鍵液晶多級菜單設計方法,附帶一個Linux液晶驅(qū)動

請教一下如何用protel畫實驗用的結(jié)構(gòu)?

單片機程序設計的十層功力,你練到那一層了?

控件快捷菜單選擇事件,能不能選擇不是最低一層的菜單?

單片機程序設計的十層功力,你練到那一層了?

單片機程序設計的十層功力,你練到那一層了?

PADS設計4板,第一層基板挖一個大矩形槽,露出第二層基板,再在第二層基板挖一個小矩形槽。請問怎么實現(xiàn)?

C語言單片機等待詢問_單片機程序設計有十層功力,你現(xiàn)在在哪一層?

CMOS第一層互聯(lián)的結(jié)構(gòu)與作用

CMOS第一層互聯(lián)的結(jié)構(gòu)與作用

評論