概述

ADI公司早期的ADSP-BF531、ADSP-BF532和ADSP-BF533產品系列具備Blackfin處理器的所有簡單易用和架構上的特性。這三個處理器全部完全引腳兼容,僅在其性能和片上存儲器方面有所不同,從而降低了風險,并提供根據終端應用要求進行靈活擴展的能力。所有這三個處理器都具備低功耗以及從低成本到極高性能的可擴展性能。

ADSP-BF531是Blackfin處理器系列的低成本切入點。它實現了性能、外設集成和價格之間的完美平衡,非常合適用于便攜式測試設備、嵌入式調制解調器、生物特征識別和消費類音頻等大多數對成本敏感的應用。

數據表:*附件:ADSP-BF531 ADSP-BF532 ADSP-BF533 400MHz低成本Blackfin處理器技術手冊.pdf

高集成度

- 52KB片上L1存儲器,可配置為

- 32KB L1指令存儲器SRAM/高速緩存

- 16KB L1數據存儲器SRAM/高速緩存

- 4 KB L1便箋式SRAM

- 并行外設接口,支持ITU-R 656視頻數據格式

- 兩個雙通道全雙工同步串行端口,支持八個立體聲I^2^S通道

- 12個DMA通道,支持一維和二維數據傳輸

- 存儲器控制器,提供與多組外部SDRAM、SRAM、閃存或ROM的無縫連接

- 3個定時器/計數器,支持PWM、脈寬和事件計數模式

- UART,支持IrDA?

- SPI兼容端口

- 事件處理器

- 實時時鐘

- 看門狗定時器

- 具備1至63倍倍頻能力的鎖相環

- 160焊球(12mm x 12mm)小型BGA封裝、176引腳(24mm x 24mm)LQFP封裝和169焊球(19mm x 19mm)無鉛Sparse PBGA封裝

特性

- 400MHz/800MMAC的性能可實現多媒體應用中的多通道音頻和CIF視頻處理

- 具備片上內核電壓調節功能的增強型動態電源管理可實現0.8V的工作電壓,從而延長便攜應用中的電池使用壽命

- 針對數據采集應用而優化的外設,提供與通用轉換器的無縫連接

- 低成本且引腳和代碼兼容的系列衍生產品,使得在成本敏感的消費類應用中的軟件差異化成為可能

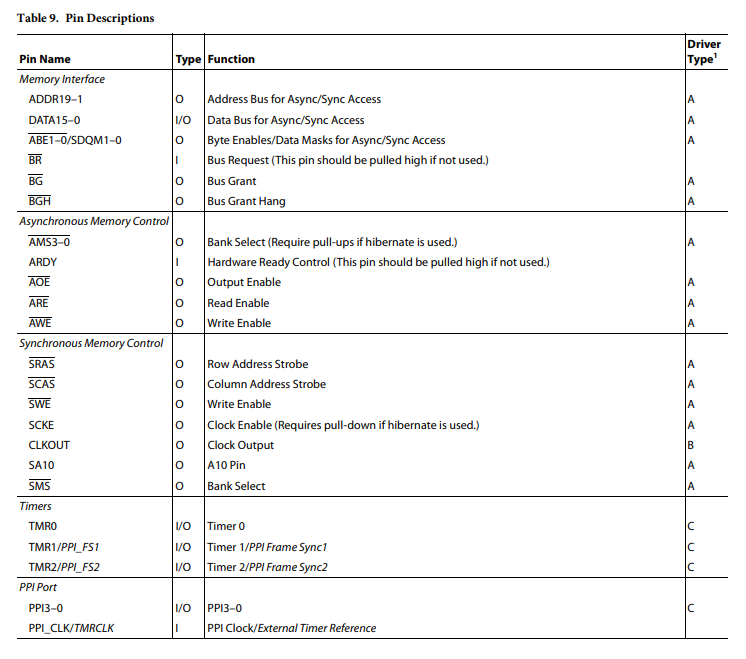

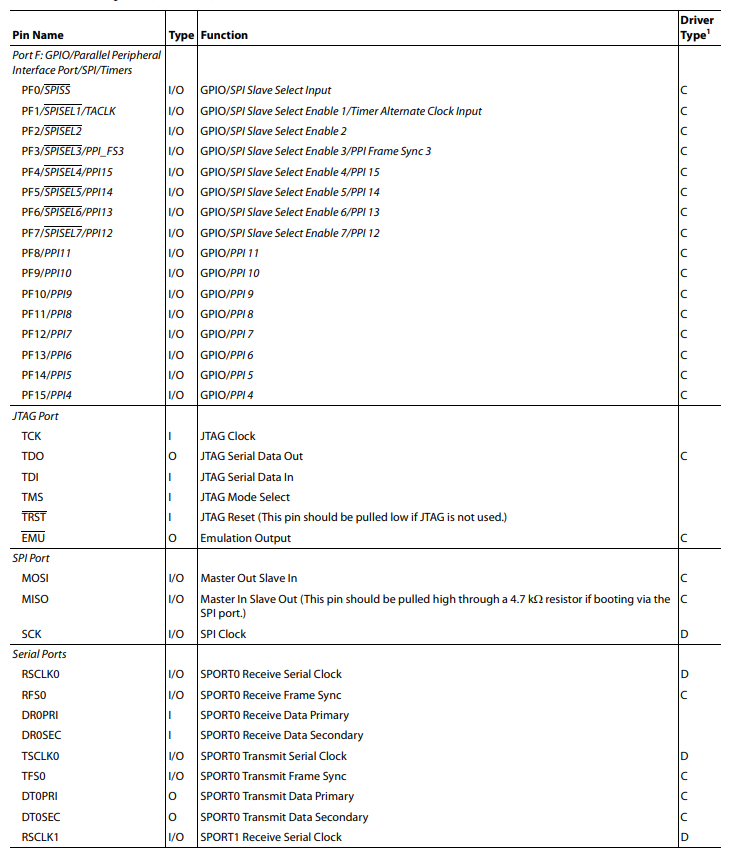

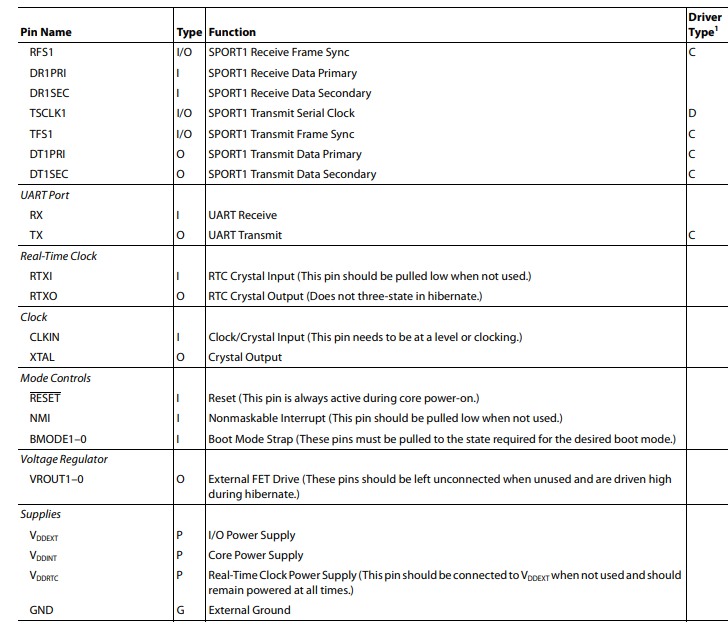

引腳說明

ADSP - BF531/ADSP - BF532/ADSP - BF533處理器的引腳定義見表9。

復位后,所有引腳均為三態,除了那些在系統時鐘期間異步控制內存的引腳,以及同步控制內存的引腳。這些引腳由CLKOUT驅動,在系統時鐘之外會進行翻轉,除非另有說明。表9中注明的所有輸出在復位期間均為三態。

如果(overline{BR})有效(無論(overline{RESET})是否置位 ),內存引腳也為三態。所有未使用的輸入/輸出(I/O)引腳的輸入緩沖器已禁用,除了那些需要上拉或下拉的引腳,具體見表中說明。

為了保持最大功能和減少封裝尺寸及引腳數量,一些引腳具有雙重復用功能。在引腳功能可配置的情況下,默認狀態以普通字體顯示,備用功能以斜體顯示。

測試條件

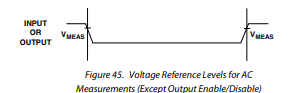

本數據手冊中出現的所有定時參數均在本節所述條件下測量。圖45展示了交流測量(輸出使能/禁用除外 )的測量點。測量點(V_{MEAS}),對于(V_{DDEXT})(標稱值 ) = 3.3V時為0.95V,對于(V_{DDEXT})(標稱值 ) = 1.8V時為1.5V,對于(V_{DDEXT})(標稱值 ) = 2.5V時為1.5V 。

輸出使能時間測量

當輸出引腳從高阻抗狀態轉變為開始驅動時,視為輸出引腳被使能。

輸出使能時間(t_{ENA})是從參考信號達到高電平或低電平,到輸出開始驅動的時間間隔,如圖46右側所示。

時間(t_{ENA_MEASURED})是參考信號切換到輸出電壓達到(V_{TRIP})(高 )或(V_{TRIP})(低 )的時間間隔。

對于(V_{DDEXT})(標稱值 ) = 1.8V,(V_{TRIP})(高 ) = 1.3V,(V_{TRIP})(低 ) = 0.7V 。

對于(V_{DDEXT})(標稱值 ) = 2.5V/3.3V,(V_{TRIP})(高 ) = 2.0V,(V_{TRIP})(低 ) = 1.0V 。

時間(t_{TRIP})是輸出從開始驅動到輸出電壓達到(V_{TRIP})(高 )或(V_{TRIP})(低 )的時間間隔。

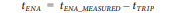

(t_{ENA})按以下公式計算:

如果多個引腳(如數據總線)被使能,測量值為第一個開始驅動的引腳的值。

圖46. 輸出使能/禁用

輸出禁用時間測量

當輸出引腳停止驅動并進入高阻抗狀態時,視為輸出引腳被禁用。

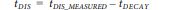

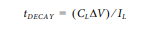

輸出禁用時間(t_{DIS})是輸出高電平或低電平開始從測量值下降(Delta V)的時間,它取決于電容負載(C_{L})和負載電流(I_{L}) 。此下降時間可通過以下公式近似計算:

時間(t_{DIS_MEASURED})和(t_{DECAY})如圖45左側所示。

示例系統保持時間計算

要確定特定系統中的數據輸出保持時間,首先使用上述公式計算(t_{DECAY}) 。選擇(Delta V)為處理器輸出電壓與所需保持時間的設備輸入閾值之間的差值。(C_{L})是總總線電容(每條數據線 ),(I_{L})是總泄漏或三態電流(每條數據線 )。保持時間為(t_{DECAY})加上各種輸出禁用時間,如第27頁“定時規格”中指定的時間(例如SDRAM寫周期中的(t_{DSWAT}) ,見第30頁“SDRAM接口定時” )。

(t_{DECAY})在測試負載(C_{L})和(I_{L}) 下計算,對于(V_{DDEXT})(標稱值 ) = 1.8V,(Delta V)等于0.1V;對于(V_{DDEXT})(標稱值 ) = 3.3V,(Delta V)等于0.5V 。

時間(t_{DEC_MEASURED})是參考信號切換到輸出電壓從測量輸出高電平或輸出低電平下降(Delta V)的時間間隔。

-

處理器

+關注

關注

68文章

19852瀏覽量

234190 -

Blackfin

+關注

關注

0文章

78瀏覽量

24950

發布評論請先 登錄

ADSP-BF532 400 MHz高性能Blackfin處理器

ADSP-BF531 400MHz低成本Blackfin處理器

ADSP-BF531/BF532/BF533 Blackfin?功耗估算(Rev 4, 12/2007)

ADSP-BF531/ADSP-BF532/ADSP-BF533:Blackfin嵌入式處理器數據表

EE-197:ADSP-BF531/532/533 Blackfin?處理器多周期指令和延遲

EE-262:ADSP-BF537 Blackfin?針對ADSP-BF533用戶的亮點

ADSP-BF531/BF532/BF533黑球BSDL 169球PBGA包(02/2004)

ADSP-BF531/BF532/BF533黑丙烯BSDL 176-Pin LQFP包(02/2004)

ADSP-BF531/BF532/BF533修訂版0.5、0.6的Blackfin異常列表

BF533-EZ ADSP-BF533 EZ-Kit Lite評估硬件為評估ADSP-BF531、ADSP-BF532和ADSP-BF533 Blackfin處理器系列提供低成本硬件解決方案。

ADSP-BF531BF532BF533 2.53.3V IO Blackfin處理器IBIS數據文件160-Ball CSP BGA封裝(092005)

EE-229: ADSP-BF531/BF532/BF533 Blackfin功耗估算

AN-813: ADSP-BF533/ADSP-BF561 Blackfin處理器與高速并行ADC接口

EE-197:ADSP-BF531/532/533 Blackfin處理器多周期指令和延遲

ADSP-BF531/ADSP-BF532/ADSP-BF533 400MHz低成本Blackfin處理器技術手冊

ADSP-BF531/ADSP-BF532/ADSP-BF533 400MHz低成本Blackfin處理器技術手冊

評論