AMD QDMA Subsystem for PCI Express( PCIe )旨在利用多隊列的概念實現(xiàn)高性能 DMA,以搭配 PCI Express Integrated Block 一起使用,它與 DMA/Bridge Subsystem for PCI Express 的不同之處在于,后者使用多個 AMD 卡到主機(jī)( C2H )和主機(jī)到卡( H2C )通道。

本指南適用于面向 AMD UltraScale+ 器件的 QDMA Subsystem for PCIe。

功能特性

AMD UltraScale+ 器件中支持 PCIe Integrated Block( PCIe 集成塊)。

支持 64、128、256 和 512 位數(shù)據(jù)路徑。

支持 x1、x2、x4、x8 或 x16 鏈路寬度。

支持 Gen1、Gen2 和 Gen3 鏈路速度。Gen4 用于 PCIE4C 和 PCIE4CE 塊。

支持 AXI4 存儲器映射接口和 AXI4-Stream 接口(按隊列)。

2048 個隊列集合

2048 個 H2C 描述符環(huán)。

2048 個 C2H 描述符環(huán)。

2048 個 C2H 完成( CMPT ) 環(huán)。

支持輪詢模式(狀態(tài)描述符寫回)和中斷模式。

中斷

2048 個 MSI-X 矢量。

每個功能最多 8 個 MSI-X。

中斷聚合。

C2H 串流中斷調(diào)制。

C2H 串流完成隊列條目合并。

通過用戶邏輯進(jìn)行描述符和 DMA 自定義

允許定制描述符格式。

流量管理。

支持含最多 4 個物理功能( PF )和 252 個虛擬功能( VF )的 SR-IOV

精簡虛擬機(jī)管理器型號。

QID 虛擬化。

僅允許有特權(quán)的功能/物理功能對上下文和寄存器進(jìn)行編程。

支持功能級別復(fù)位( FLR )。

郵箱。

基于隊列的豐富可編程性,例如,AXI4 存儲器映射接口對比 AXI4-Stream 接口。

概述

Queue-based Direct Memory Access( QDMA )基于隊列的直接存儲器訪問子系統(tǒng)是基于 PCI Express ( PCIe )的 DMA 引擎,該引擎專為滿足高帶寬和高包計數(shù)數(shù)據(jù)傳輸需求而優(yōu)化。QDMA 由 AMD UltraScale+ Integrated Block for PCI Express 以及廣泛的 DMA 和 Bridge 基礎(chǔ)架構(gòu)組成,可實現(xiàn)卓越的性能和靈活性。

QDMA Subsystem for PCIe 提供了廣泛的設(shè)置和使用選項,大部分設(shè)置和選項均可按隊列來選擇,例如存儲器映射 DMA 或串流 DMA、中斷模式和輪詢。該子系統(tǒng)提供了諸多選項,用于通過用戶邏輯來自定義描述符和 DMA,以提供復(fù)雜的流量管理功能。

QDMA 引擎可憑借使用 QDMA 進(jìn)行數(shù)據(jù)傳輸?shù)闹饕獧C(jī)制來對主機(jī)操作系統(tǒng)所提供的指令(描述符)進(jìn)行操作。QDMA 可使用描述符在主機(jī)到卡( H2C )方向或卡到主機(jī)( C2H )方向進(jìn)行數(shù)據(jù)移動。您可基于逐個隊列選擇 DMA 流量 是進(jìn)入 AXI4 存儲器映射( MM )接口還是進(jìn)入 AXI4-Stream 接口。此外,QDMA 可以選擇實現(xiàn) AXI4 MM 主端口或?qū)崿F(xiàn) AXI4 MM 從端口,從而允許 PCIe 流量完全繞過 DMA 引擎。

QDMA 與其他 DMA 產(chǎn)品的主要區(qū)別在于隊列的概念。隊列的概念源自高性能計算( HPC )互連的遠(yuǎn)程直接存儲器訪問( RDMA )的“隊列集”概念。這些隊列可以通過接口類型進(jìn)行單獨配置,并且能夠在許多不同的模式下工作。基于單個隊列加載 DMA 描述符的方式,每個隊列均可提供極低開銷的建立時間選項和連續(xù)更新功能。通過將隊列作為資源分配給多個 PCIe 物理功能( PF )和虛擬功能( VF ),即可在各種多功能和虛擬化應(yīng)用空間中使用同一個 QDMA 核與 PCI Express 接口。

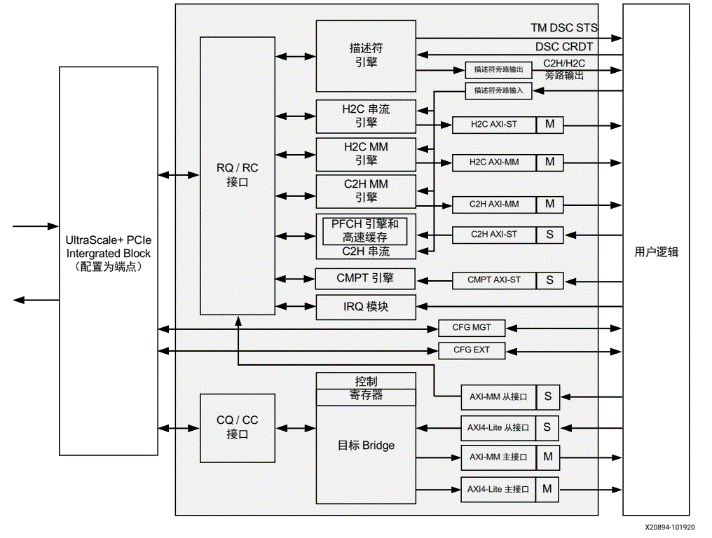

QDMA 架構(gòu)

下圖顯示了 QDMA Subsystem for PCIe 的模塊框圖。

-

amd

+關(guān)注

關(guān)注

25文章

5584瀏覽量

136280 -

存儲器

+關(guān)注

關(guān)注

38文章

7648瀏覽量

167228 -

UltraScale

+關(guān)注

關(guān)注

0文章

122瀏覽量

31892

原文標(biāo)題:QDMA Subsystem for PCI Express v5.0 產(chǎn)品指南

文章出處:【微信號:賽靈思,微信公眾號:Xilinx賽靈思官微】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

DLC發(fā)布V5.0版本增加哪些測試要求

DLC美國能效V5.0標(biāo)準(zhǔn)的測試內(nèi)容

PCI Express插槽,什么是PCI Express插槽

Sprint-Layout V5.0免安裝中文版

力科推出PCI Express 5.0開放網(wǎng)絡(luò)接口卡3.0信號采集卡

QDMA Subsystem for PCI Express產(chǎn)品指南

UltraScale+器件用于PCI Express的集成模塊產(chǎn)品指南

DMA/Bridge Subsystem for PCI Express v4.1指南

用于PCI Express的Versal ACAP集成塊產(chǎn)品指南

用于PCI Express v2.1的Versal ACAP CPM模式產(chǎn)品指南

UltraScale+器件Integrated Block for PCI Express v1.3產(chǎn)品指南

QDMA Subsystem for PCI Express v5.0產(chǎn)品指南

QDMA Subsystem for PCI Express v5.0產(chǎn)品指南

評論