DesignCon會(huì)議自舉辦以來(lái)一直都為我們帶來(lái)業(yè)內(nèi)最新的PCB layout和仿真軟件工具。在DesignCon 2018期間,我有幸采訪了Cadence的產(chǎn)品工程師Sam Chitwood先生。 Chitwood先生向我們解釋了Cadence? Sigrity?的仿真軟件如何允許用戶在設(shè)計(jì)的早期階段就作出決定,以及這樣做如何有助于優(yōu)化電源分配網(wǎng)絡(luò)的設(shè)計(jì)并確保復(fù)雜PCB中的信號(hào)完整性。

Kelly Dack

現(xiàn)在我和Sam Chitwood都在DesignCon會(huì)議上。我了解到現(xiàn)在Sigrity工具可以解決電源完整性方面的一些問(wèn)題。我們先來(lái)聊一聊設(shè)計(jì)師和工程師在電源完整性方面遇到了哪些問(wèn)題好嗎?

Sam Chitwood

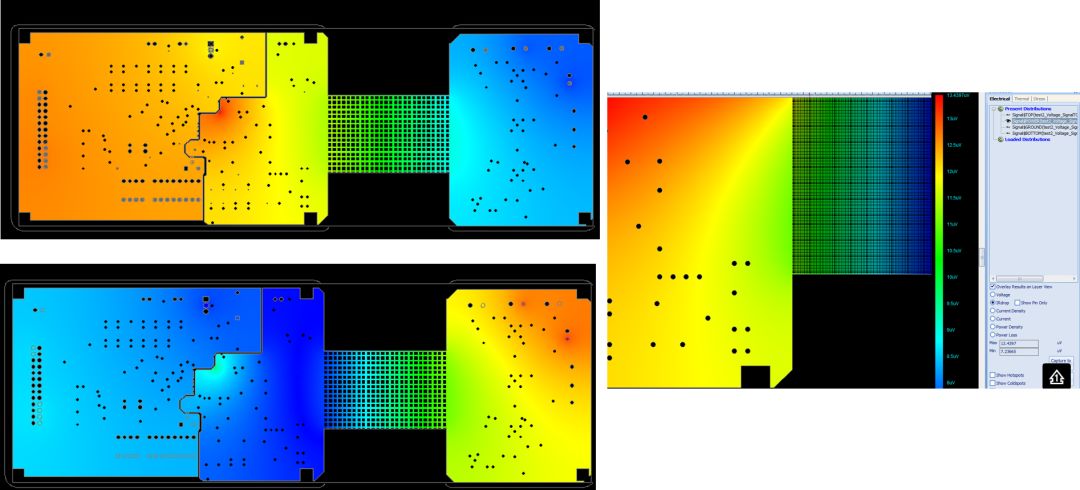

電源完整性問(wèn)題有兩個(gè)不同的方面:直流和交流。前者要求從根本上為器件提供充足的直流電源。就像你過(guò)去使用的移動(dòng)電子設(shè)備一樣,必須要有電池——一個(gè)直流電源。直流問(wèn)題的起因在于大電流和布線金屬不足的共同作用。

交流電源的完整性可以從頻域和時(shí)域兩方面考慮。在頻域中,我們力求在相關(guān)帶寬上獲得平坦的阻抗分布。在時(shí)域中,以許多正在切換的I/O為例:如果它們的電源由于噪聲較大而不穩(wěn)定,那么噪聲將在這些輸出上表現(xiàn)為信號(hào)衰減。這種現(xiàn)象稱為同步開(kāi)關(guān)噪聲(簡(jiǎn)稱SSN),由此說(shuō)明了電源完整性問(wèn)題是如何影響信號(hào)完整性問(wèn)題的。 Sigrity工具的特殊之處就在于它們可以在時(shí)域和頻域兩個(gè)方面同時(shí)進(jìn)行信號(hào)、電源和地仿真。

Kelly Dack

仿真發(fā)生在前端、后端、還是兩者均可呢?請(qǐng)告訴我們它最適用的地方。

Sam Chitwood

以往,大多數(shù)電源完整性仿真都是在布局后,接近設(shè)計(jì)周期的末期進(jìn)行的。但是顯然這種做法并不理想。設(shè)計(jì)末期的每個(gè)人都很繁忙,幾乎沒(méi)有人有足夠的時(shí)間去執(zhí)行優(yōu)化設(shè)計(jì)或降低成本。PI工程師更是幾乎沒(méi)有時(shí)間去執(zhí)行驗(yàn)收分析以判斷設(shè)計(jì)的好壞。

實(shí)際上,過(guò)去兩年我們一直在做的就是實(shí)現(xiàn)設(shè)計(jì)上的“左移/前移”(我的同事Brad Griffin喜歡使用這個(gè)形象的稱呼)。意即:如何將所有類型的仿真分析移到設(shè)計(jì)周期的早期?以下是從原理圖角度的一個(gè)示例:電源網(wǎng)絡(luò)是否有足夠的去耦電容?是否有正確的去耦電容?這些問(wèn)題恐怕大多數(shù)原理圖設(shè)計(jì)工程師都無(wú)法回答。我們的目的就是把以往僅在設(shè)計(jì)周期即將結(jié)束時(shí)才做的工作、那些PI專家?guī)缀鯖](méi)有充足時(shí)間去進(jìn)行檢查的工作,提前到設(shè)計(jì)周期早期來(lái)做,并開(kāi)放給設(shè)計(jì)工程師和layout工程師來(lái)協(xié)助完成。那么問(wèn)題來(lái)了,你認(rèn)為提前到設(shè)計(jì)周期早期協(xié)助完成電源完整性工作意味著什么?

Kelly Dack

“提前”對(duì)我來(lái)說(shuō),大概意味著從電路原理圖階段入手。

Sam Chitwood

沒(méi)錯(cuò),我們的目標(biāo)是從一開(kāi)始就讓原理圖設(shè)計(jì)人員參與進(jìn)來(lái)。他們需要一種簡(jiǎn)便、快捷的自動(dòng)化方式來(lái)提供有用的可操作的信息。例如,是否選擇了正確的去耦電容?原理圖設(shè)計(jì)人員一開(kāi)始就需要這些信息,而不是讓PI專家在最后緊要關(guān)頭說(shuō)“你選擇的去耦電容一直都是錯(cuò)的”。這樣的話,設(shè)計(jì)人員就必須進(jìn)行返工。而從電源分配布線的角度來(lái)看,這相當(dāng)于要全部重做了。顯然,代價(jià)是非常昂貴的。

Kelly Dack

對(duì)于那些可能沒(méi)有接受過(guò)仿真培訓(xùn)的新手而言,請(qǐng)解釋一些仿真的要素,比如元件、數(shù)據(jù)表以及我們要尋求什么結(jié)果。

Sam Chitwood

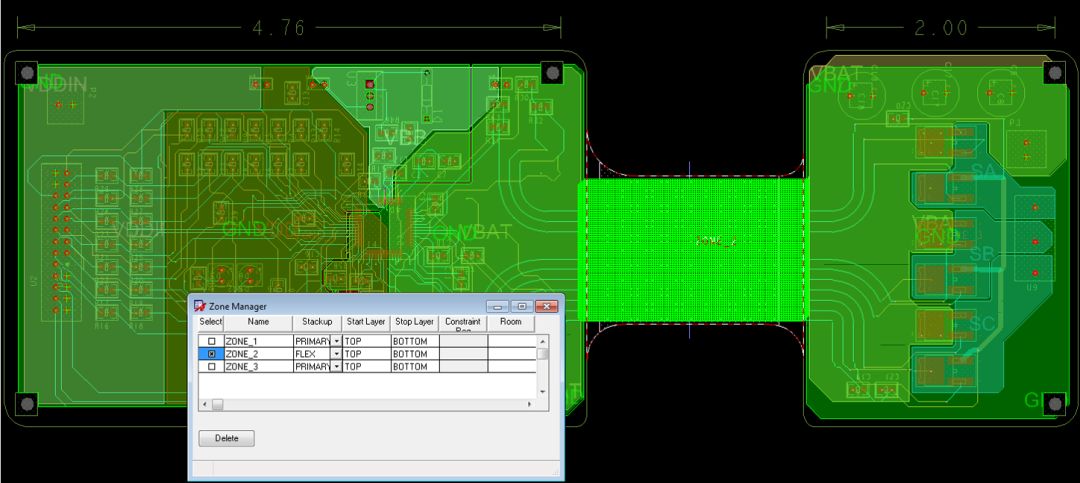

對(duì)于一個(gè)可能是仿真新手的layout工程師來(lái)說(shuō),我們用一個(gè)很好的例子來(lái)解釋他都能夠做些什么。在我們的軟件里,PDN電感檢查是非常容易獲取的,絕對(duì)不需要電氣模型。Layout工程師需要的僅僅是包含正確層疊和指定電源網(wǎng)絡(luò)名稱的layout數(shù)據(jù)庫(kù)。通過(guò)這些信息,我們的軟件可以自動(dòng)識(shí)別元件名稱以及它們的位置。至于 IC器件,我們解決了IC與其每個(gè)去耦電容之間的環(huán)路電感。這么做的目的很簡(jiǎn)單,結(jié)果也很直觀:識(shí)別所有異常的去耦電容。在確定具體問(wèn)題之后,layout設(shè)計(jì)人員可以檢查是否有不正確的布線或者是否有去耦電容被放置得太遠(yuǎn)。這些去耦電容是否需要被移動(dòng)或從頂層換到底層等等。這些問(wèn)題都可以很快被發(fā)現(xiàn)并提前進(jìn)行糾正。

Kelly Dack

你這里說(shuō)的“提前“就不是指原理圖設(shè)計(jì)階段了吧?

Sam Chitwood

是的,我剛剛說(shuō)的例子適用于layout設(shè)計(jì)人員。現(xiàn)在,讓我們“前移/左移”到原理圖設(shè)計(jì)人員。正如我之前提到的,原理圖設(shè)計(jì)人員需要在一開(kāi)始沒(méi)有可用layout的情況下就知道應(yīng)該選擇哪些去耦電容。而這一關(guān)鍵在于PDN的目標(biāo)阻抗。我們倡議為系統(tǒng)客戶提供芯片的IC供應(yīng)商提供目標(biāo)阻抗數(shù)據(jù),以便原理圖設(shè)計(jì)人員據(jù)此設(shè)計(jì)出恰好合格的性能方案。由于沒(méi)有目標(biāo)阻抗數(shù)據(jù)參考,原理圖設(shè)計(jì)人員從根本上受困于“過(guò)猶不及“的兩難境地。正如有些設(shè)計(jì)師所說(shuō)的:“我可以繼續(xù)添加去耦電容,并且可以繼續(xù)提高性能,但是該提高到什么程度呢?”沒(méi)有目標(biāo)阻抗,就沒(méi)有辦法真正知道設(shè)計(jì)是否達(dá)成,更沒(méi)有辦法判定設(shè)計(jì)的好壞。這種情況通常會(huì)導(dǎo)致過(guò)度設(shè)計(jì)去耦電容和不必要的BOM成本。

Kelly Dack

那好,我們獲得了一個(gè)目標(biāo)阻抗,并且我們?cè)缭谠韴D階段就使用了仿真分析工具。那么我們何時(shí)可以確定添加額外的板層會(huì)提高電源完整性呢?請(qǐng)告訴我們,如何運(yùn)用Sigrity工具來(lái)確定層疊和板層。

Sam Chitwood

PDN層疊設(shè)計(jì)是一個(gè)很好的介于原理圖和layout兩者之間的設(shè)計(jì)區(qū)域。我們將此稱為PDN的預(yù)布局。

Kelly Dack

因?yàn)槲覀冚p易就可以在設(shè)計(jì)中添加一層。但是我們?nèi)绾沃肋@會(huì)在多大程度上幫助我們實(shí)現(xiàn)成本合理化呢?

Sam Chitwood

PDN預(yù)布局是我們創(chuàng)建的工作流程之一,可以幫助指導(dǎo)用戶選擇層疊和PDN層分配。用戶選擇將電源層放置在層疊的頂部或是底部、以及選擇在頂部或底部表面放置去耦電容,都會(huì)對(duì)性能造成差異極大的影響。這些關(guān)鍵決策都是我們的工具可以自動(dòng)化仿真分析,并且生成去耦電容配置準(zhǔn)則。在這里,不要將這些去耦電容準(zhǔn)則視為強(qiáng)制規(guī)定,而應(yīng)將其視為基于分析基礎(chǔ)的建議。我們提供了三種去耦電容推薦列表:頂層、底層以及電路板背面元器件下方的去耦電容。基于這三種預(yù)布局去耦電容的配置列表,layout工程師便清楚知道要做什么了。該方法比傳統(tǒng)的“盡可能靠近元器件放置去耦電容”的經(jīng)驗(yàn)法則要優(yōu)越很多。

Kelly Dack

這可以讓layout設(shè)計(jì)人員根據(jù)設(shè)計(jì)中的其它目標(biāo)參數(shù)來(lái)進(jìn)行布局設(shè)計(jì)。例如,很多設(shè)計(jì)都是力求單面組裝,因此設(shè)計(jì)人員知道成本是多少、知道將元件和電容作為單獨(dú)的部件添加到電路板背面的成本。但他是否也知道這提升了多少性能,能否做個(gè)成本分析?

Sam Chitwood

當(dāng)然可以。我們工具獨(dú)一無(wú)二的特點(diǎn)之一就是能夠?qū)⒊杀拘畔⒓{入去耦電容優(yōu)化分析。在同類型的工程工具中,允許用戶在電氣性能與BOM成本之間進(jìn)行權(quán)衡決策的產(chǎn)品并不常見(jiàn)。而我們的產(chǎn)品可以讓用戶知道每個(gè)元件成本、裝配成本以及BOM庫(kù)存成本(或是在裝配期間存儲(chǔ)該元件的成本),從而進(jìn)行成本分析。

Kelly Dack

本次展會(huì)上很多與會(huì)者都十分關(guān)心高速信號(hào)和信號(hào)完整性問(wèn)題,但也有設(shè)計(jì)工程師在應(yīng)對(duì)、處理所有的“設(shè)計(jì)制約因素”。我們現(xiàn)在有“控制成本設(shè)計(jì)”參數(shù),有“可制造/生產(chǎn)性設(shè)計(jì)”約束。我們談到了諸如把元器件放在電路板的這一邊或另一邊之類的問(wèn)題;DFX,或叫“卓越設(shè)計(jì)”。你們的工具則可以直接解決成本問(wèn)題。

Sam Chitwood

是的,直接從去耦電容BOM的角度來(lái)看,或者間接從層疊和DC直流電源的角度來(lái)看都可以解決成本問(wèn)題。

Kelly Dack

那么作為結(jié)束話題,我們不妨來(lái)討論下關(guān)于DC直流電源。DC直流電源是個(gè)很大的話題。

Sam Chitwood

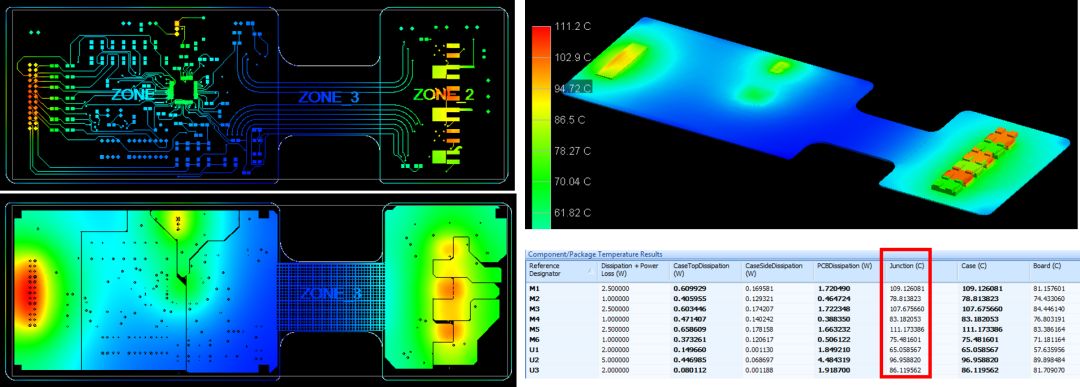

據(jù)我所知,Cadence Sigrity PowerDC? 是第一個(gè)將電和熱組合到一個(gè)協(xié)同仿真環(huán)境中的技術(shù)工具,僅僅只需一個(gè)按鈕,用戶就可以在同一個(gè)GUI界面內(nèi)獲得電結(jié)果和熱結(jié)果。可以想象,這項(xiàng)技術(shù)會(huì)有多么炙手可熱。例如,一個(gè)特定的過(guò)孔可以允許通過(guò)多大電流?將10安培從一層移動(dòng)到另一層需要多少個(gè)過(guò)孔? Sigrity技術(shù)是該領(lǐng)域應(yīng)用的先驅(qū)。

Kelly Dack

因?yàn)槭请娫聪嚓P(guān),因此也是熱相關(guān)的?

Sam Chitwood

是的,電和熱是緊密相關(guān)的。開(kāi)玩笑地說(shuō),你永遠(yuǎn)不想看到一封提到“火”的電子郵件。我看到過(guò)客戶們用其他一些創(chuàng)造性的方式向管理層描述他們所遇到這個(gè)情況。例如,對(duì)于一個(gè)器件,他們可能會(huì)說(shuō)發(fā)生了“放熱事件”。另一個(gè)很好的例子是PCB的“光炭化”,但我個(gè)人最喜歡的是“過(guò)孔炸彈”。

Kelly Dack

我從未聽(tīng)說(shuō)過(guò)這些。不過(guò)我們常說(shuō):“如果它變暖,沒(méi)關(guān)系;如果它變熱,也沒(méi)關(guān)系;但當(dāng)它冒煙時(shí),就意味著失敗了。”

Sam Chitwood

同意!我們有一位客戶來(lái)找我們就是為了熱問(wèn)題:他們發(fā)生了級(jí)聯(lián)故障,導(dǎo)致電路板上的過(guò)孔熔化。他們認(rèn)為他們有足夠數(shù)量的過(guò)孔,但分析顯示這些過(guò)孔并未正確放置。

Kelly Dack

電路板材料通常不被制造或設(shè)計(jì)成擁有處理熱問(wèn)題的能力。熱是電路板的大敵。無(wú)論是否“爆炸”,Z軸熱膨脹對(duì)于過(guò)孔來(lái)說(shuō)都十分糟糕。

Sam Chitwood

我們要記住FR-4中的“FR”代表阻燃,并不防火!

Kelly Dack

您還有什么要告訴大家的嗎?

Sam Chitwood

Cadence近期發(fā)布了新的電源完整性實(shí)用技術(shù)Allegro PowerTree? 工具。該工具可在原理圖設(shè)計(jì)人員、layout設(shè)計(jì)人員和PI專家之間共享PI分析的新的生態(tài)系統(tǒng)。我們希望真正實(shí)現(xiàn)PI方法的自動(dòng)化,在該方法中,所有這三種用戶都可以為PDN分析做出貢獻(xiàn),最終在預(yù)算和截至日期內(nèi)實(shí)現(xiàn)設(shè)計(jì)優(yōu)化。

Kelly Dack

請(qǐng)向我們介紹下PowerTree?工具以及它是如何處理PI問(wèn)題的。

Sam Chitwood

我們的目標(biāo)是實(shí)現(xiàn)直流和交流仿真的自動(dòng)設(shè)置,讓過(guò)去非常復(fù)雜的問(wèn)題變得非常簡(jiǎn)單。例如,大型服務(wù)器主板上的電源部分可能非常復(fù)雜,有數(shù)十個(gè)與之關(guān)聯(lián)的網(wǎng)絡(luò)名稱。這些網(wǎng)絡(luò)名稱并不易讀,因?yàn)樗鼈兪亲詣?dòng)生成的、隨機(jī)的文本字符串。顯然,任何人都不愿意跟蹤這些名字。PowerTree?工具能夠自動(dòng)識(shí)別從源到全部負(fù)載的所有電源網(wǎng)絡(luò),實(shí)現(xiàn)元件,例如濾波電感、電阻、電容的自動(dòng)識(shí)別與分配型號(hào);還可實(shí)現(xiàn)自動(dòng)應(yīng)用檢測(cè)約束,例如每個(gè)引腳的壓降和目標(biāo)阻抗。而仿真過(guò)程實(shí)際上也僅僅只需幾個(gè)按鈕就可以自動(dòng)完成。

Kelly Dack

哇,聽(tīng)起來(lái)很簡(jiǎn)單。

Sam Chitwood

是的,無(wú)論從DC直流還是AC交流的角度來(lái)看都是這樣的。我相信你知道Cadence是以基于信號(hào)完整性規(guī)則約束下的布線而聞名的。我們希望在電源完整性方面做出同樣的成就。我們有許多類型的DC約束和AC目標(biāo)阻抗約束。只要提供了這些限制條件,那么從原理圖階段到整個(gè)設(shè)計(jì)周期直至電路板驗(yàn)收的各個(gè)環(huán)節(jié),PCB設(shè)計(jì)人員都可以保證得到正確的電源分配。

最后,我們?cè)贒esignCon有一家IC供應(yīng)商介紹了他們?nèi)绾螢镻CB客戶提供目標(biāo)阻抗的流程。我們希望能廣泛傳播這種方法,以便整個(gè)行業(yè)都可以從中受益。

-

電源

+關(guān)注

關(guān)注

185文章

18356瀏覽量

256051 -

pcb

+關(guān)注

關(guān)注

4365文章

23480瀏覽量

409168 -

信號(hào)完整性

+關(guān)注

關(guān)注

68文章

1444瀏覽量

96693

原文標(biāo)題:DesignCon2018專題采訪:如何在設(shè)計(jì)周期早期自動(dòng)實(shí)現(xiàn)電源完整性仿真

文章出處:【微信號(hào):CadencePCB,微信公眾號(hào):CadencePCB和封裝設(shè)計(jì)】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

【高手問(wèn)答】9年IC布局工程師來(lái)做客,聊聊PADS、信號(hào)完整性

【信號(hào)完整性工程師】和【硬件測(cè)試工程師】

分享資深硬件工程師視頻講解信號(hào)完整性原理

分享資深硬件工程師用cadence仿真DDR3 SDRAM視頻---- sigxplorer信號(hào)完整性仿真例子 ...

信號(hào)完整性為什么寫(xiě)電源完整性?

信號(hào)完整性(SI)和電源完整性(PI)的基本原理理解

28小時(shí)從數(shù)字電路工程師到信號(hào)完整性工程師

信號(hào)完整性工程師工作職責(zé)

信號(hào)完整性工程師的最佳伴侶_圖書(shū)推薦

信號(hào)完整性工程師總結(jié)的精華100例

信號(hào)完整性為什么寫(xiě)電源完整性?

什么是信號(hào)完整性?

電源完整性仿真:電子工程師的必讀指南

設(shè)計(jì)師和工程師在電源完整性方面遇到了哪些問(wèn)題好嗎?

設(shè)計(jì)師和工程師在電源完整性方面遇到了哪些問(wèn)題好嗎?

評(píng)論