本文轉發連云港杰瑞電子有限公司的臧艷麗等發表在《電子工藝技術》上的“基于疊層組裝和雙腔體結構的高密度集成技術”,文中基于芯片堆疊和多層HTCC管殼開發了一款產品,在此予以介紹,供大家學習。

01雙腔產品結構設計

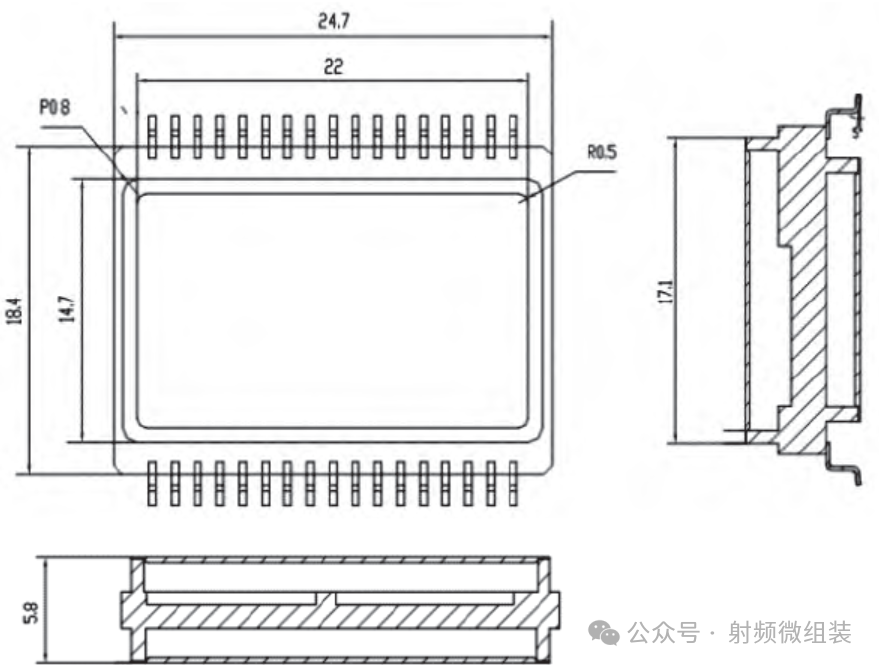

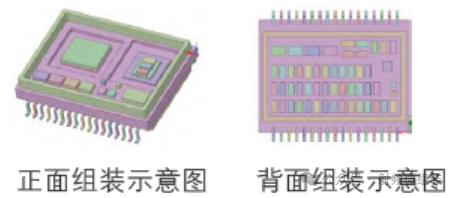

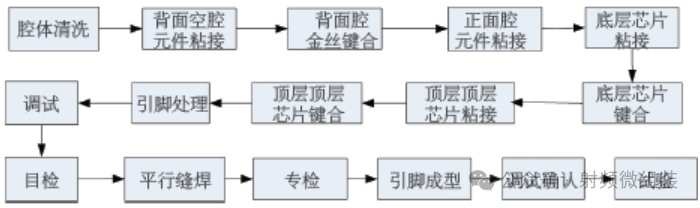

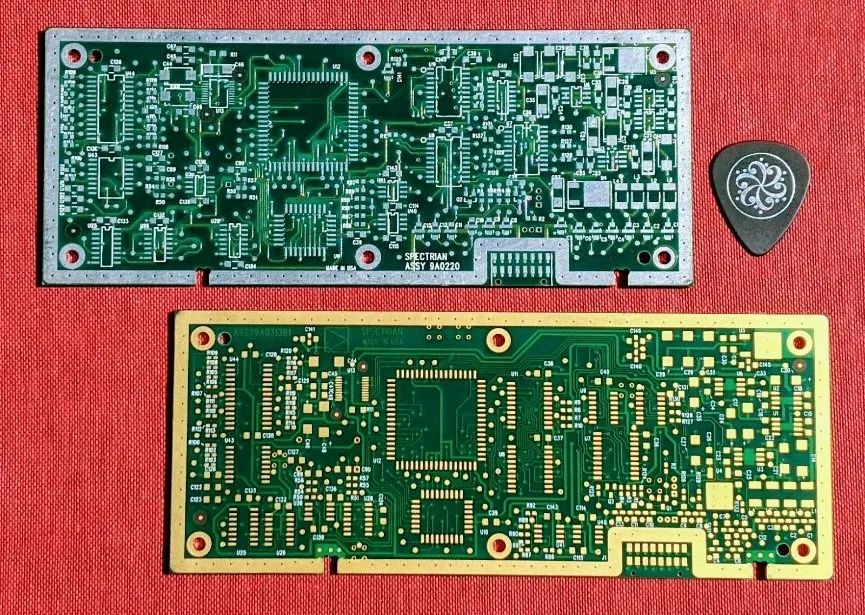

產品集成11顆芯片,58個無源元件,采用雙面陶瓷管殼作為載體,進行雙層芯片疊裝和組裝,實現高密度集成。殼體工藝采用高溫多層陶瓷共燒工藝,可以最大限度地增加布線密度和縮短互連線長度,從而提高組件密度和信號傳輸速度。如下圖所示,腔體內部設計兩層深腔,留有多層芯片疊裝的立體組裝空間,設計兩層臺階鍵合區域,便于空間鍵合走線實現電氣連接。陶瓷基板上設計電路,通過金絲鍵合實現電氣互連。雙面組裝完成后進行雙面平行封焊,最后進行引腳成型。

02關鍵工藝技術

1)三維芯片堆疊技術

芯片堆疊結構有三種典型的疊裝方式:1)小芯片疊裝大芯片的金字塔式;2)芯片兩側出鍵合線的十字交叉式;3)同尺寸的芯片通過墊片疊裝的懸臂梁式。前兩種芯片堆疊方式難度不大,本部分重點分析懸臂梁式芯片疊裝。

該技術難點主要有三個:1)芯片與墊片粘接、芯片與芯片粘接材料的選擇,既要具有較高粘接強度又要具有緩沖結構應力的能力,以適應芯片疊裝的應用;2)控制芯片與芯片間粘接膠量,避免溢出膠污染到鍵合區,需要采用自動粘接設備;3)空間鍵合難度大,疊層芯片組裝的垂直空間極為有限,因此要求鍵合線必須具有盡可能低的弧高,采用反向鍵合的工藝方法,適當的時候使用等離子清洗避免洇膠影響鍵合質量。

2)一體化雙面腔體組裝技術

該技術可實現高密度模塊的組裝,雙面安裝元器件,實現立體組裝,較單腔模塊體積可縮小1/3以上,雙面腔體密封,耐環境應力可靠性高。該技術主要有兩個工藝難點:1)雙面腔體元器件的粘接、鍵合工藝;2)雙面腔體封焊技術。封焊技術目前有激光封焊、平行縫焊、真空熔焊等,根據所選擇的工藝和腔體材料的不同,選擇合適的封焊技術。

3)后引腳成型技術

引腳作為電氣連接和結構支撐的用途,設計類似芯片小外形封裝,兩側出引腳數量34根,引腳材料采用柯伐合金材料。產品通過引腳與印制板實現電氣連接,整個大腔體依靠引腳支撐存在風險,設計增加背面腔體也起到結構支撐作用。如果采用背面同步焊接的方式,引腳成型過程需要確保引腳底面與底層腔體蓋板面共平面,需要定制專門的工裝,背面腔與引腳的共面性要求高度差小于0.1 mm,這對引腳成型過程的控制要求更高。另一種方式采用側面打膠加固,此方法對引腳底面和底層腔體的共面性要求不高,引腳成型工藝更容易實現。

03芯片疊層和雙腔體工藝設計

1)客戶使用工藝性設計

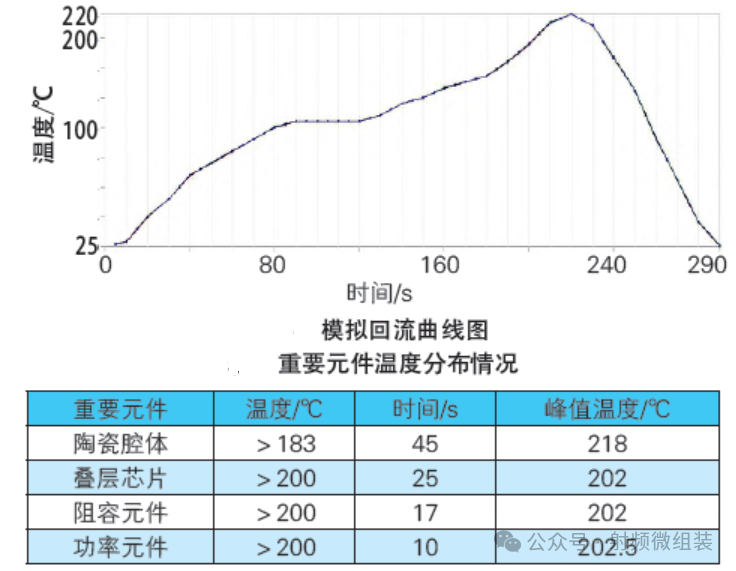

客戶使用的是采用貼裝的方式將轉換器組裝到印制板上,通過34根引腳與印制板實現電氣連接,背面蓋板表面鍍鎳,通過Sn63Pb37與印制板表面焊接固定,焊料共晶溫度點183 ℃,側面點膠加固,背面蓋板和引腳同時起固定支撐作用。

模擬回流焊接曲線如下圖所示,經過回流焊接過程各重要器件溫度分布情況見下表。

通過溫度分布結果顯示:芯片、元器件超過200 ℃的時間均控制在25 s以內,雙腔體封裝后的產品經過回流焊接,溫度分布對元器件影響不大,產品元件的可耐受峰值溫度和時間可控。

2)可靠性預測分析

高密度集成封裝中,芯片疊層技術是封裝中的薄弱點,因為芯片、墊片、陶瓷管殼三種材料熱膨脹系數存在差異,硅芯片又屬于脆性材料,粘接材料的選擇是提高芯片堆疊可靠性的基礎,通過查閱相關文獻,選擇低應力粘接材料,匹配真實的產品數據進行了溫度沖擊、機械沖擊、恒定加速度模擬分析,可靠性試驗模擬結果見下表。通過預測模擬分析結果顯示:1)在經受-65~150 ℃溫度循環試驗時,每種材料由于收縮程度不一致,芯片疊裝結構內部會產生內應力,2層芯片堆疊結構的最大應力100MPa,硅的破壞強度較高,在5~10GPa,實際損壞強度遠低于理論強度,只有30%~70%,,按照30%的破壞強度,受到的應力依然是小于芯片材料的強度值,不會出現芯片開裂的問題,芯片翹曲變形最大是在最頂層,變形量最小是在最底層。

2)機械沖擊條件1500g ,0.5ms的條件作用于模型結構,芯片受到最大等效應力5.83MPa小于Si芯片的損壞強度;恒定加速度5000g ,Y2方向時間1min,芯片受到的等效最大應力5.57MPa遠小于芯片的損壞強度,芯片間的絕緣膠在機械沖擊和恒定加速度條件下,對芯片有緩沖作用,芯片受到的應力遠小于芯片的破壞強度。

基于真實的產品數據進行了溫度沖擊、隨機振動、恒定加速度模擬分析,結果證明該產品的低應力粘接膠和結構能夠滿足產品的使用要求。

-

芯片

+關注

關注

460文章

52520瀏覽量

441169 -

無源元件

+關注

關注

1文章

1289瀏覽量

17227 -

芯片堆疊

+關注

關注

0文章

19瀏覽量

14738 -

陶瓷基板

+關注

關注

5文章

246瀏覽量

11846

原文標題:基于疊層組裝和雙腔體結構的高密度集成技術

文章出處:【微信號:深圳市賽姆烯金科技有限公司,微信公眾號:深圳市賽姆烯金科技有限公司】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

器件高密度BGA封裝設計

高密度印制電路板(HDI)簡介

高密度電路板的塞孔制程

探討高密度小間距LED屏工藝

高速高密度PCB設計的關鍵技術問題是什么?

高密度PCB(HDI)檢驗標準

Cyntec高密度uPOL模塊的特點

什么是高密度DDR芯片

高密度封裝失效分析關鍵技術和方法

基于疊層組裝和雙腔體結構的高密度集成技術

基于疊層組裝和雙腔體結構的高密度集成技術

評論