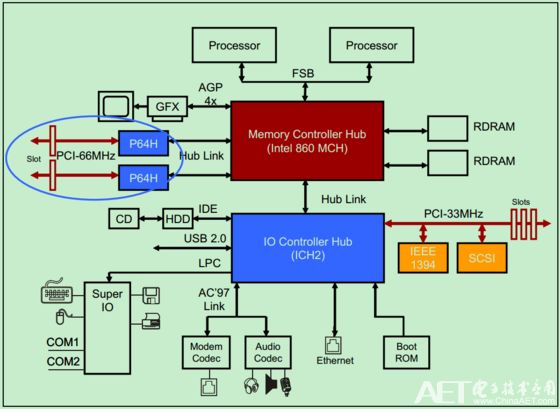

為了能夠取得更高的帶寬,新版本的PCI Spec將PCI總線提高到了64-bit并將頻率提高到了66MHz,最高支持533MB/s。下圖描述的是一個(gè)典型的66Mhz,64-bit的PCI系統(tǒng)結(jié)構(gòu)圖。

前面的文章介紹過(guò),PCI總線采用了Reflected-Wave Signaling技術(shù),因此總線頻率的提高,必然會(huì)導(dǎo)致總線負(fù)載能力的降低。結(jié)果就是,66MHz 64-bit的PCI總線只能支持一個(gè)PCI插卡設(shè)備(算作兩個(gè)PCI設(shè)備,插槽和PCI卡各算一個(gè))。為了增加整個(gè)系統(tǒng)的PCI設(shè)備數(shù),就不得不去增加額外的PCI橋,這又進(jìn)一步增加了功耗,提高了成本。此外,64-bit的PCI總線由于增加了很多的引腳,導(dǎo)致66MHz 64-bit的PCI總線的穩(wěn)定性降低,對(duì)PCB的設(shè)計(jì)提出了更高的要求,也限制了其廣泛應(yīng)用。

此外,由于PCI總線采用的是non-registered輸入,這要求輸入信號(hào)的建立時(shí)間至少要有3ns,而66MHz的時(shí)鐘下,周期為15ns,剩余的12ns基本上都被Reflected-Wave Signaling給消耗了。因此,66MHz基本上算是PCI總線的頻率的上限了。

在PCI-X總線中,為了解決上訴問(wèn)題,PCI-X總線將所有的輸入信號(hào)都先用寄存器打一拍,此時(shí)對(duì)輸入信號(hào)的建立時(shí)間的要求就不在那么苛刻了,因此PIC-X總線可以運(yùn)行在更高的頻率上(100MHz,甚至133MHz)。

-

負(fù)載

+關(guān)注

關(guān)注

2文章

616瀏覽量

35267 -

PCI

+關(guān)注

關(guān)注

5文章

679瀏覽量

132141 -

頻率

+關(guān)注

關(guān)注

4文章

1562瀏覽量

60396 -

功耗

+關(guān)注

關(guān)注

1文章

836瀏覽量

32685

原文標(biāo)題:【博文連載】PCIe掃盲——66MHz的PCI總線與其技術(shù)瓶頸

文章出處:【微信號(hào):ChinaAET,微信公眾號(hào):電子技術(shù)應(yīng)用ChinaAET】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

把老版本AD升級(jí)到最新版本AD19的方法

使用新版本IAR編譯老版本的STM32工程

如何使用更新版本的MbedTLS?

FilterPro v3.0設(shè)計(jì)工具的最新版本

谷歌發(fā)布Chrome新版本

OpenVINO? 2022.2新版本有哪些亮眼的新特性

關(guān)于博達(dá)透?jìng)鞴ぞ?b class='flag-5'>新版本升級(jí)公告

CANoe新版本18正式發(fā)布

新版本的PCI Spec將取得更好帶寬

新版本的PCI Spec將取得更好帶寬

評(píng)論