在本文中,我們不涉及關于EMC的設計建議。然而,在組件水平上,所使用的技術所固有的“鎖存”現象是唯一考慮的因素。

CMOS結構封裝括一個PNPN可控硅類型單元,由VDD和VSS之間的寄生晶體管產生。當寄生可控硅被擾動激活,導致了μC的電源短路,并導致內部結構的破壞時,就會出現一種延遲現象。以下的條件可能會導致“鎖存”:

ü輸入/輸出電壓的電壓高于VDD或低于VSS的電壓。

ü電源電壓VDD比VDDMax高

ü電源VDD急劇變化。

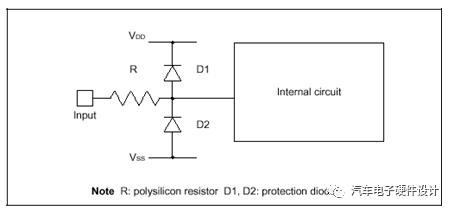

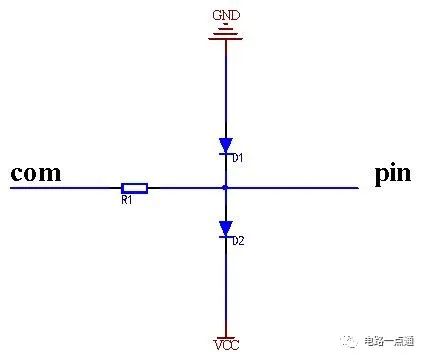

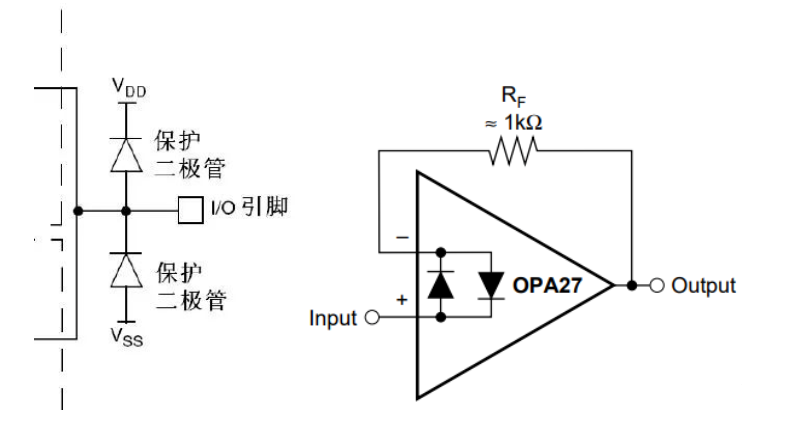

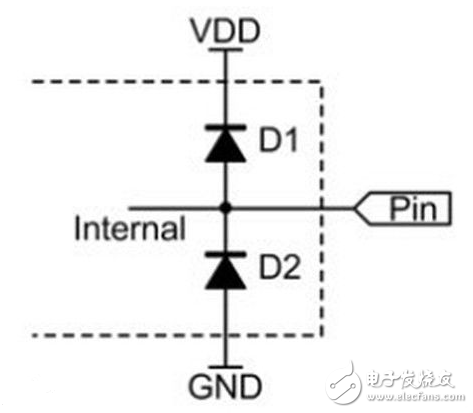

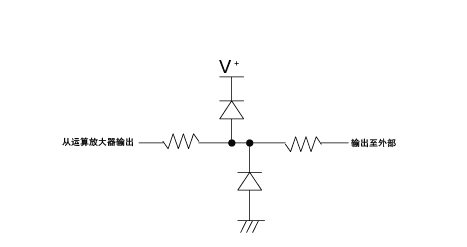

μC有對靜電保護,輸入是在內部配置保護網絡,通過對VDD和VSS并聯鉗位二極管和串聯電阻進行保護。

然而,這種內部保護電路必須在設計層面上的預防措施來完成。建議:

ü保持μC在其額定范圍內的電源電壓。

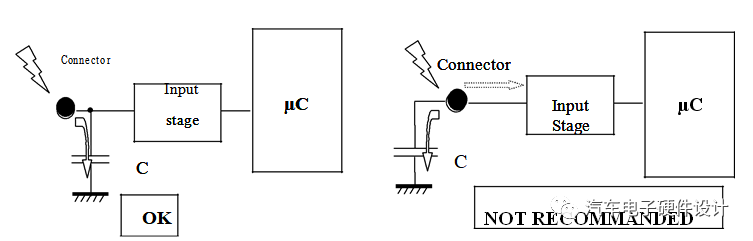

ü在連接器的引腳上直接放置一個靜電電容,以得到保護。

-

CMOS

+關注

關注

58文章

5900瀏覽量

237644 -

二極管

+關注

關注

148文章

9974瀏覽量

169679 -

emc

+關注

關注

170文章

4059瀏覽量

185467

原文標題:MCU健壯性設計之EMC / ESD的要求

文章出處:【微信號:QCDZYJ,微信公眾號:汽車電子工程知識體系】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

二極管鉗位保護電路講解

鉗位二極管保護電路圖 TVS鉗位二極管保護原理詳解

VDD和VSS并聯鉗位二極管和串聯電阻進行保護

VDD和VSS并聯鉗位二極管和串聯電阻進行保護

評論