絕大多數負載點DC-DC轉換器可以將上一個轉換器的電源就緒輸出連接至下一個轉換器的使能輸入,實現上電排序。這種方法只適合比較簡單的設計,不能滿足多數現代微處理器和DSP的要求一這類器件要求斷電順序必須與上電順序相反。許多廠商針對這類應用推出了可編程排序IC,但器件價格較為昂貴,不適合成本敏感應用。

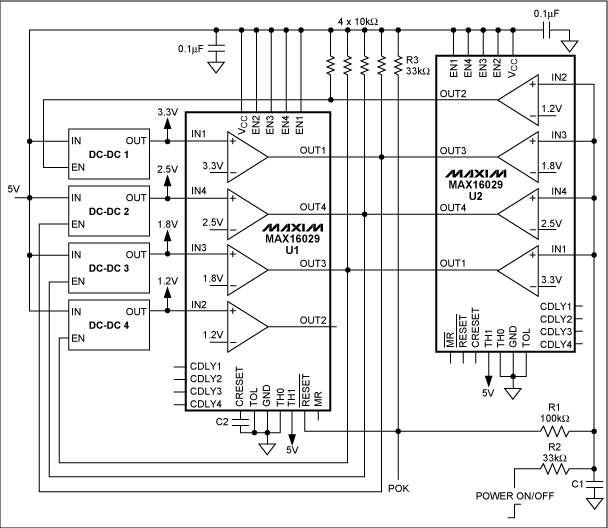

作為可編程排序IC的替代方案,圖1電路可以對四路電源進行經濟有效的排序和監測。四路DC-DC電源可分別為應用電路提供3.3V、2.5V、1.8V和1.2V電壓。四電壓監控器(U1)可監測每路電源電壓,并生成主電源就緒(POK)信號。上電期間,U1可保證前一路電源有效之前不會接通下一路電源。另一個四電壓監控器(U2)采用R1、R2、R3以及C1組成的RC電路設定上電和斷電時序。由于各監控器由內部設置的門限,因此不需要外部電阻分壓器。

圖1. 采用低成本IC,該電路首先以規定的上電次序打開四路電源,斷電時使它們以相反的順序關閉。

將電源開/關信號連接至5V輸入以啟動上電時序,此時C1通過R2充電。隨著電容電壓逐漸達到1.2V以上,上升至1.8V、2.5V和3.3V,相應的U2輸出變為高電平,從而使電源以預定的順序打開。四個電源全部接通后,經過由C2設置的延時,POK信號變為高電平。

為對電源進行監測,電源開/關信號可處于高電平狀態。POK信號通過R1和R3維持C1電壓,并保持電源導通。響應故障時,POK迅速解除有效狀態,C1 通過R1放電,進而關閉所有電源。斷電時,將電源開/關信號接地。POK解除有效狀態時,C1通過R2和R1放電,以相反順序關閉各路電源(圖2)。

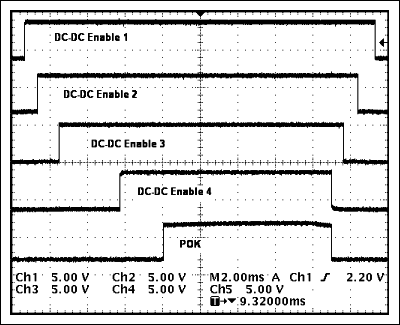

圖2. 從第1路DC-DC轉換器開始,圖1電路依序打開其它3路轉換器,并生成一個POK信號。將電路的開/關輸入接低電平,撤銷POK信號,將以相反順序關閉所有4路轉換器。

-

轉換器

+關注

關注

27文章

9027瀏覽量

151532 -

IC

+關注

關注

36文章

6111瀏覽量

179121 -

DC-DC

+關注

關注

30文章

2258瀏覽量

83763 -

電源排序器

+關注

關注

0文章

4瀏覽量

6565

原文標題:低成本電源排序器

文章出處:【微信號:analog_devices,微信公眾號:analog_devices】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

XilinxVirtex?Ultrascale?FPGA多路千兆位收發器MGT電源解決方案

用于Xilinx Ultrascale Kintex FPGA多路千兆位收發器(MGT)的電源解決方案

低成本LCD偏置電源分立式解決方案

低成本大容量Skylake平臺系統電源解決方案

詳解 FPGA 電源排序的四種方案

四種FPGA 電源排序方案

電源排序挑戰的解決方案?

關于電源排序的解決方案你了解嗎

Xilinx Virtex Ultrascale FPGA MGT電源解決方案

用于為I.MX6四核供電的低成本分立電源解決方案

低成本電源排序器

低成本電源排序器

基于MAX17014的低成本LCD TV電源解決方案

低成本電源排序器解決方案

低成本電源排序器解決方案

評論