以下文章來(lái)源于SOC磁測(cè)試之家,作者SOC磁測(cè)試之家

引言:WAT為什么要測(cè)Vth?

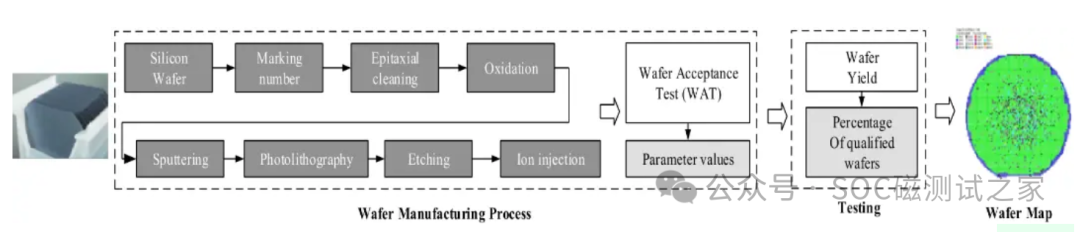

在芯片制造的納米世界里,閾值電壓(Threshold Voltage, Vth)如同人體的“血壓值”——微小偏差即可導(dǎo)致系統(tǒng)性崩潰。作為晶圓接受測(cè)試(WAT)的核心指標(biāo)之一,Vth直接決定晶體管的開(kāi)關(guān)特性、功耗水平與信號(hào)完整性。本文將深入拆解Vth的測(cè)試原理、工藝關(guān)聯(lián)及行業(yè)應(yīng)用,揭示這項(xiàng)參數(shù)如何牽動(dòng)半導(dǎo)體制造的全局。

01Vth的本質(zhì):晶體管開(kāi)關(guān)的“臨界點(diǎn)”

1. 物理定義

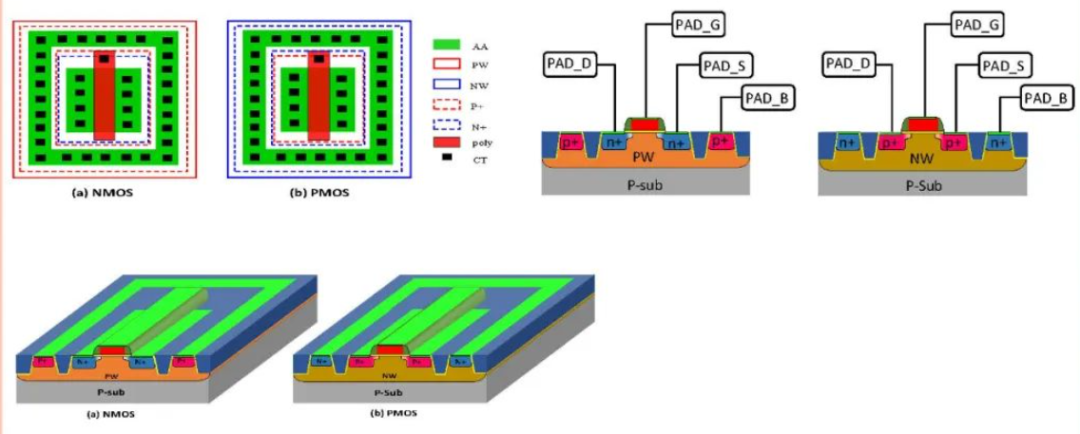

Vth指使MOSFET晶體管溝道形成導(dǎo)通所需的最低 柵極電壓 。當(dāng)柵極電壓(Vg)達(dá)到Vth時(shí),源漏極間開(kāi)始形成導(dǎo)電通道(反型層),電流(Ids)顯著上升。

2. 工程意義

性能指標(biāo) :Vth越低,晶體管開(kāi)啟速度越快,但漏電流(Ioff)增加;

功耗平衡 :Vth升高可降低靜態(tài)功耗,但會(huì)犧牲運(yùn)算速度;

工藝標(biāo)尺 :Vth波動(dòng)反映柵氧化層厚度、摻雜濃度等核心工藝參數(shù)的穩(wěn)定性。

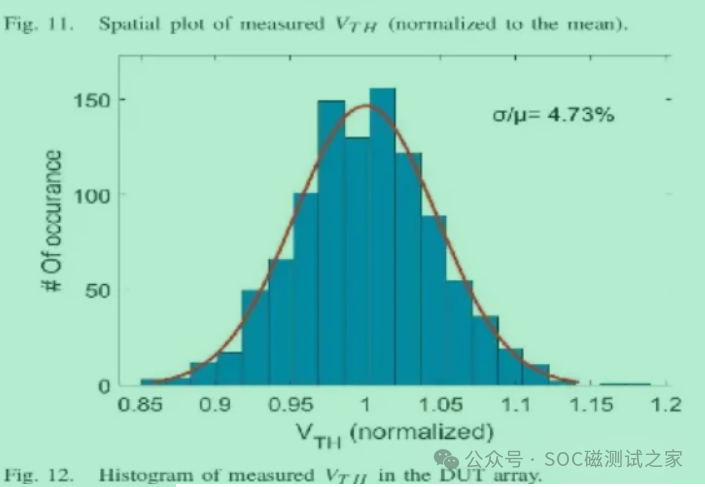

行業(yè)標(biāo)準(zhǔn) :在先進(jìn)制程中,Vth的批次內(nèi)波動(dòng)需控制在±5%以內(nèi),否則將導(dǎo)致芯片性能離散甚至功能失效。

02WAT如何測(cè)試Vth?——從結(jié)構(gòu)設(shè)計(jì)到數(shù)據(jù)采集

1. 專用測(cè)試結(jié)構(gòu)設(shè)計(jì)

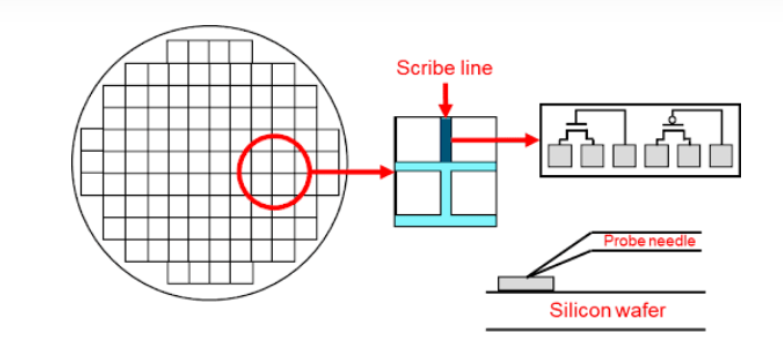

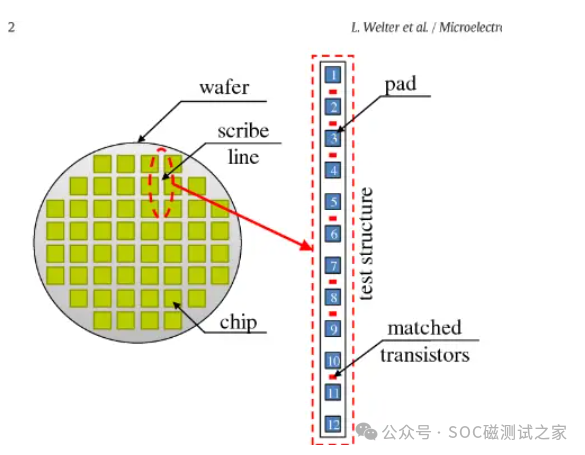

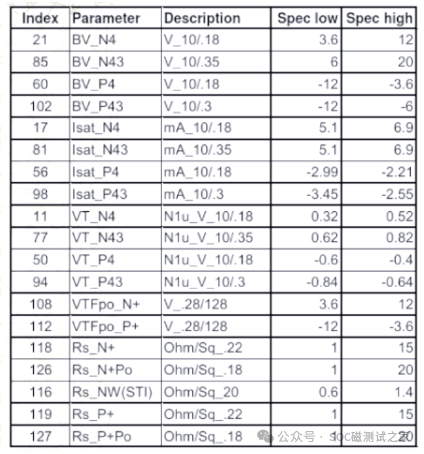

WAT通過(guò)以下特殊結(jié)構(gòu)測(cè)量Vth:

Test Key的放置點(diǎn)布置:

在進(jìn)行 WAT 測(cè)試之前,合理選擇和布置測(cè)試點(diǎn)是至關(guān)重要的一步。測(cè)試點(diǎn)的位置和數(shù)量直接關(guān)系到測(cè)試的準(zhǔn)確性和工藝評(píng)估的全面性。

Van der Pauw結(jié)構(gòu) :用于提取載流子遷移率,輔助Vth計(jì)算

環(huán)形振蕩器(Ring Oscillator) :通過(guò)振蕩頻率反推Vth

單晶體管測(cè)試單元 :最直接的Vth測(cè)量結(jié)構(gòu)

2. 測(cè)試設(shè)備與流程

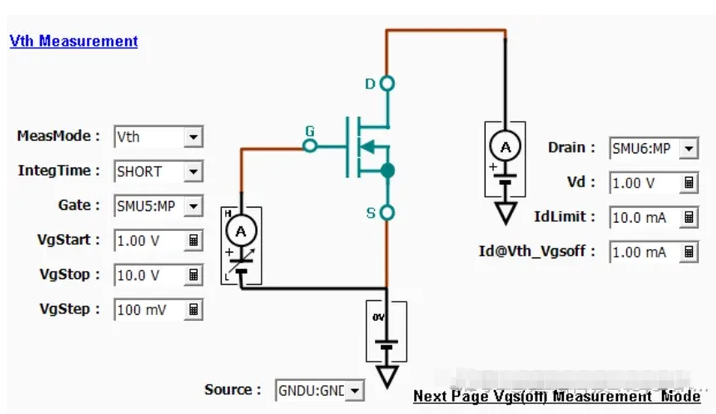

測(cè)試方法 :

線性區(qū)法 :固定Vd(漏極電壓)為0.1V,掃描Vg,取Ids=100nA·(W/L)對(duì)應(yīng)電壓為Vth(適用于長(zhǎng)溝道器件)

飽和區(qū)法 :固定Vd>Vg-Vth,通過(guò)外推Id-Vg曲線斜率確定Vth(短溝道器件主流方法)

03Vth異常背后的工藝“破案”邏輯

1. 關(guān)鍵工藝影響因素

2. 異常數(shù)據(jù)診斷流程

晶圓圖分析 :發(fā)現(xiàn)Vth呈現(xiàn)“同心圓”分布 → 指向爐管工藝溫度梯度問(wèn)題

相關(guān)性檢驗(yàn) :Vth與柵極電容(Cox)強(qiáng)相關(guān) → 鎖定氧化層厚度異常

根本原因追溯 :檢查CVD設(shè)備氣流分布 → 發(fā)現(xiàn)反應(yīng)腔邊緣沉積速率偏低

經(jīng)典案例 :

臺(tái)積電5nm危機(jī) :某批次Vth偏移8%,經(jīng)WAT數(shù)據(jù)分析發(fā)現(xiàn)EUV光刻膠殘留導(dǎo)致柵極形變,緊急升級(jí)顯影工藝后挽回?cái)?shù)萬(wàn)片晶圓損失。

中芯國(guó)際成熟制程優(yōu)化 :通過(guò)WAT監(jiān)控發(fā)現(xiàn)Vth隨晶圓位置規(guī)律性波動(dòng),最終定位至離子注入機(jī)掃描機(jī)構(gòu)校準(zhǔn)偏差,調(diào)整后良率提升12%。

04Vth測(cè)試的未來(lái)挑戰(zhàn)

1. 三維結(jié)構(gòu)測(cè)試難題

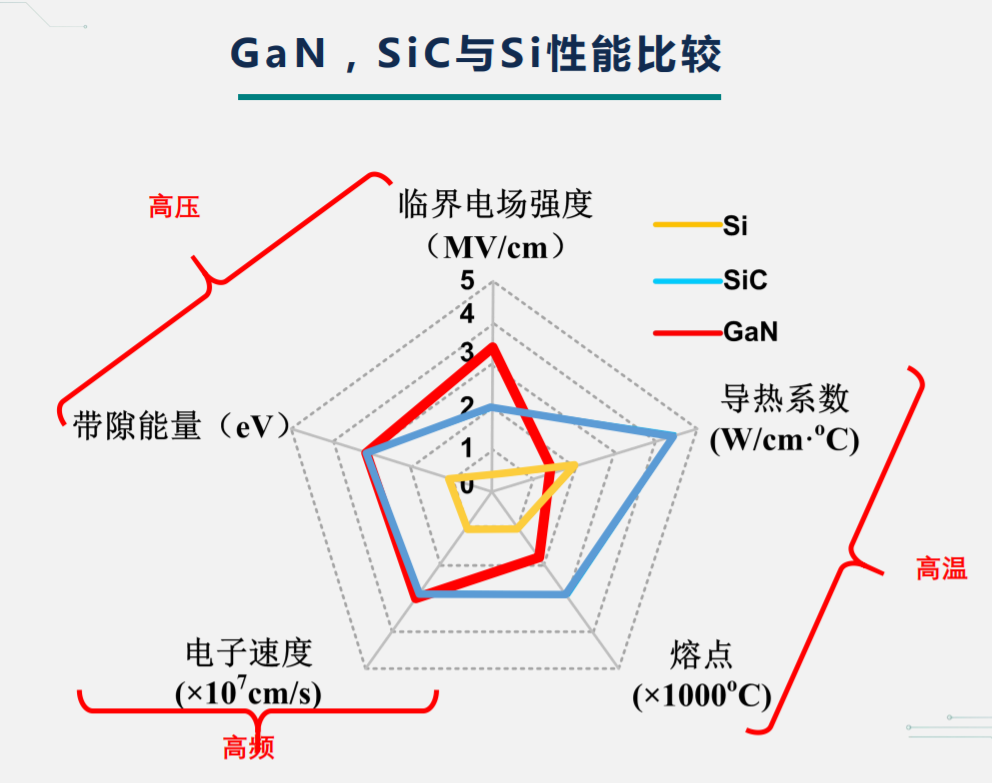

FinFET/GAA晶體管 :三維溝道使傳統(tǒng)測(cè)試方法失效,需開(kāi)發(fā)基于TCAD仿真的新型Vth提取算法

解決方案 :應(yīng)用機(jī)器學(xué)習(xí)預(yù)測(cè)Vth與鰭片寬度的非線性關(guān)系(如ASML與IMEC合作項(xiàng)目)

2. 量子效應(yīng)干擾

在3nm以下制程,量子隧穿效應(yīng)導(dǎo)致Vth隨溫度劇烈波動(dòng)

行業(yè)探索 :引入低溫WAT測(cè)試(-50℃),結(jié)合多物理場(chǎng)建模解析量子效應(yīng)

3. 測(cè)試效率瓶頸

3D堆疊芯片需測(cè)試數(shù)千個(gè)TSV通孔對(duì)應(yīng)的局部Vth,傳統(tǒng)探針臺(tái)速度無(wú)法滿足

突破方向 :應(yīng)用超導(dǎo)探針技術(shù)(日本Advantest已實(shí)現(xiàn)100GHz高頻測(cè)試)

結(jié)語(yǔ):Vth測(cè)試——半導(dǎo)體行業(yè)的“微觀戰(zhàn)場(chǎng)”

從一片晶圓的參數(shù)檢測(cè)到全球半導(dǎo)體產(chǎn)業(yè)鏈的博弈,Vth這個(gè)納米級(jí)的參數(shù),實(shí)則是技術(shù)實(shí)力的微觀投射。當(dāng)芯片制程逼近物理極限,Vth測(cè)試的精度將直接決定誰(shuí)能掌控下一代技術(shù)的制高點(diǎn)。Vth不僅為晶圓的電氣性能提供了可靠的數(shù)據(jù)支持,也為制造工藝的穩(wěn)定性和一致性提供了有效的監(jiān)控手段。通過(guò)對(duì)電學(xué)參數(shù)的精確測(cè)量和深入分析,WAT測(cè)試能夠及時(shí)識(shí)別制造過(guò)程中的問(wèn)題,進(jìn)而指導(dǎo)工藝調(diào)整,從而提升晶圓的良率和整體產(chǎn)品質(zhì)量。

-

半導(dǎo)體

+關(guān)注

關(guān)注

335文章

28838瀏覽量

236424 -

晶圓

+關(guān)注

關(guān)注

53文章

5143瀏覽量

129633 -

芯片制造

+關(guān)注

關(guān)注

10文章

684瀏覽量

29673

原文標(biāo)題:晶圓接受測(cè)試(WAT):Vth測(cè)試解析

文章出處:【微信號(hào):芯長(zhǎng)征科技,微信公眾號(hào):芯長(zhǎng)征科技】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

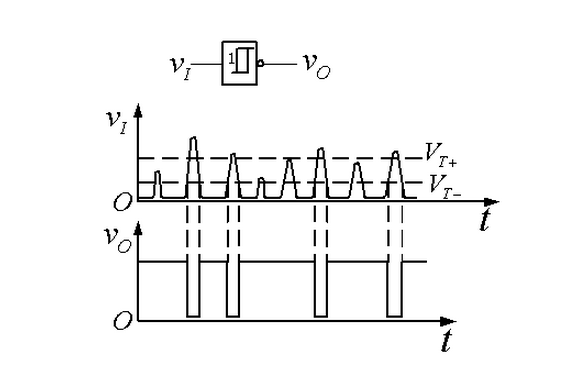

解答74HC14中正向閾值電壓和負(fù)向閾值電壓是什么/電壓為多少

提供半導(dǎo)體工藝可靠性測(cè)試-WLR晶圓可靠性測(cè)試

什么是晶圓測(cè)試?怎樣進(jìn)行晶圓測(cè)試?

閾值電壓的計(jì)算

EDA探索之控制閾值電壓

控制閾值電壓

影響第三代半導(dǎo)體SiC MOS閾值電壓不穩(wěn)定的因素有哪些?如何應(yīng)對(duì)?

晶圓封裝測(cè)試什么意思?

影響MOSFET閾值電壓的因素

什么是MOS管亞閾值電壓?MOSFET中的閾值電壓是如何產(chǎn)生的?

MOSFET閾值電壓是什么?影響MOSFET閾值電壓的因素有哪些?

MOS管的閾值電壓是什么

WAT晶圓接受測(cè)試簡(jiǎn)介

晶圓接受測(cè)試中的閾值電壓測(cè)試原理

晶圓接受測(cè)試中的閾值電壓測(cè)試原理

評(píng)論