概述

DS4510是CPU監(jiān)控電路,具有內(nèi)部集成的64字節(jié)EEPROM存儲(chǔ)器和四個(gè)可編程的非易失性(NV) I/O引腳。它配備了工業(yè)標(biāo)準(zhǔn)I2C接口,使用快速模式(400kbps)或標(biāo)準(zhǔn)模式(100kbps)進(jìn)行通信。I/O引腳可以用作通用I2C至并行I/O擴(kuò)展器,具有無(wú)限制讀寫的能力。EEPROM寄存器允許調(diào)節(jié)I/O引腳的上電值,由此在上電過(guò)程跟蹤系統(tǒng)的狀態(tài)。該CPU監(jiān)控器的定時(shí)器可以在125ms至1000ms之間調(diào)整以滿足大多數(shù)應(yīng)用的需要。

數(shù)據(jù)表:*附件:DS4510 CPU監(jiān)控電路,具有非易失存儲(chǔ)器和可編程輸入 輸出技術(shù)手冊(cè).pdf

應(yīng)用

特性

- 5V電源精確的5%、10%或15%門限值監(jiān)視

- 在V

CC返回容限范圍后,可編程的復(fù)位定時(shí)器將維持復(fù)位狀態(tài) - 具有可選擇內(nèi)部上拉電阻的四個(gè)可編程、NV、數(shù)字I/O引腳

- 64字節(jié)的用戶EEPROM

- 減少了對(duì)分立元件的需求

- I2C兼容的串行接口

- 10引腳μSOP封裝

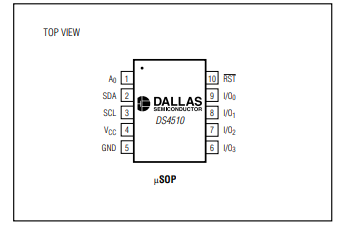

引腳配置描述

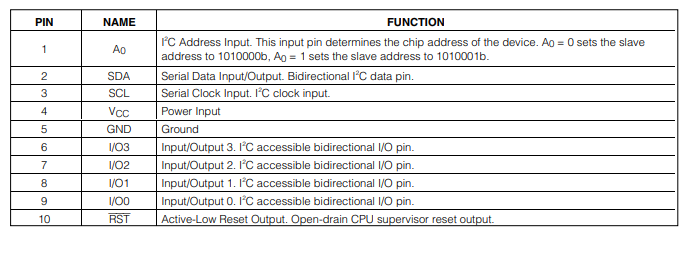

操作電路

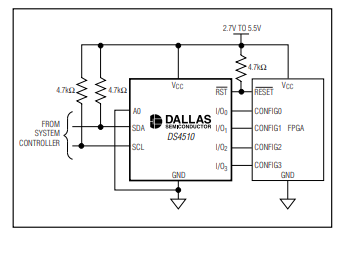

交流電氣特性

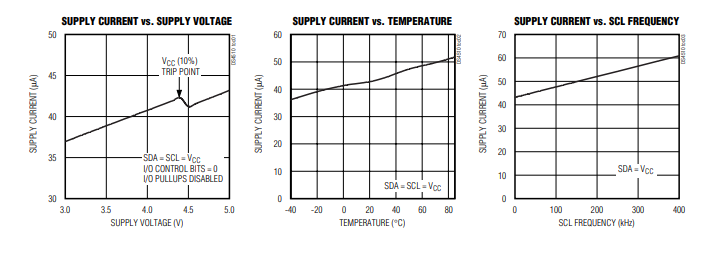

典型操作特性

詳細(xì)說(shuō)明

DS4510 包含一個(gè) CPU 監(jiān)控器、四個(gè)可編程 I/O 引腳以及一個(gè) 64 字節(jié)的 EEPROM 存儲(chǔ)器。所有功能均可通過(guò)業(yè)界標(biāo)準(zhǔn)的 I2C 兼容總線進(jìn)行配置和控制。DS4510 的非易失性寄存器采用 SRAM 映射的 EEPROM(即影子 EEPROM)實(shí)現(xiàn)。該存儲(chǔ)器可配置為作為易失性 SRAM 或非易失性 EEPROM 運(yùn)行,通過(guò)調(diào)整配置寄存器(SEEPROM)中的 SEE 位來(lái)實(shí)現(xiàn)。將這些寄存器配置為 SRAM 可消除 EEPROM 寫入時(shí)間,并允許對(duì)這些寄存器進(jìn)行無(wú)限次循環(huán)寫入。將寄存器配置為 EEPROM 可讓應(yīng)用程序更改上電時(shí)調(diào)用的電源電平值。

可編程 CPU 監(jiān)控器

通過(guò)向復(fù)位延遲寄存器(EEPROM)寫入來(lái)調(diào)整超時(shí)周期。AC 電氣特性中給出了每個(gè)設(shè)置的延遲時(shí)間。如果設(shè)置了 SEE 位,更改將寫入 SRAM。在上電時(shí),最后一個(gè)值也會(huì)寫入 EEPROM 中。I2C 總線用于通過(guò)設(shè)置配置寄存器中的 SWRT 位來(lái)激活 RST 引腳。超時(shí)周期結(jié)束后,該位會(huì)自動(dòng)復(fù)位為零。配置寄存器還包含就緒位、閾值點(diǎn)和復(fù)位狀態(tài)位。就緒位用于判斷 DS4510 的上電復(fù)位電平是否被 VCC 超過(guò)。閾值點(diǎn)用于判斷 VCC 是否高于 VCTP。如果 RST 處于有效狀態(tài),則設(shè)置復(fù)位狀態(tài)位。

注意:RST 引腳為集電極開路輸出,因此需要一個(gè)外部上拉電阻,以實(shí)現(xiàn)高邏輯電平。

可編程非易失性數(shù)字 I/O 引腳

每個(gè)可編程 I/O 引腳都包含一個(gè)輸入、一個(gè)集電極開路輸出以及一個(gè)可選擇的內(nèi)部上拉電阻。DS4510 將 I/O 引腳的更改存儲(chǔ)在 EEPROM 存儲(chǔ)器中。將 SEEPROM 用作 SRAM 對(duì)應(yīng)用程序有益,因?yàn)?I/O 擴(kuò)展通常需要快速訪問(wèn)時(shí)間和對(duì) I/O 引腳進(jìn)行頻繁修改。配置 SEE 位以在 EEPROM 模式下運(yùn)行,可允許更改 I/O 引腳的上電狀態(tài)。上電時(shí),I/O 引腳為高阻抗?fàn)顟B(tài),直到 VCC 超過(guò) 2.0V(典型值),此時(shí)從 EEPROM 中調(diào)用最后一個(gè)值。掉電時(shí),I/O 狀態(tài)由 VCC 降至 1.9V(典型值)來(lái)維持。

I/O 引腳的內(nèi)部上拉電阻由上拉使能寄存器(F0h)控制。同樣,各個(gè) I/O 控制寄存器(F4h 至 F7h)用于調(diào)整下拉電阻。

-

存儲(chǔ)器

+關(guān)注

關(guān)注

38文章

7648瀏覽量

167222 -

EEPROM

+關(guān)注

關(guān)注

9文章

1085瀏覽量

83686 -

DS4510

+關(guān)注

關(guān)注

0文章

2瀏覽量

5565

發(fā)布評(píng)論請(qǐng)先 登錄

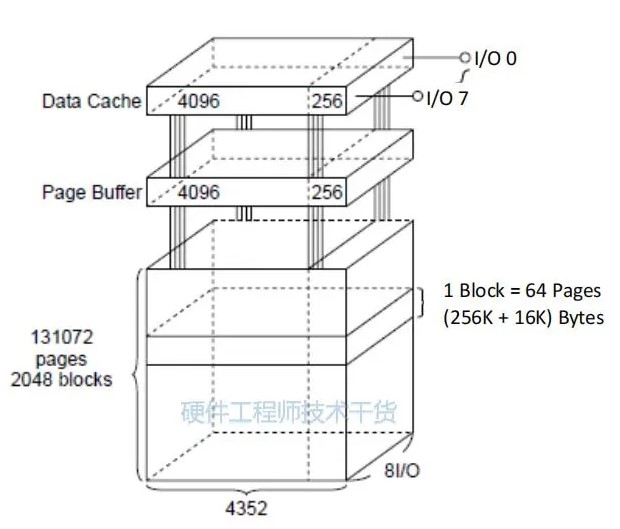

NAND Flash非易失存儲(chǔ)器簡(jiǎn)介

具有多種可編程性的易失性存儲(chǔ)器數(shù)字電位器

FPGA零基礎(chǔ)學(xué)習(xí):半導(dǎo)體存儲(chǔ)器和可編程邏輯器件簡(jiǎn)介

可編程非易失(NV)存儲(chǔ)器的質(zhì)詢-響應(yīng)安全認(rèn)證IC DS28

高度集成、10位可編程gamma和VCOM基準(zhǔn)系統(tǒng),帶有非易

Mbit非易失性靜態(tài)隨機(jī)訪問(wèn)存儲(chǔ)器nvSRAM系列

非易失性NVSRAM存儲(chǔ)器的詳細(xì)講解

LTC2936:帶電可編程只讀存儲(chǔ)器和比較器輸出的可編程禍不單行電壓監(jiān)控器數(shù)據(jù)表

帶電可編程只讀存儲(chǔ)器數(shù)據(jù)表的可編程禍不單行電壓監(jiān)控器

64Kbit非易失性鐵電存儲(chǔ)器FM25640B的功能及特征

STT-MRAM非易失存儲(chǔ)器特點(diǎn)及應(yīng)用

ram存儲(chǔ)器和rom存儲(chǔ)器的區(qū)別是什么

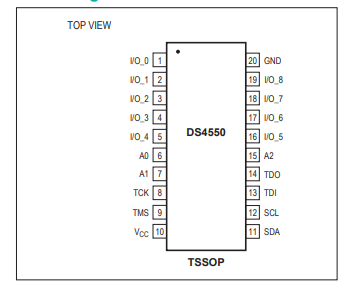

DS4550 I2C和JTAG、非易失、9位、輸入/輸出擴(kuò)展器與存儲(chǔ)器技術(shù)手冊(cè)

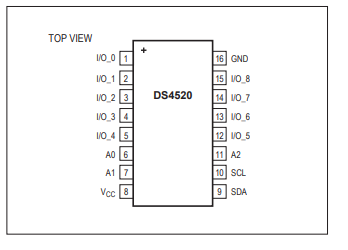

DS4520 9位、I2C、非易失、輸入/輸出擴(kuò)展器與存儲(chǔ)器技術(shù)手冊(cè)

DS4510 CPU監(jiān)控電路,具有非易失存儲(chǔ)器和可編程輸入/輸出技術(shù)手冊(cè)

DS4510 CPU監(jiān)控電路,具有非易失存儲(chǔ)器和可編程輸入/輸出技術(shù)手冊(cè)

評(píng)論