具有最小面積和最低功耗的高性能解決方案現已面向客戶推出

近日,Cadence(NASDAQ:CDNS)近日宣布推出業界速度最快的 HBM4 12.8Gbps 內存 IP 解決方案,以滿足新一代 AI 訓練和 HPC 硬件系統對 SoC 日益增長的內存帶寬需求。CadenceHBM4 解決方案符合 JEDEC 的內存規范 JESD270-4,與前一代 HBM3E IP 產品相比,內存帶寬翻了一番。Cadence HBM4 PHY 和控制器 IP 現已面向客戶開放,具備業界領先的 12.8Gbps 性能,每比特的能效提升 20%,面積利用率提升 50%,同時 I/O 數翻倍,可顯著增強整體帶寬能力。

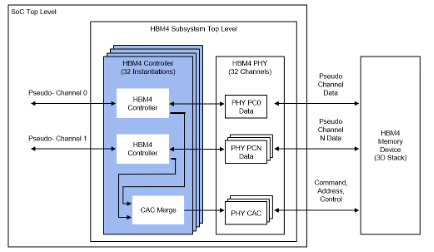

新推出的Cadence HBM4 IP將 PHY 和高性能控制器作為完整的內存子系統解決方案。HBM4 PHY 將作為臺積公司 N3 和 N2 工藝節點中的嵌入式硬宏,而 HBM4 控制器將作為 RTL 軟宏。該解決方案具有一流的 12.8Gbps 數據速率,較現有 HBM4 DRAM 設備提升 60%,為設計人員提供充足的系統裕度,既支持速率的進一步提升,也可用于打造面向未來的 SoC 產品。高性能、低延遲架構包括 RAS 和 BIST 功能,用于現場微調內存子系統性能,優化數據中心運營。標準 HBM4 IP 產品支持各種類型的中介層設計實施選項,提供實驗室軟件,助力客戶快速調試 SoC 內存子系統。

“隨著生成式和代理式 AI 應用迅猛增長,AI 工作負載增加,對內存帶寬提出了更高的要求,亟需在不額外增加功耗的前提下提高 AI 硬件系統效率。Cadence 的 HBM4 解決方案不僅實現了高達 12.8Gbps 的卓越性能,同時在 AI 工廠重點關注的面積和功率優化方面表現出色,滿足對內存帶寬持續增長的需求。”Cadence 高級副總裁兼芯片解決方案事業部總經理 Boyd Phelps表示。

Cadence的HBM4解決方案提供一套全面的可交付成果,可將 IP 快速集成到 SoC 設計,加快硅后調試工作。可交付成果包括一個參考中介層設計,該設計已在全功能測試芯片(由 HBM4 控制器、PHY、中介層和 HBM4 DRAM 設備組成)上以 12.8Gbps 的速度完成了驗證。LabStation 軟件具有豐富的功能和測試套件,有助縮短 SoC 硅后實驗室調試時間,從而加快產品上市。

Cadence 的 HBM4 PHY 和控制器已使用 Cadence 面向HBM4 的 Verification IP(VIP)進行驗證,能夠提供快速的 IP 和 SoC 驗證收斂。面向 HBM4 的 Cadence VIP 包括一個完整的解決方案,涵蓋了從 IP 到系統級驗證在內的全部流程,提供 DFI VIP、HBM4 存儲器模型和 System Performance Analyzer 系統性能分析工具。

關于 Cadence

Cadence 是 AI 和數字孿生領域的市場領導者,率先使用計算軟件加速從硅片到系統的工程設計創新。我們的設計解決方案基于 Cadence 的 Intelligent System Design戰略,可幫助全球領先的半導體和系統公司構建下一代產品(從芯片到全機電系統),服務超大規模計算、移動通信、汽車、航空航天、工業、生命科學和機器人等領域。2024 年,Cadence 榮登《華爾街日報》評選的“全球最佳管理成效公司 100 強”榜單。

-

控制器

+關注

關注

114文章

17089瀏覽量

184088 -

Cadence

+關注

關注

67文章

973瀏覽量

144305 -

內存

+關注

關注

8文章

3119瀏覽量

75227 -

HBM4

+關注

關注

0文章

54瀏覽量

249

原文標題:Cadence 推出業界領先的 HBM4 12.8Gbps IP 內存系統解決方案, 賦能新一代 AI 和 HPC 系統

文章出處:【微信號:gh_fca7f1c2678a,微信公眾號:Cadence楷登】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

HBM3E量產后,第六代HBM4要來了!

美光12層堆疊36GB HBM4內存已向主要客戶出貨

Cadence推出DDR5 12.8Gbps MRDIMM Gen2內存IP系統解決方案

三星調整1cnm DRAM設計,力保HBM4量產

美光發布HBM4與HBM4E項目新進展

特斯拉欲將HBM4用于自動駕駛,內存大廠加速HBM4進程

特斯拉也在搶購HBM 4

特斯拉或向SK海力士、三星采購HBM4芯片

Rambus推出業界首款HBM4控制器IP

Rambus宣布推出業界首款HBM4控制器IP,加速下一代AI工作負載

英偉達向SK海力士提出提前供應HBM4芯片要求

Cadence展示完整的PCIe 7.0 IP解決方案

Cadence推出HBM4 12.8Gbps IP內存系統解決方案

Cadence推出HBM4 12.8Gbps IP內存系統解決方案

評論