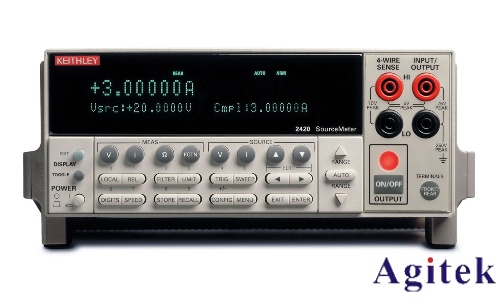

吉時(shí)利源表作為多功能電學(xué)測(cè)試儀器,其高精度特性在電阻測(cè)量中尤為突出。本文將結(jié)合實(shí)操要點(diǎn),闡述如何通過優(yōu)化接線、參數(shù)設(shè)置及誤差消除技術(shù),實(shí)現(xiàn)亞歐姆級(jí)至兆歐姆級(jí)的精準(zhǔn)電阻測(cè)量。

一、接線方法的選擇:四線制消除引線干擾

高精度電阻測(cè)量需最大限度降低引線電阻與接觸電阻的影響。采用四線制(開爾文)接線法,將電流輸出線與電壓測(cè)量線分離:電流線用于驅(qū)動(dòng)被測(cè)電阻(DUT),電壓線僅負(fù)責(zé)測(cè)量DUT兩端電勢(shì)差。此舉可避免引線壓降引入誤差,尤其適用于低阻測(cè)量(如<1Ω)。此外,使用三同軸電纜進(jìn)一步提升屏蔽效果,降低噪聲干擾。

二、參數(shù)設(shè)置與量程優(yōu)化

1. 源回讀功能(Source Readback):?jiǎn)⒂迷摴δ芸蓪?shí)時(shí)監(jiān)測(cè)輸出電流/電壓,確保源表輸出穩(wěn)定。例如,測(cè)量小電阻時(shí),若電流源設(shè)定值與實(shí)際輸出存在偏差,回讀功能可及時(shí)修正,提升測(cè)量精度。

2. 量程選擇與限流保護(hù):根據(jù)待測(cè)電阻范圍合理選擇量程。例如,測(cè)量10kΩ電阻時(shí),優(yōu)先選用低電流檔位(如1mA),避免自熱效應(yīng);同時(shí)設(shè)置限壓保護(hù),防止過壓損壞DUT。

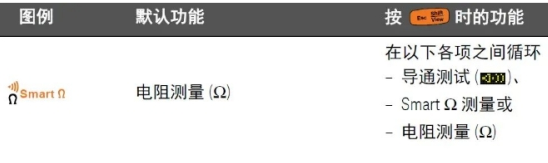

3. 自動(dòng)歐姆測(cè)量模式:部分型號(hào)支持自動(dòng)歐姆測(cè)量,通過電流-電壓雙極性掃描計(jì)算電阻平均值,有效抑制熱電動(dòng)勢(shì)(EMF)干擾。

三、誤差消除技術(shù):補(bǔ)償與修正

1. 熱電動(dòng)勢(shì)補(bǔ)償(Offset Compensation):針對(duì)微電阻測(cè)量(如mΩ級(jí)),啟用該功能可抵消線纜與探針間的溫差電勢(shì)。建議預(yù)熱儀器30分鐘,確保溫度穩(wěn)定。

2. 溫度修正系數(shù)應(yīng)用:對(duì)于溫度系數(shù)較高的材料(如金屬膜電阻),需結(jié)合測(cè)試環(huán)境設(shè)置溫度補(bǔ)償參數(shù),通過軟件修正電阻值。

3. 多次平均與數(shù)據(jù)濾波:通過多次測(cè)量取平均值,配合軟件的數(shù)字濾波功能,進(jìn)一步平滑隨機(jī)噪聲。

四、注意事項(xiàng)與實(shí)戰(zhàn)技巧

1. 測(cè)試前準(zhǔn)備:接線時(shí)務(wù)必?cái)嚯姴僮鳎苊?a target="_blank">高壓脈沖損傷DUT或儀器。使用前置放大器時(shí),需先關(guān)閉源表主機(jī)再連接設(shè)備。

2. 寄生電容處理:對(duì)于高阻測(cè)量(如GΩ級(jí)),使用屏蔽箱隔離待測(cè)器件,并采用“電流換向法”消除寄生電容充放電影響。

3. 模型選擇:針對(duì)薄膜材料或復(fù)雜器件,結(jié)合四探針法測(cè)試表面/體電阻率,選用支持微電流測(cè)量的型號(hào)(如2450/2460系列)。

通過以上技術(shù)組合,吉時(shí)利源表可在半導(dǎo)體器件表征、材料分析及精密電路調(diào)試中,實(shí)現(xiàn)ppm級(jí)精度的電阻測(cè)量。合理配置硬件與軟件參數(shù),輔以嚴(yán)謹(jǐn)?shù)臏y(cè)試流程,可最大化挖掘儀器性能,滿足科研與工業(yè)測(cè)試的嚴(yán)苛需求。

審核編輯 黃宇

-

電阻測(cè)量

+關(guān)注

關(guān)注

2文章

40瀏覽量

12683 -

源表

+關(guān)注

關(guān)注

0文章

119瀏覽量

4929

發(fā)布評(píng)論請(qǐng)先 登錄

吉時(shí)利數(shù)字源表2450如何實(shí)現(xiàn)MOSFET柵極漏電流的超低噪聲測(cè)量

吉時(shí)利2450源表如何實(shí)現(xiàn)高精度IV特性測(cè)試

貼片熱敏電阻測(cè)量指南

用吉時(shí)利數(shù)字源表2450測(cè)量電導(dǎo)率的方法

國(guó)產(chǎn)首款量產(chǎn)型七位半萬用表!青島漢泰開啟國(guó)產(chǎn)高精度測(cè)量新篇章。

吉時(shí)利2400數(shù)字源表在材料科學(xué)中電導(dǎo)率測(cè)量中的應(yīng)用

吉時(shí)利數(shù)字源表2400在半導(dǎo)體器件測(cè)試中的深度應(yīng)用與關(guān)鍵技術(shù)解析

國(guó)巨電阻的厚膜技術(shù):如何實(shí)現(xiàn)高精度與低成本?

串聯(lián)高精度電阻實(shí)現(xiàn)直流電流采樣遇到的疑問求解

吉時(shí)利源表軟件在憶阻器測(cè)試中的應(yīng)用

用吉時(shí)利源表實(shí)現(xiàn)高精度電阻測(cè)量的技術(shù)指南

用吉時(shí)利源表實(shí)現(xiàn)高精度電阻測(cè)量的技術(shù)指南

評(píng)論