你知道嗎?把設計好的芯片圖紙變成實物,這個關鍵步驟叫“流片”。但最近行業曝出一個驚人數據:2025年,芯片第一次流片的成功率只有14%!相比兩年前的24%,幾乎“腰斬”。這背后,作為深耕分立器件封測的老牌企業——合科泰,為您講解整個半導體行業面臨的巨大挑戰。

流片:從圖紙到硅片的驚險一躍

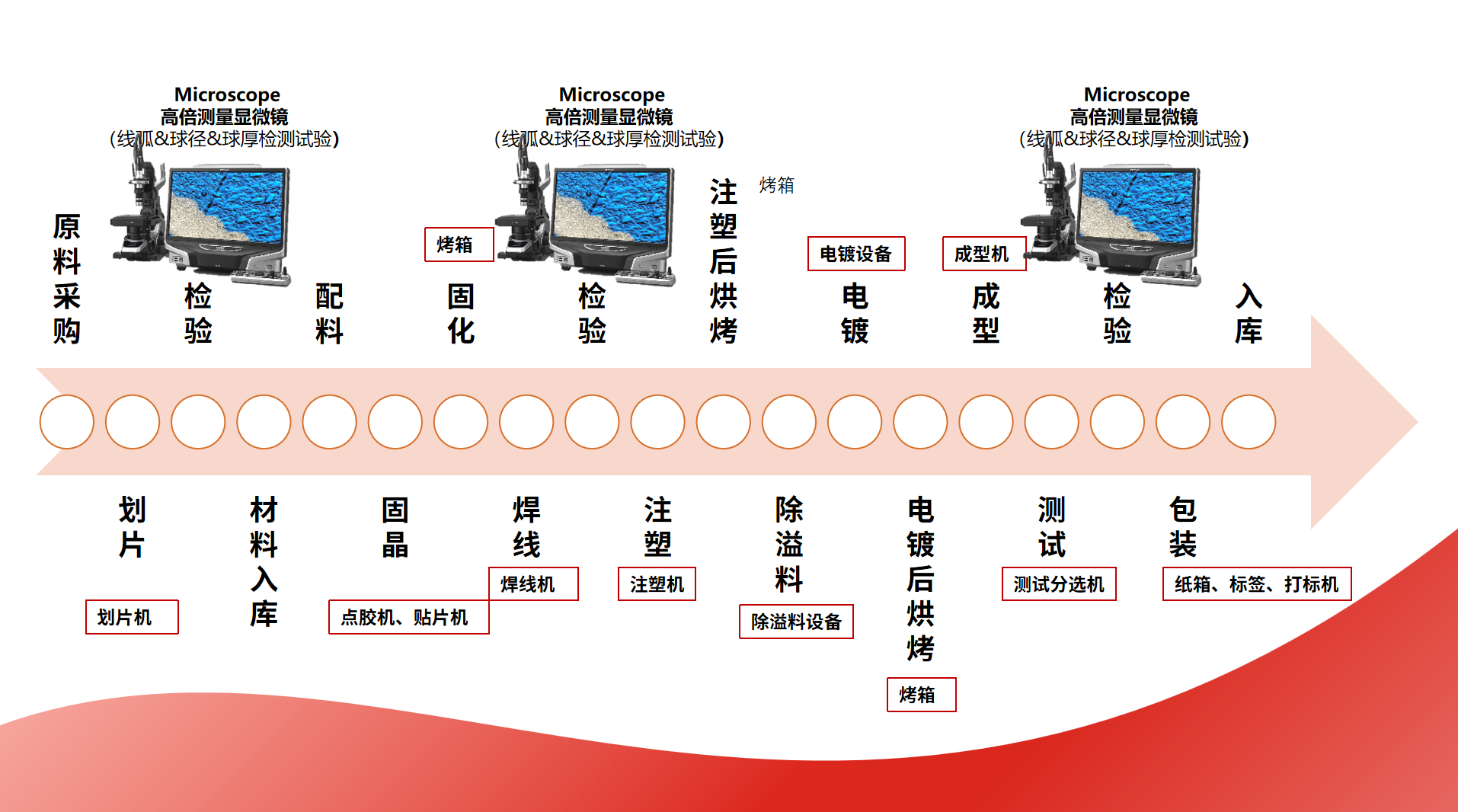

流片流程大致是這樣:工程師把設計好的芯片“藍圖”(版圖文件)交給芯片代工廠(比如臺積電、三星)。首先,工廠要制作極其精密的“模具”——光刻掩膜版。在3nm這樣的尖端工藝上,一套掩膜版成本可能高達幾百萬美元!接著是復雜的制造過程,核心是光刻(尤其是先進的EUV光刻技術)、蝕刻、離子注入和層層金屬布線。芯片越做越小,布線帶來的電阻、電容問題就越突出,難度激增。

制造完成的晶圓片,還要經過嚴格的“體檢”(晶圓測試/CP測試),用探針一個個芯片測功能。如果發現速度慢了、功耗高了或者根本不通電,那這批流片就算失敗,錢打水漂,得重頭再來。即使過了這關,后續切割、封裝環節也可能出問題。

成功率暴跌的三大“元兇”

為什么第一次就成功的芯片越來越少?主要有三大原因:

1.設計太復雜,驗證跟不上:現在的芯片都是“混血兒”。比如,AI芯片可能用5nm做計算核心,14nm做存儲,28nm做接口。不同工藝模塊要協同工作,設計難度指數級上升。同時,AI、自動駕駛等定制化芯片需求猛增,驗證場景可能超過10億種,傳統設計工具根本忙不過來。

2.搶時間,基礎沒打牢:市場競爭太激烈,很多公司把開發周期從18個月壓縮到1年以內。結果是設計驗證時間被大幅擠壓,很多潛在問題沒查出來就匆忙流片。有AI芯片公司就曾因“時序收斂”這種基礎問題流片失敗,損失數千萬美元。此外,先進工藝(如2nm/3nm)本身良率就不高(臺積電2nm初期良率約60%,三星3nm更低),即使設計完美,制造環節也可能出問題。

3.技術躍進,老經驗不夠用:從28nm到14nm時,首次成功率就從30%降到26%。如今邁向3nm/2nm,復雜度更高,風險更大。同時,芯片設計要融合模擬、數字、射頻等多種技術,缺乏協同經驗就容易在信號傳輸上栽跟頭。

出路何在?提升成功率的“三板斧”

面對挑戰,行業也在積極尋找出路:

AI助力“火眼金睛”:用AI設計驗證工具是突破口。比如西門子的QuestaOne工具,利用AI預測哪些測試最關鍵,能把幾千次測試壓縮到幾百次,效率提升好幾倍,還能自動定位問題根源。結合數學驗證和仿真,能把驗證時間從幾周縮短到幾天。

模擬考”提前排雷:流片前先用FPGA(可編程芯片)快速搭建原型,驗證系統級功能。有公司就靠這個方法發現了內存控制器漏洞,避免了流片失敗。專用仿真加速器速度更是比普通電腦快百倍。

"抱團取暖”深度合作:芯片設計公司和代工廠緊密合作至關重要。像蘋果和臺積電合作開發3nm芯片時,就共同優化設計來提高良率。復用經過嚴格驗證的第三方成熟模塊(IP核),也能大大降低風險、縮短周期。

結語

流片成功率低至14%催生新趨勢:中小公司聚焦核心設計,將流片委托專業方。先進封裝成破局關鍵,Chiplet技術通過模塊化封裝降低工藝依賴,合科泰Flipchip倒裝工藝研發線已探索多芯片封裝良率提升方案。國產替代加速背景下,合科泰以X-Ray檢測、全溫域測試等技術攻克良率難題。破局需AI驗證、產業鏈協同與創新,合科泰DFM協同設計及現貨供應鏈,為企業縮短周期、降低風險,成應對“成功率危機”可靠伙伴。

審核編輯 黃宇

-

芯片

+關注

關注

460文章

52520瀏覽量

440952 -

流片

+關注

關注

0文章

30瀏覽量

9901

發布評論請先 登錄

MOSFET工藝參數揭秘:合科泰的技術突圍之道

合科泰功率MOSFET在智能照明行業的選型

合科泰三極管TIP42A的應用領域

芯片流片首次成功率僅14%?合科泰解析三大破局技術

芯片流片首次成功率僅14%?合科泰解析三大破局技術

評論