近日,2025 “概倫電子技術日” 北京站活動成功舉辦。本次活動以 “AI 賦能國產 EDA 新進程”為主題,聚焦AI與EDA技術融合,吸引了集成電路行業專家、高校學者及企業代表齊聚一堂,共同探討集成電路產業在 AI 時代的變革與發展,為國產EDA技術的創新與應用搭建了高端交流平臺。

開篇致辭:錨定AI時代產業發展新機遇

概倫電子副總裁韋承在歡迎辭中表示,AI技術與EDA的深度融合是國產EDA實現換道超車的關鍵機遇,需加速技術創新與生態協同。概倫電子將以技術創新為核心,推動AI在EDA領域的落地應用,助力中國集成電路產業高質量發展。

主題演講:工藝協同,優化設計

概倫電子總監逯文忠在《工藝協同,優化設計,提升集成電路行業競爭力》主題演講中提到,概倫電子一直踐行DTCO理念,通過EDA創新,應對大規模設計的挑戰,打造了業界最領先、最完整的建模解決方案,快速、精準的標準單元庫特征化解決方案,持續演進一體化電路仿真驗證解決方案。同時,通過業界領先的Design Enablement解決方案不僅支撐晶圓廠的工藝平臺研發,更幫助尋求差異化競爭的設計企業建設COT能力,挖掘工藝潛力,優化芯片的YPPAC。

技術前沿:創新路徑,為芯片企業打造差異化競爭力

概倫電子副總裁馬玉濤在《AI時代模擬和定制電路設計挑戰和機遇》的演講中,從設計場景、工藝協同、效能提升三維度,解析AI技術對EDA工作流的重構路徑。當前模擬與定制電路設計仍以晶體管級手動設計為基礎,其復雜度隨工藝演進持續攀升:先進制程下單個FinFET器件需提取數百個寄生參數,百萬級晶體管規模的模擬電路對仿真精度提出更高要求;面向SoC的全芯片設計則需兼顧寄生參數提取(PEX)的效率與容量。EDA工具在精度與速度上,面臨雙重挑戰。概倫電子在AI技術上探索已久,覆蓋芯片制造到設計優化全流程,貫穿成熟工藝定制化與先進工藝良率提升,已部署和規劃多維度AI/ML融合解決方案。

概倫電子總監趙寶磊在《SDEP智能化建模平臺,助力縮短工程服務周期》技術演講中,重點介紹了公司的Spec驅動模型自動化提取平臺SDEP。該平臺憑借對業界最新模型的全面支持,在性能和易用性方面實現雙重突破,還特別分享了SDEP在頭部客戶中的成功應用案例:通過AI驅動的智能參數提取算法,成功將器件建模周期縮短50%;在先進工藝PDK開發中,模型精度也獲得顯著提升。這一創新成果為半導體行業提供了高效的智能化建模解決方案。

清華大學副教授葉佐昌在《AI賦能的模擬電路設計》主題演講中,系統性地闡述了模擬電路設計的創新方法論。他首先開創性地提出了"代碼化模擬電路設計"的全新理念,隨后重點展示了其團隊研發的TED工具平臺及其核心技術突破。最后,葉教授前瞻性地分享了多個AI技術賦能模擬電路自動化設計的創新研究方向,為行業提供了具有實踐價值的智能化解決方案。

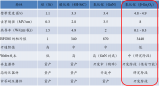

概倫電子高級總監鄧雨春在《持續創新,高效快速仿真應對高性能芯片應用挑戰》技術演講中,詳細介紹了概倫電子NanoSpice家族仿真解決方案。該方案以2倍以上的仿真速度優勢,為高性能芯片設計提供一站式支持:其中True SPICE工具NanoSpice X實現了從器件模型、模塊級電路到高精度模擬全芯片仿真的全流程覆蓋;FastSPICE工具NanoSpice Pro X則專注于SoC、存儲器電路和CLK tree等復雜場景的高效仿真。他還特別強調,通過NanoSpice與數字仿真器VeriSim的混仿技術,配合完整的模型支持體系,該方案已構建起覆蓋各類仿真和驗證方法學的完整技術生態。目前,這項經過國際國內頭部芯片公司十余年驗證的成熟技術,已全面支持SPICE、FastSPICE和CoSim等多種仿真模式,為芯片設計行業提供了可靠的高性能仿真解決方案。

概倫電子應用工程師何秋云詳解《從PDK到芯片設計:“交鑰匙”服務加速工藝平臺建設》,她表示,隨著芯片工藝節點不斷降低,PDK的參數也會成倍增長,對于仿真、callback、layout code的編寫也變得非常復雜,特別是FinFET工藝,對開發工程師的經驗和數量都有非常高的要求。概倫電子基于在該領域多年的深耕經驗,為客戶提供高效、自動化的PDK開發解決方案,能夠一站式為PDK正向開發、代碼轉換、二次開發提供自動化Source code生成,且操作簡便。同時,提供全面、自動化的PDK驗證解決方案,確保高質量交付。從助力企業工藝平臺搭建的實際案例中得出,概倫電子的工具可提速三倍以上,使得為Fab和Fabless客戶提供快速定制化通道成為可能。

概倫電子總監章勝在《應用驅動,先進工藝K庫挑戰與實踐》演講中,重點介紹了概倫電子K庫工具NanoCell的創新突破。該工具不僅具備ARC自動化提取功能,更實現了Moment LVF與MC一致性超過99%的行業領先水平,并通過萬核級分布式并行算力大幅提升運算效率。他強調,概倫電子將持續深耕標準單元庫建庫EDA工具開發領域,通過設計流程優化與方法學集成創新,致力于解決先進工藝節點下行業面臨的K庫痛點,為半導體產業提供更具競爭力的解決方案。

北京超弦存儲器研究院研發總監余泳在《超越摩爾定理,DTCO在DRAM及新型存儲器中的應用》技術演講中,深入剖析了設計技術協同優化(DTCO)的創新價值。他指出,DTCO通過實質性架構創新成功突破了摩爾定律的局限,在4F2 DRAM和3D DRAM等先進存儲器開發中展現出關鍵作用。他還特別強調,SPICE模型作為DTCO流程的核心支撐,在當前新材料和存儲單元缺乏標準緊湊模型的情況下,正發揮著不可替代的關鍵技術價值,為存儲器創新提供重要支撐。

概倫電子總監任繼杰在《芯片設計中可靠性分析EDA技術挑戰和解決方案》演講中強調,晶體管級仿真器尤其是快速仿真器是芯片可靠性驗證的核心技術支撐,并系統介紹了概倫電子在high-sigma良率分析、EMIR分析、信號完整性驗證、電路檢查及MOSFET老化分析等關鍵領域的技術突破,展示了公司為行業提供的全方位、領先的可靠性驗證解決方案體系,以助力芯片用戶企業應對日益復雜的可靠性驗證挑戰。

概倫電子高級經理秦朝政在《DTCO解決方案賦能芯片企業COT平臺》演講中,詳細解讀了設計與制造協同優化(DTCO)技術如何打破傳統芯片設計與制造的壁壘,并助力IDM公司和設計公司加速COT平臺建設,挖掘工藝潛力。通過全流程協同實現芯片性能提升與成本優化的雙重目標。

“概倫電子技術日”北京站活動構建了產學研用深度交流的平臺,從技術創新到工具開發,全方位展現了AI賦能國產EDA的實踐成果。正如活動結語所言,國產EDA的發展需要產業鏈上下游協同發力,概倫電子將持續以技術創新為引領,推動中國集成電路產業在AI時代實現跨越式發展。

-

集成電路

+關注

關注

5420文章

11985瀏覽量

367523 -

eda

+關注

關注

71文章

2904瀏覽量

176745 -

AI

+關注

關注

88文章

34544瀏覽量

276067 -

概倫電子

+關注

關注

1文章

112瀏覽量

8993

原文標題:概倫電子技術日 |「北京站」圓滿收官,共話AI賦能國產EDA新進程

文章出處:【微信號:khai-long_tech,微信公眾號:概倫電子Primarius】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

2025概倫電子技術日廣州站成功舉行

概倫電子攜應用驅動的一站式芯片可靠性解決方案亮相ISEDA 2025,賦能設計公司COT平臺

合作共贏 星縱物聯生態路演北京站圓滿收官!

碩博電子Bauma 2025圓滿收官

硬件永不止步 · 互連進無止境 | Samtec于Keysight開放日北京站的總結

概倫電子邀您相約SEMICON CHINA 2025

概倫電子2025年半導體器件特性測試系統代理商培訓會議圓滿結束

電馭未來,智啟北京 — 電力電子技術產業大會北京站盛大啟幕

2025概倫電子技術日北京站圓滿收官

2025概倫電子技術日北京站圓滿收官

評論