01簡介

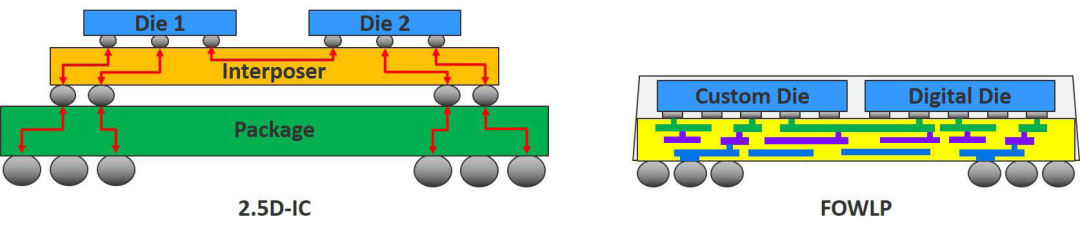

高密度先進封裝 (HDAP) 設(shè)計如今已成為真實的產(chǎn)品。過去十年里,HDAP 技術(shù)的所有變化形式都承諾通過集成使用不同技術(shù)節(jié)點構(gòu)建的多個集成電路 (IC) 芯片(異構(gòu)集成),來獲得改進的外形參數(shù)和功能。下圖顯示了兩種流行的 HDAP 技術(shù):2.5D(中介層)和扇出型晶圓級封裝 (FOWLP) 設(shè)計。

圖:基于中介層的 2.5D IC 和 FOWLP 設(shè)計是最常用的 HDAP 技術(shù)

同任何電子產(chǎn)品一樣,HDAP 設(shè)計也需要廣泛的驗證,確保它們能夠按預(yù)期運行,并且能夠可靠地制造出足夠的數(shù)量以滿足市場需求。但事實證明,自動化 HDAP 驗證對電子設(shè)計自動化 (EDA) 行業(yè)來說頗具挑戰(zhàn),因為它需要結(jié)合 IC 和封裝驗證的元素。在確定問題、建議或制定解決方案方面,人們投入了大量的時間和研究。類似于集成電路工藝設(shè)計套件 (PDK) 的合格裝配設(shè)計套件 (ADK) 的一般概念,至少已在有限的程度上變?yōu)楝F(xiàn)實。HDAP 的裝配級版圖和電路圖比較 (LVS) 驗證,現(xiàn)在至少有了一種 EDA 解決方案。HDAP 的布線后仿真(模擬)和布線后 STA(數(shù)字)流程的價值,更是眾所周知。人們認(rèn)識到,需要一種方法來生成 HDAP 系統(tǒng)級連接,同時兼顧芯片、封裝和芯片/封裝接口寄生效應(yīng)。

在推動 HDAP 成為一個可行的市場選擇方面,雖然上述所有工作都很珍貴,但現(xiàn)在似乎有必要評估這一過程的成熟度和范圍,并展望其未來的發(fā)展。為此,我們將聚焦其中一個目標(biāo):封裝 LVS 驗證。

02HDAP 物理驗證成熟度

隨著 HDAP 技術(shù)的日益發(fā)展和成熟,設(shè)計人員需要 EDA 工具公司、晶圓代工廠和封測代工廠 (OSAT) 提供合格、可靠的 EDA 設(shè)計和驗證流程。完成設(shè)計后,第一步自然是 HDAP 的物理驗證。HDAP 設(shè)計包含通過封裝連接的多個異構(gòu)芯片。雖然 HDAP 中每個芯片自身的功能都已經(jīng)過驗證,但 HDAP 設(shè)計人員如何確保整個 HDAP 在制造后仍能按預(yù)期運行呢?

這個問題代表了一種不連續(xù)性,也是傳統(tǒng)封裝設(shè)計中不存在的全新挑戰(zhàn)。在過去,單憑肉眼檢查就足以確認(rèn)芯片是否正確連接到封裝,繼而連接到最終產(chǎn)品,如印刷電路板 (PCB)。對 HDAP 設(shè)計而言,情況并非如此。

盡管 EDA 公司、晶圓代工廠/OSAT 和 HDAP 設(shè)計公司已合作多年,共同構(gòu)建 HDAP 物理驗證流程,但這個流程還遠遠談不上 “成熟”。各方需要學(xué)習(xí)的地方還很多。

03驗證數(shù)據(jù)完整性

下面我們來考慮一下面向 HDAP 設(shè)計的版圖和電路圖比較 (LVS) 驗證。除非版圖設(shè)計中內(nèi)置的幾何形狀實現(xiàn)了原始原理圖/設(shè)計意圖所需的連接,否則片上系統(tǒng) (SoC) 就無法獲批投入制造。LVS 驗證是 SoC 領(lǐng)域一個成熟、完善的自動化流程。用于 SoC 的 EDA LVS 工具需要一組一致的基本輸入:

■ 版圖數(shù)據(jù)庫(格式可以是 GDSII、OASIS 或 LEF/DEF)

■源網(wǎng)表(格式可以是 SPICE 或 Verilog)

■ LVS 規(guī)則集(基于 EDA 公司專有語法的格式)

設(shè)計公司、晶圓代工廠和 EDA 供應(yīng)商都理解并同意,如果沒有某種形式的上述三種輸入,SoC LVS 驗證便無從談起。LVS 規(guī)則集通常由晶圓代工廠創(chuàng)建并提供,獨立于任何單一 SoC 設(shè)計,版圖數(shù)據(jù)庫和源網(wǎng)表則由設(shè)計公司創(chuàng)建。

回到 HDAP LVS 驗證,我們馬上就能發(fā)現(xiàn)重要的差異。最明顯且最關(guān)鍵的一點是,設(shè)計公司、晶圓代工廠/OSAT 和 EDA 公司在 HDAP LVS 流程所需的輸入集上沒有達成一致。存在這種脫節(jié)的原因有三個:所有權(quán)、數(shù)據(jù)可用性和設(shè)計依賴性。

所有權(quán)

由于 HDAP 仍是一種新興技術(shù),HDAP 驗證的責(zé)任在不同公司往往由不同的團隊承擔(dān)。例如,一些設(shè)計公司傾向于將 2.5D 設(shè)計和驗證視為 “SoC 為主,封裝為輔” 的活動。這類設(shè)計的設(shè)計和驗證責(zé)任通常落到了 SoC 和/或計算機輔助設(shè)計 (CAD) 團隊的身上,他們在 SoC 驗證要求和格式方面有著豐富的經(jīng)驗。而對于 FOWLP 封裝,設(shè)計和驗證被視為 “SoC 為輔,封裝為主” 的活動,因此該責(zé)任通常由不太熟悉 SoC 驗證要求和格式的封裝團隊承擔(dān)。保持這種多樣性的底線是,晶圓代工廠/OSAT 和 EDA 公司在支持采用不同方法且具有不同要求的 HDAP 設(shè)計公司時,必須做好靈活應(yīng)對的準(zhǔn)備。

數(shù)據(jù)可用性

為了實現(xiàn)對整個 HDAP 的 LVS 驗證,所有組件的所有數(shù)據(jù)都必須可用。例如,F(xiàn)OWLP 設(shè)計人員需要 die1 版圖設(shè)計數(shù)據(jù)庫、die2 版圖設(shè)計數(shù)據(jù)庫、FOWLP 設(shè)計數(shù)據(jù)庫,以及某種形式的 FOWLP 系統(tǒng)源網(wǎng)表。現(xiàn)在,如果 FOWLP 設(shè)計數(shù)據(jù)庫(由封裝團隊負(fù)責(zé))已準(zhǔn)備就緒,而芯片數(shù)據(jù)庫(由 SoC 團隊負(fù)責(zé))仍在開發(fā)中,將會出現(xiàn)什么情況?對 FOWLP 設(shè)計人員來說,如果等到所有芯片構(gòu)建完畢并經(jīng)過驗證再運行 FOWLP LVS,結(jié)果發(fā)現(xiàn) FOWLP 設(shè)計數(shù)據(jù)庫中充斥了短路、開路和其他錯誤,將是完全行不通的。設(shè)計人員必須在完成完整的 LVS 驗證之前的早期驗證期間,采取一些做法來修復(fù)明顯的問題。為了實現(xiàn)和支持這種早期驗證,EDA 公司必須提供一種自動化 HDAP LVS 檢查方法,并且能夠在尚未取得所有最終組件的情況下運行。

設(shè)計依賴性

在 SoC LVS 驗證中,LVS 規(guī)則集僅依賴于 SoC 技術(shù)節(jié)點信息(即 GDSII 層)。但是,HDAP LVS 卻增加了另一個復(fù)雜問題:芯片布局。HDAP LVS 規(guī)則集依賴于中介層、 die1、die2 等 GDSII 層,也依賴于芯片(以及 2.5D 設(shè)計的中介層)的布局位置。反過來,這些信息則高度依賴于 HDAP 設(shè)計本身。晶圓代工廠/OSAT 構(gòu)建 HDAP LVS 規(guī)則集將是一個面面俱到的過程,需要考慮所有可能的芯片和中介層布局組合。盡管 “一個中介層上兩個芯片” 的設(shè)計在過去是可能的,但隨著 HDAP 中的裸片和基底數(shù)量的增加,很快就變得不切實際了。

04克服數(shù)據(jù) “不完整性”

因此,我們認(rèn)識到,與已經(jīng)存在了幾十年的 SoC 驗證流程相比,設(shè)計端的 HDAP 驗證流程還遠遠不夠成熟。這導(dǎo)致每個設(shè)計公司(以及潛在的每個 HDAP 設(shè)計周期)都可能具有不同類型的驗證數(shù)據(jù)。這種情況下,EDA 公司為 HDAP 驗證強制執(zhí)行某一組數(shù)據(jù)要求是不切實際的。相反,EDA 公司必須非常靈活,從某種意義上說,應(yīng)始終能夠利用可獲取的數(shù)據(jù)實現(xiàn)某種類型的 HDAP LVS 驗證。下面我們來探討一下,不同情況下的不同流程中的 LVS 驗證可能是什么樣子。

不含原理圖/設(shè)計意圖的封裝/中介層連接檢查

采用標(biāo)準(zhǔn)格式的 “源網(wǎng)表” 在封裝領(lǐng)域是個相對較新的概念。傳統(tǒng)上,封裝設(shè)計人員使用手動電子表格來規(guī)劃從裸片到封裝再到印刷電路板 (PCB) 上的外部 I/O 的連接。盡管在 HDAP 驗證中應(yīng)用這類方法非常困難,但一些設(shè)計人員出于不同的原因(傳統(tǒng)、管腳數(shù)目太少等)仍在使用電子表格。不用說,根據(jù)設(shè)計公司的舊有方法,這些電子表格可能有不同的格式和組織形式,所以 EDA 公司很難支持所有可能的電子表格。

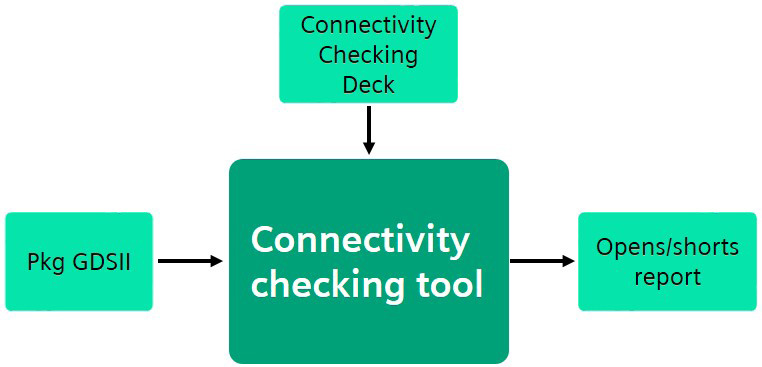

好吧,如果各種舊式電子表格不可用,設(shè)計人員還有封裝設(shè)計數(shù)據(jù)庫。難道就沒有什么簡單的開路/短路檢查辦法嗎?事實上,可能真有。鑒于設(shè)計人員擁有的數(shù)據(jù)量(僅限于封裝設(shè)計數(shù)據(jù)庫),EDA 工具可以使用一種仍對他們有用的簡單方法:

■ 如果封裝設(shè)計數(shù)據(jù)庫中的兩個形狀具有相同的文本標(biāo)簽,但在物理上是斷開連接的,則應(yīng)報告為 “開路”

■如果封裝設(shè)計數(shù)據(jù)庫中的兩個形狀具有不同的文本標(biāo)簽,但在物理上是相連接的,則應(yīng)報告為 “短路”

盡管這不是全面的 LVS(因為沒有可比較的設(shè)計意圖),但如果還沒有源網(wǎng)表,則仍不失為一種有價值的開路/短路檢查。下圖顯示了這種簡單的開路/短路檢查器的方框圖。

圖:不含設(shè)計意圖的封裝連接檢查

不含裸片管腳的封裝/中介層 LVS

下一個案例介紹一種更復(fù)雜的情形。驗證數(shù)據(jù)現(xiàn)在包括封裝設(shè)計數(shù)據(jù)庫和源網(wǎng)表,這樣設(shè)計人員應(yīng)該能夠運行真正的 LVS 驗證。他們的第一個念頭可能是,使用與 SoC LVS 相同的 LVS 工具和方法。但是,SoC 中的 LVS 概念依賴于 SoC 版圖設(shè)計數(shù)據(jù)庫和源網(wǎng)表中的“器件”的存在。器件可以是有源(晶體管)或無源(電阻器、電容器等)器件。由于大多數(shù) 2.5D-IC 和 FOWLP 設(shè)計不含任何器件(僅包含金屬布線),所以 SoC LVS 工具并不實用,因為它們并非針對 HDAP LVS 問題。

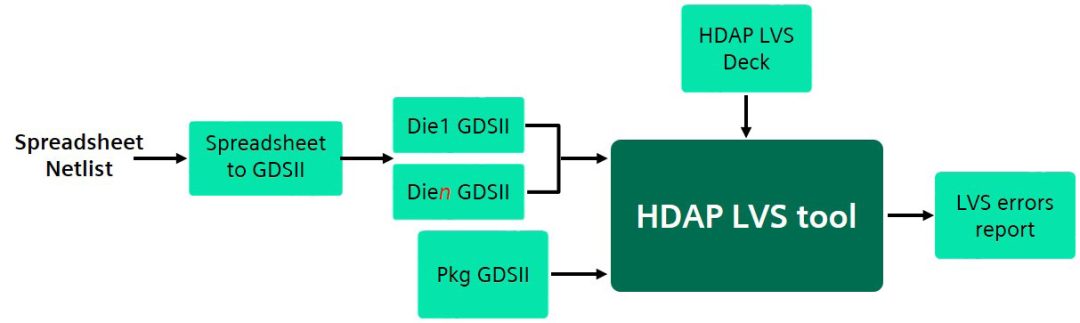

更為可行的解決方案是使用 HDAP 裝配級 LVS 工具,默認(rèn)情況下,這些工具會考慮封裝中不存在器件的情況。但此類工具不僅需要用于裝配級 LVS 的封裝版圖設(shè)計數(shù)據(jù)庫,還需要裸片的版圖設(shè)計數(shù)據(jù)庫。不過,這一限制是可以解決的。裝配級 LVS 工具經(jīng)過強化,可以從輸入電子表格網(wǎng)表(其中包括裸片凸塊 (x,y) 坐標(biāo)和管腳名稱)自動生成“占位符”裸片凸塊(表示裸片)。然后可以在裝配設(shè)計數(shù)據(jù)庫中使用此 “裸片占位符” 設(shè)計數(shù)據(jù)庫。設(shè)計人員僅使用封裝版圖設(shè)計數(shù)據(jù)庫和輸入電子表格網(wǎng)表,就能成功運行 HDAP LVS。下圖顯示了不含裸片管腳的 HDAP LVS 流程的方框圖。

圖:不含裸片管腳的 HDAP LVS

盡管這類流程為客戶提供了價值(捕獲封裝設(shè)計數(shù)據(jù)庫中的任何物理短路/開路),但不能保證完整的裝配能夠成功運行。如果 HDAP 中的裸片與封裝之間存在錯位怎么辦?

裝配級 LVS/LVL

在 HDAP 中,版圖與版圖比較 (LVL) 驗證跟 LVS 同樣重要,尤其在需要旋轉(zhuǎn)或縮放時(例如,將裸片收縮 10%,旋轉(zhuǎn) 90°,然后布置在封裝上)。設(shè)計人員必須確保,經(jīng)過這類處理之后,封裝凸塊與裸片凸塊之間仍有足夠的重疊。

僅幾何裸片接口

如果封裝設(shè)計人員能夠獲得裸片接口(凸塊)GDSII 層,那么除了封裝 LVS 之外,他們還可以執(zhí)行 LVL 驗證。設(shè)計人員可以使用 EDA 工具自動將裸片布置在封裝/中介層的頂面,并驗證對齊情況(根據(jù)需要)。

從連接的角度來看,將裸片和封裝都納入裝配級 LVS 時,通常會面臨一個挑戰(zhàn):SoC 團隊可能使用與封裝團隊不同的方法來命名裸片管腳/網(wǎng)絡(luò)。SoC 設(shè)計人員的 SoC 版圖設(shè)計數(shù)據(jù)庫中可能有一個名為 “A” 的裸片管腳,而在系統(tǒng)源網(wǎng)表和封裝設(shè)計數(shù)據(jù)庫中,該管腳被稱為 “A_B”。這種差異會導(dǎo)致許多虛假的 LVS 違規(guī)。但這一狀況與此流程無關(guān),因為 HDAP 設(shè)計人員從裸片導(dǎo)入的數(shù)據(jù)是 “接口物理幾何形狀”,而不是“接口邏輯管腳”。

也就是說,如果 SoC 設(shè)計數(shù)據(jù)庫或封裝設(shè)計數(shù)據(jù)庫中存在額外管腳,則在使用此流程時不會捕獲到該管腳。

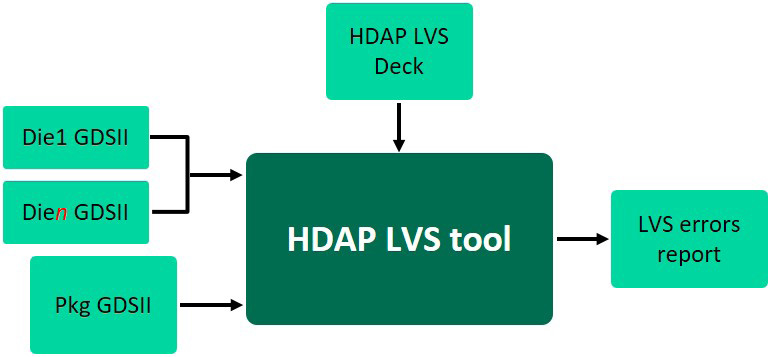

幾何裸片接口 + 邏輯裸片管腳

在此流程中,來自裸片的所有接口信息(幾何形狀和管腳)全部可用。HDAP 設(shè)計人員可以將此流程作為 signoff 流程來運行,因為其中包括了綜合驗證所需的全部數(shù)據(jù)。設(shè)計人員可以驗證所有可能的違規(guī):

■ 裝配級 LVS

■裝配級 LVL

■額外/缺失的管腳

至于 SoC 與封裝之間管腳名稱/網(wǎng)絡(luò)名稱不匹配的挑戰(zhàn), EDA 公司提供了新穎的方法來解決這類問題,避免導(dǎo)致虛假的 LVS 違規(guī)。例如,HDAP 設(shè)計人員可以在輸入中將這類不一致標(biāo)注為豁免。下圖顯示了包含裸片管腳的裝配級 LVS/LVL 流程。

圖:裝配級 LVS/LVL,包括裸片管腳

05HDAP LVS 流程

西門子提供了完整的自動化流程,可支持 HDAP 設(shè)計人員運行靈活的 HDAP LVS 驗證流程,同時兼顧各種級別的數(shù)據(jù) “不完整性” Xpedition Substrate Integrator (xSI) 工具可執(zhí)行 HDAP 系統(tǒng)級連接關(guān)系管理和規(guī)劃。xSI 工具生成系統(tǒng)源網(wǎng)表(采用電子表格格式),其中包括連接信息和裸片/封裝管腳的 x,y 位置。利用 Calibre 3DSTACK 工具可實現(xiàn)靈活的 HDAP 物理驗證(LVS 和 LVL),執(zhí)行上述任意和所有三種流程。Calibre 3DSTACK HDAP 規(guī)則集可使用 xSI 工具自動生成,以兼顧 HDAP 規(guī)則集的設(shè)計依賴性。

06總結(jié)

隨著 HDAP 技術(shù)逐漸成為主流,HDAP 設(shè)計人員需要來自晶圓代工廠/OSAT 和 EDA 公司的可靠設(shè)計與驗證流程。但與成熟的傳統(tǒng) SoC 驗證流程相比,目前可用的 HDAP 驗證流程還遠遠不夠成熟。在許多情況下,HDAP LVS “sign off”所需的驗證數(shù)據(jù)可能并不完整。EDA 公司必須提供工具和流程來兼顧各種級別的數(shù)據(jù)可用性,同時繼續(xù)支持 HDAP 設(shè)計人員執(zhí)行有用且有價值的 HDAP LVS 流程。

-

芯片

+關(guān)注

關(guān)注

460文章

52529瀏覽量

441309 -

集成電路

+關(guān)注

關(guān)注

5425文章

12076瀏覽量

368587 -

LVS

+關(guān)注

關(guān)注

1文章

38瀏覽量

10194 -

先進封裝

+關(guān)注

關(guān)注

2文章

476瀏覽量

636

原文標(biāo)題:一文了解 HDAP LVS/LVL 驗證

文章出處:【微信號:Mentor明導(dǎo),微信公眾號:西門子EDA】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

芯華章RISC-V敏捷驗證方案再升級

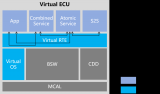

技術(shù)解讀 | 光庭信息虛擬ECU技術(shù)賦能SOA化MCU軟件的早期驗證與集成加速

《電子發(fā)燒友電子設(shè)計周報》聚焦硬科技領(lǐng)域核心價值 第14期:2025.06.2--2025.06.6

芯華章攜手EDA國創(chuàng)中心推出數(shù)字芯片驗證大模型ChatDV

硬件輔助驗證(HAV) 對軟件驗證的價值

FPGA EDA軟件的位流驗證

芯華章以AI+EDA重塑芯片驗證效率

面向HDAP設(shè)計的LVS/LVL驗證

面向HDAP設(shè)計的LVS/LVL驗證

評論