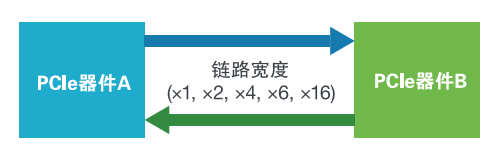

在計(jì)算和網(wǎng)絡(luò)應(yīng)用中采用PCI Express? (PCIe) 接口非常普遍,這些應(yīng)用包括中央處理器(CPU)、圖形處理器(GPU)、網(wǎng)絡(luò)接口卡(NIC)、交換機(jī)、服務(wù)器以及諸如固態(tài)設(shè)備(SSD)之類更 新型的存儲(chǔ)系統(tǒng),等等。然而,當(dāng)今的網(wǎng)絡(luò)和快速興起的人工智能(AI)應(yīng)用均要求在加速器 和GPU中采用更大的帶寬以及更快的互連,以便發(fā)送和接收更大量的數(shù)據(jù)。

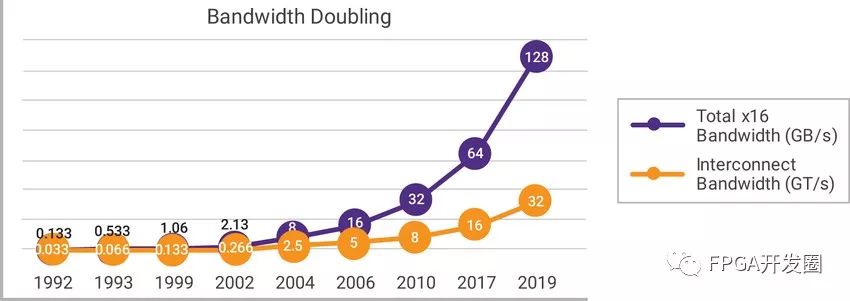

鑒于PCIe在此類應(yīng)用中的廣泛使用以及越來越大的帶寬需求,PCI-SIG產(chǎn)業(yè)聯(lián)盟最近宣布了最新規(guī)范PCIe 5.0,它把數(shù)據(jù)速率提高到32GT/s,并使鏈路帶寬增加一倍,從64GB/s 提高到128GB/s。 圖1顯示了PCIe 互連和總帶寬的演變。

圖1:PCI-SIG帶寬增長(zhǎng)

PCIe 5.0規(guī)范主要處理速度提升以及相關(guān)物理層(PHY層)的修改。然而,轉(zhuǎn)向32GT/s設(shè)計(jì)時(shí),將會(huì)帶 來 系統(tǒng)設(shè)計(jì)人員及PHY設(shè)計(jì)人員都必須考慮的幾項(xiàng)挑戰(zhàn)。本文描述了轉(zhuǎn)向32GT/s速度的PCIe設(shè)計(jì)所面臨的挑戰(zhàn),以及設(shè)計(jì)人員如何能夠利用新的PCIe 5.0接口成功設(shè)計(jì)出系統(tǒng)。

系統(tǒng)設(shè)計(jì)師面臨的挑戰(zhàn)

印刷電路板(PCB)的走線、連接器、電纜乃至IC封裝都是系統(tǒng)級(jí)的帶寬限制因素,它們使 得高 數(shù)據(jù) 速率 的設(shè)計(jì)變得具有挑戰(zhàn)性。高信號(hào)頻率增加了銅損和功率損耗,這會(huì)導(dǎo)致傳輸距離減小。另外,更高 信號(hào) 頻 率中存在的通道損失會(huì)導(dǎo)致信號(hào)完整性(SI)問題。

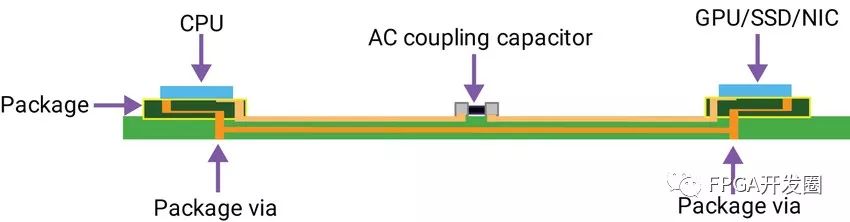

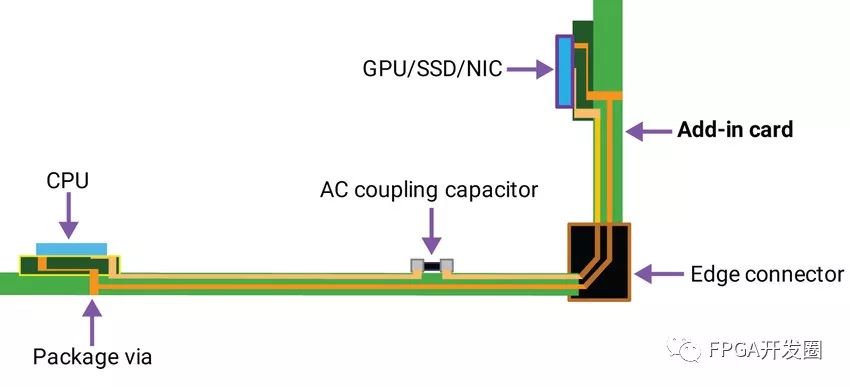

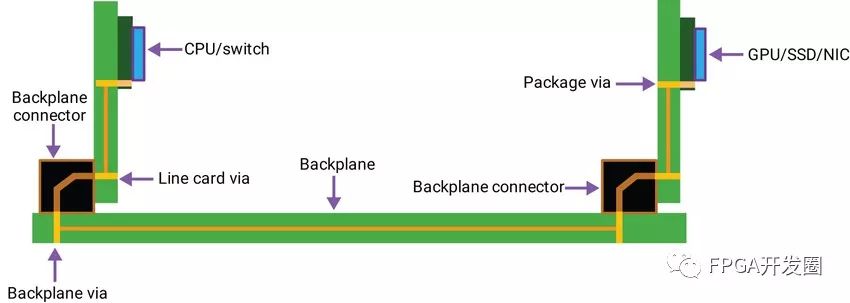

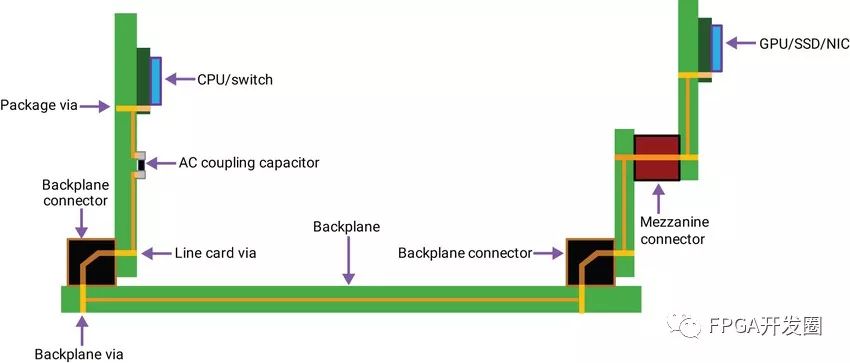

為了滿足各種應(yīng)用的需求,PCIe通道的種類有很多,既有不包含連接器的“芯片到芯片”拓?fù)浣Y(jié)構(gòu),也 有 包 含背板接口的復(fù)雜服務(wù)器拓?fù)浣Y(jié)構(gòu),而且這樣的背板 接口還包括多個(gè) PCB卡和兩個(gè) 或多個(gè)連 接器。 如圖2至圖5所示,大多數(shù)PCIe通道在每一端都由一個(gè)IC封裝組成,而且?guī)в卸鄠€(gè)PCB,其中包括: 處 理 器 板、附加卡和轉(zhuǎn)接卡;它們?nèi)窟B接至一個(gè)或多個(gè)夾層卡或PCIe卡機(jī)電(CEM)連接器。

圖2:“芯片到芯片”接口,最簡(jiǎn)單的通道,沒有連接器

圖3(a):帶有一個(gè)夾層連接器的通道

圖3(b):帶有一個(gè)邊緣連接器(附加卡)的通道

圖4(a):帶有兩個(gè)連接器并使用一個(gè)轉(zhuǎn)接卡和一個(gè)附加卡的通道

圖4(b):帶有兩個(gè)線路卡和兩個(gè)連接器的標(biāo)準(zhǔn)背板通道

圖5:具有兩個(gè)以上連接器的復(fù)雜背板通道

歷史上,PCIe系統(tǒng)設(shè)計(jì)人員把通用低成本FR4 PCB材料和引線鍵合(wirebond)封裝用于 高達(dá) 8GT/s 數(shù) 據(jù) 速率(Gen3)的大多數(shù)應(yīng)用,這種做法已被證明是成功的。但是,在32GT/s的數(shù) 據(jù)速率下 使用 這 種材料 和封裝并不可行。

由于通道損耗的增加,即使在最大速率為16GT/s的PCIe 4.0中(它對(duì)于在下一代電路板設(shè)計(jì)中保持 現(xiàn)有 的 通道長(zhǎng)度是必不可少的),大多數(shù)設(shè)計(jì)人員也正在從FR4 PCB轉(zhuǎn)向更低損耗的材料,如MEGTRON。 PCB在 設(shè)計(jì)上也可以在走線之間采用更寬的空間間隔,以便進(jìn)一步提高系統(tǒng)級(jí)SI性能。同樣,對(duì)于SI,許多設(shè)計(jì)將 使用增強(qiáng)的CEM連接器或定制的夾層連接器,并且將回鉆PCB通孔,以便盡量縮短截線(stub)長(zhǎng)度。在 某些通道很長(zhǎng)的情況下,也可以使用重定時(shí)器。

然而,所有這些增強(qiáng)都是有代價(jià)的。MEGTRON材料的成本可能比標(biāo)準(zhǔn)FR4材料高出1.2倍至2.5倍,而且PCB 走線可能需要進(jìn)一步加大間隔以獲得更好的抖動(dòng)(jitter)性能,從而導(dǎo)致更大、更昂貴的 PCB。如果 采用 截線(stub)回鉆(電路板制造過程中的一個(gè)增量步驟),也會(huì)增加 PCB的總成本。 另一個(gè)需要考慮 的因 素是,增強(qiáng)的和定制的表面貼裝連接器如何比標(biāo)準(zhǔn)通孔CEM連接器更為昂貴。此外,采用時(shí)脈 重驅(qū)器會(huì) 增 加物料清單(BOM)成本、數(shù)據(jù)路徑延遲和系統(tǒng)功耗;它們也會(huì)占據(jù)PCB上額外區(qū)域,這會(huì)增加電路 板及 組裝成本。

為了驗(yàn)證其設(shè)計(jì),系統(tǒng)設(shè)計(jì)人員必須與信號(hào)完整性工程師、封裝設(shè)計(jì)人員、SoC設(shè)計(jì)人員 以及電 路板 布局 設(shè)計(jì)人員密切合作,對(duì)其通道中的每個(gè)組件進(jìn)行建模,并驗(yàn)證其整個(gè)端到端性能。

PHY設(shè)計(jì)師面臨的挑戰(zhàn)

對(duì)16GT/s PHY設(shè)計(jì)進(jìn)行漸進(jìn)式改進(jìn)在大多數(shù)應(yīng)用中并不足以滿足PCIe 5.0通道 要求。 由于在 32GT/s 速 度下信道損耗顯著增加,發(fā)射器(TX)和接收器(RX)中的均衡電路需要顯著的改進(jìn)。另外,更 嚴(yán) 格 的 抖動(dòng)參數(shù)和抖動(dòng)限制以及回波損耗規(guī)格也要求在TX和RX中重新設(shè)計(jì)許多子電路。

預(yù)計(jì)PCIe 5.0的PHY將通過控制器以及單獨(dú)參考時(shí)鐘獨(dú)立擴(kuò)展頻譜計(jì)時(shí)(SRIS)來支持通道通路裕量(Lane margining)請(qǐng)保留英文描述等功能,同時(shí)滿足在過程、電壓和溫度角(Corner)建議保留英文 等方 面 更 嚴(yán)格的時(shí)序和抖動(dòng)要求。

此類增強(qiáng)和額外的限制使得設(shè)計(jì)PCIe 5.0 32GT/s PHY變得非常復(fù)雜,需要許多方面的能力來實(shí)現(xiàn)低功耗、小面積和低延遲的PHY,同時(shí)提供最佳信號(hào)和電源完整性(PI)性能。

具有精確模型、經(jīng)過硅驗(yàn)證的PHY使得設(shè)計(jì)人員能夠?qū)Χ说蕉送ǖ肋M(jìn)行建模、設(shè)計(jì)和模擬,以便對(duì) 系統(tǒng) 設(shè) 計(jì)進(jìn)行驗(yàn)證和優(yōu)化。

小結(jié)

在諸如網(wǎng)絡(luò)、存儲(chǔ)和新興人工智能等數(shù)據(jù)密集型應(yīng)用中,對(duì)帶寬的要求越來越高,這迫切需要更快的互連,例如在32GT/s速度下的新型PCIe 5.0技術(shù)。但是,設(shè)計(jì)人員必須了解并考慮在轉(zhuǎn)向32GT/s PCIe設(shè)計(jì)時(shí) 面臨 的諸多挑戰(zhàn)。在更高的數(shù)據(jù)速率下解決信號(hào)完整性、封裝和通 道性能等問 題需要在多 個(gè)領(lǐng)域具 備充分 能 力。這就是為什么越來越多的片上系統(tǒng)(SoC)設(shè)計(jì)人員采用經(jīng) 過驗(yàn)證的第三方 IP來進(jìn)行成功的 IC集成的 原因。

許多企業(yè)都在利用諸如Synopsys這樣可靠且經(jīng)過驗(yàn)證的第三方IP和電源完整性服務(wù)。借助于Synopsys以數(shù)十年P(guān)CIe專業(yè)知識(shí)為基礎(chǔ)的面向PCIe 5.0的IP,SoC設(shè)計(jì) 人員可 以盡早啟 動(dòng)其32GT/s 的設(shè)計(jì)。 SoC設(shè)計(jì) 人 員可以與Synopsys合作,以討論在更高數(shù)據(jù)速率下PCIe通道的性能需求,同時(shí)解決IP集成、時(shí)序收斂、信 號(hào)完整性、封裝和制造方面的需求。我們將在隨后發(fā)布的文檔中詳細(xì)闡述每項(xiàng)挑戰(zhàn)。

-

印刷電路板

+關(guān)注

關(guān)注

4文章

833瀏覽量

35909 -

cpu

+關(guān)注

關(guān)注

68文章

11049瀏覽量

216164 -

PCIe

+關(guān)注

關(guān)注

16文章

1328瀏覽量

84769

原文標(biāo)題:轉(zhuǎn)向32GT/s PCI Express設(shè)計(jì)所面臨的挑戰(zhàn)

文章出處:【微信號(hào):FPGA-EETrend,微信公眾號(hào):FPGA開發(fā)圈】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

PCIe 4.0 SSD尚未起飛,就要迎戰(zhàn)速度翻倍的5.0

移動(dòng)電視射頻技術(shù)面臨什么挑戰(zhàn)

DVB-H接收器設(shè)計(jì)所面臨的機(jī)遇和挑戰(zhàn)討論

調(diào)試速度高達(dá)幾個(gè)Gb每秒的連接時(shí)所面臨的挑戰(zhàn)

電子系統(tǒng)設(shè)計(jì)所面臨的挑戰(zhàn)是什么

DVB-H接收器設(shè)計(jì)所面臨的機(jī)遇和挑戰(zhàn)是什么?

5G終端天線研發(fā)所面臨的主要挑戰(zhàn)有哪些?如何去解決?

PCIe 4.0 SSD尚未起飛,就要迎戰(zhàn)速度翻倍的5.0

DVB-H接收器設(shè)計(jì)所面臨的機(jī)遇和挑戰(zhàn)

什么是 PCIe 5.0? PCIe 5.0規(guī)范以及挑戰(zhàn)

泰克PCIe Gen 5 Tx一致性測(cè)試解決方案

如何破解PCIe 6.0帶來的芯片設(shè)計(jì)新挑戰(zhàn)?

如何破解PCIe 6.0帶來芯片設(shè)計(jì)新挑戰(zhàn)?

PCIe 6.0的優(yōu)化設(shè)計(jì)方案探討分析

轉(zhuǎn)向32GT/s速度的PCIe設(shè)計(jì)所面臨的挑戰(zhàn)

轉(zhuǎn)向32GT/s速度的PCIe設(shè)計(jì)所面臨的挑戰(zhàn)

評(píng)論