同構(gòu)融合技術(shù)

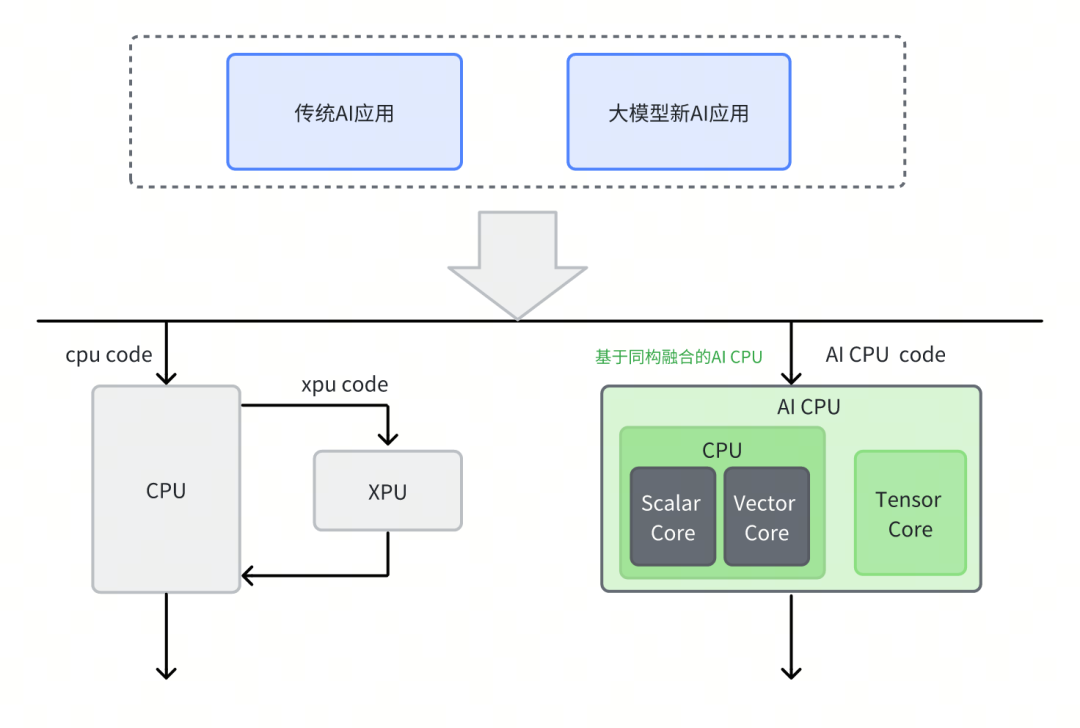

為了加速AI計(jì)算,芯片企業(yè)設(shè)計(jì)了多種專用處理器架構(gòu),如GPGPU、NPU、TPU等。這些專用處理器架構(gòu)在執(zhí)行調(diào)度代碼及應(yīng)用層代碼時(shí),需要主控CPU的配合,如下圖所示。因此,通常需要構(gòu)建復(fù)雜的異構(gòu)調(diào)度系統(tǒng)來協(xié)調(diào)CPU和XPU的額外數(shù)據(jù)交互和同步。

進(jìn)迭時(shí)空踐行的同構(gòu)融合技術(shù),創(chuàng)新性地在CPU內(nèi)集成TensorCore,以RISC-V指令集為統(tǒng)一的軟硬件接口,驅(qū)動(dòng)Scalar標(biāo)量算力、Vector向量算力和 Matrix AI算力,支持軟件和AI模型同時(shí)在RISC-V AI核上運(yùn)行,并通過程序正常跳轉(zhuǎn)實(shí)現(xiàn)軟件和AI模型之間的事件和數(shù)據(jù)交互,進(jìn)而完成整個(gè)AI應(yīng)用執(zhí)行。我們將這種使用同構(gòu)融合技術(shù),得到具有AI算力的CPU稱為AI CPU。

同構(gòu)融合技術(shù)以更輕的軟件基礎(chǔ)設(shè)施構(gòu)建接近Nvidia的軟件層級(jí)

雖然市面上已有多種不同架構(gòu)且硬件做的非常出色的AI加速器,但是除了AIOT細(xì)分場(chǎng)景之外,Nvidia占據(jù)了AI計(jì)算絕大多數(shù)市場(chǎng)份額,成為AI計(jì)算主流架構(gòu),并深刻影響工業(yè)界學(xué)術(shù)界AI計(jì)算的發(fā)展。Nvidia通過CUDA將異構(gòu)開發(fā)的門檻降至最低,并基于多層級(jí)的軟件棧構(gòu)建了護(hù)城河。基于這些軟件棧,全球開發(fā)者都在壯大Nvidia生態(tài)。很多企業(yè)的GPGPU發(fā)展策略是硬件上學(xué)習(xí)Nvidia,軟件上兼容CUDA生態(tài)。由于很難跟上Nvidia的快速迭代,這條路徑并不容易實(shí)現(xiàn)。

同構(gòu)融合有望成為新的發(fā)展路徑。相比于異構(gòu)加速器和CPU的組合,同構(gòu)融合技術(shù)在硬件層面上對(duì)AI算力和通用CPU進(jìn)行了更高層次的封裝,用戶不需要關(guān)心主控CPU和異構(gòu)加速器之間的數(shù)據(jù)同步,并且保留了通用CPU的調(diào)試和開發(fā)方式。廠商不需要開發(fā)復(fù)雜的異構(gòu)調(diào)度系統(tǒng),也不需要開發(fā)額外的驅(qū)動(dòng)管理就可以讓開發(fā)者便捷的使用AI算力。另外,同構(gòu)融合技術(shù)中CPU的通用性和RISC-V架構(gòu)良好的開源生態(tài)基礎(chǔ),進(jìn)一步降低了需要自建軟件棧的復(fù)雜度。

綜上,進(jìn)迭時(shí)空基于開源軟件生態(tài),以更輕的基礎(chǔ)軟件設(shè)施,構(gòu)建了接近Nvidia的軟件層級(jí),如下圖所示。我們的目標(biāo)是,基于這些軟件層級(jí),達(dá)到接近Nvidia的AI通用性。

1 | 在模型加速層面,與Nvidia一樣,進(jìn)迭時(shí)空的推理引擎可以非常便捷的接入各主流第三方框架 |

2 | 在Tensor及多維數(shù)據(jù)塊層面,SpineDNN、SpineTriton及SpineJit分別對(duì)標(biāo)CUDNN、CUTLASS及CUTE |

3 | 在Scalar及Vector層面,SpineDPC++可以對(duì)標(biāo)CUDA |

4 | 最底層的寄存器層面,標(biāo)準(zhǔn)的Intrinsic接口則對(duì)標(biāo)Nvidia的PTX接口 |

進(jìn)迭時(shí)空同構(gòu)融合技術(shù)實(shí)踐

進(jìn)迭時(shí)空基于同構(gòu)融合技術(shù)完成兩代通用RISC-V AI核的研發(fā)。

第一代RISC-V AI核A60實(shí)現(xiàn)2Tops算力,支持INT8等數(shù)據(jù)格式。A60核已經(jīng)應(yīng)用于RISC-V AI CPU芯片K1,實(shí)踐表明,同構(gòu)融合AI算力可以無縫運(yùn)行所有AI算法,更安全地加速?gòu)腡EE到REE所有AI應(yīng)用。RISC-V AI CPU芯片K1也是第一個(gè)完整提供Scalar、Vector和Matrix三個(gè)維度關(guān)鍵算力的RISC-V芯片。在運(yùn)行常見的AI算法時(shí),K1的實(shí)際性能是傳統(tǒng)芯片的3-5倍,某些AI應(yīng)用幀率提升可達(dá)10倍以上。

尤其是在運(yùn)行大模型算法時(shí),Matrix算力可以從容應(yīng)對(duì)prefill階段的算力需求,CPU出色的訪存系統(tǒng)可以解決decode階段的帶寬需求,無需構(gòu)建復(fù)雜的異構(gòu)計(jì)算調(diào)度系統(tǒng)。此外,由于CPU的通用性,可以支持幾乎所有低bit量化方式,將帶寬需求降至最低。

更重要的是,將整個(gè)AI應(yīng)用涉及的計(jì)算步驟全部遷移至AI CPU上,還可以為客戶提供更加簡(jiǎn)單高效的開發(fā)方式。不僅能夠避免在多個(gè)硬件設(shè)備上開發(fā)和調(diào)試,而且在一個(gè)編程模型覆蓋AI開發(fā)全過程,能夠讓部署和調(diào)試變得輕松,讓算法快速實(shí)現(xiàn)價(jià)值。例如,K1芯片在客戶場(chǎng)景下,可以把在傳統(tǒng)NPU上適配新算法所需的3-6個(gè)月時(shí)間壓縮到1周以內(nèi),K1芯片已支持多個(gè)客戶在語音和機(jī)器視覺領(lǐng)域快速開發(fā)了基于最新AI大模型的產(chǎn)品。

第二代RISC-V AI核A100已經(jīng)研發(fā)完畢,預(yù)期無論在大模型運(yùn)行效率方面,還是運(yùn)行傳統(tǒng)AI效率方面都能達(dá)到業(yè)界先進(jìn)水平。

此外在算力堆疊方面,同構(gòu)融合技術(shù)路線通過采用Core-to-Core coherence和Cluster-to-Cluster coherence,能以與GPU相同的技術(shù)實(shí)現(xiàn)多芯片級(jí)聯(lián)和算力堆疊。與總線的Die2Die一致性技術(shù)結(jié)合后,通往多芯片算力堆疊的規(guī)模有望接近現(xiàn)有最先進(jìn)GPU集群。

同構(gòu)融合技術(shù)適合運(yùn)行MoE大模型

MOE模型(Mixture of Experts,混合專家模型)是一種基于分而治之策略的神經(jīng)網(wǎng)絡(luò)架構(gòu),它將復(fù)雜的問題分解為多個(gè)子問題,每個(gè)子問題由一個(gè)獨(dú)立的模型(稱為專家)進(jìn)行處理。MOE模型在單請(qǐng)求推理場(chǎng)景,每個(gè)token只需要使用部分專家參與計(jì)算。這些專家共同組成了MOE模型的激活參數(shù)。以DeepSeek-R1模型為例,671B的模型,只有37B的激活參數(shù)。對(duì)于FP8的模型,相當(dāng)于需要將近700GB的容量來存放模型所有的權(quán)重,但是在進(jìn)行單請(qǐng)求推理時(shí),每個(gè)token只需要使用將近40GB的權(quán)重。相比于Dense模型,MOE模型是一個(gè)大容量,弱帶寬的推理需求。相較于GDDR和HBM,內(nèi)存容量更容易擴(kuò)展;再加上專家的選擇是動(dòng)態(tài)的,其計(jì)算和訪存模式是CPU極其擅長(zhǎng)的。

GPU與NPU適合密集的重復(fù)計(jì)算模式,而CPU適合復(fù)雜調(diào)度場(chǎng)景下的計(jì)算模式,AI CPU介于兩者之間。MoE的興起,代表了一個(gè)兼具大容量與復(fù)雜邏輯的大模型發(fā)展趨勢(shì),而這正是AI CPU的發(fā)力場(chǎng)景。

-

AI

+關(guān)注

關(guān)注

88文章

35168瀏覽量

280117 -

大模型

+關(guān)注

關(guān)注

2文章

3147瀏覽量

4079 -

進(jìn)迭時(shí)空

+關(guān)注

關(guān)注

0文章

31瀏覽量

138

發(fā)布評(píng)論請(qǐng)先 登錄

RISC-V架構(gòu)下AI融合算力及其軟件棧實(shí)踐

迎接泛機(jī)器人時(shí)代:進(jìn)迭時(shí)空如何以RISC-V架構(gòu)數(shù)智未來

進(jìn)迭時(shí)空第三代高性能核X200研發(fā)進(jìn)展

進(jìn)迭時(shí)空攜手珠海共建RISC-V生態(tài)應(yīng)用中心

高校賽事 | 進(jìn)迭時(shí)空攜手藍(lán)橋杯,誠(chéng)邀全國(guó)高校學(xué)子共啟RISC-V人工智能應(yīng)用創(chuàng)新賽道

大象機(jī)器人攜手進(jìn)迭時(shí)空推出 RISC-V 全棧開源六軸機(jī)械臂產(chǎn)品

大象機(jī)器人×進(jìn)迭時(shí)空聯(lián)合發(fā)布全球首款RISC-V全棧開源小六軸機(jī)械臂

RISC-V+OpenHarmony5.0:進(jìn)迭時(shí)空與中科院共筑數(shù)字世界新基石

K1 AI CPU基于llama.cpp與Ollama的大模型部署實(shí)踐

進(jìn)迭時(shí)空完成A+輪數(shù)億元融資 加速RISC-V AI CPU產(chǎn)品迭代

進(jìn)迭時(shí)空亮相RISC-V產(chǎn)業(yè)發(fā)展大會(huì):新AI CPU引領(lǐng)大模型時(shí)代

業(yè)內(nèi)首顆8核RISC-V終端AI CPU量產(chǎn)芯片K1,進(jìn)迭時(shí)空與中國(guó)移動(dòng)用芯共創(chuàng)AI+時(shí)代

Banana Pi BPI-F3 進(jìn)迭時(shí)空RISC-V架構(gòu)下,AI融合算力及其軟件棧實(shí)踐

RISC-V架構(gòu)下DSA-AI算力的更多可能性:Banana Pi BPI-F3進(jìn)迭時(shí)空

進(jìn)迭時(shí)空同構(gòu)融合技術(shù)加速大模型AI應(yīng)用創(chuàng)新

進(jìn)迭時(shí)空同構(gòu)融合技術(shù)加速大模型AI應(yīng)用創(chuàng)新

評(píng)論