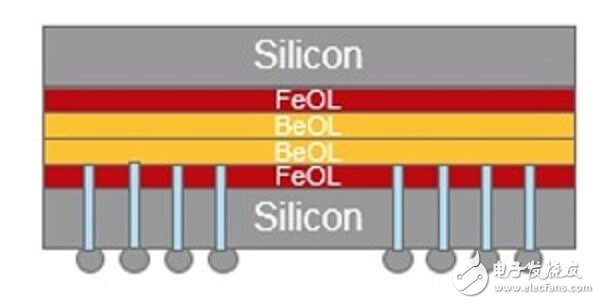

臺積電目前正在圣克拉拉舉辦第24屆年度技術研討會,它剛剛發布了一個可以為顯卡帶來革命性變革的技術Wafer-on-Wafer (WoW,堆疊晶圓)技術。顧名思義,WoW的工作方式是垂直堆疊層,而不是將它們水平放置在電路板上,就像3D NAND閃存在現代固態驅動器中堆疊的方式一樣。這意味Nvidia和AMD GPU不需要增加其物理尺寸或縮小制造工藝即可獲性能提升。

Wafer-on-Wafer (WoW,堆疊晶圓)技術通過使用形成硅通孔(TSV)連接的10微米孔彼此接觸。臺積電的合作伙伴Cadence解釋說,Wafer-on-Wafer (WoW,堆疊晶圓)設計可以放置在中介層上,將一個連接路由到另一個連接,創建一個雙晶立方體。甚至可以使用WoW方法垂直堆疊兩個以上的晶圓。

該技術將允許更多的內核被塞入一個封裝中,并且意味著每個芯片可以非常快速并且以最小的延遲相互通信。尤其令人感興趣的是,制造商可以使用WoW的方式將兩個GPU放在一張卡上,并將其作為產品更新發布,從而創建基本上兩個GPU,而不會將其顯示為操作系統的多GPU設置。

WoW現在最大的問題是晶圓產量。當它們被粘合在一起時,如果只有一個晶圓壞了,那么即使兩個晶圓都沒有問題,它們也必須被丟棄。這意味著該工藝需要在具有高成品率的生產節點上使用,例如臺積電的16納米工藝,以降低成本。不過,該公司的目標是在未來的7nm和5nm制造工藝節點上使用WoW技術。

-

臺積電

+關注

關注

44文章

5755瀏覽量

169855 -

晶圓

+關注

關注

53文章

5165瀏覽量

129826

發布評論請先 登錄

臺積電發布堆疊晶圓技術 目標是在5NM制造工藝上使用

臺積電發布堆疊晶圓技術 目標是在5NM制造工藝上使用

評論