引言:本文以TI的ADS4249(ADC)和DAC3482(DAC)之間的接口為例,介紹Altera FPGA與ADC/DAC之間的DDR LVDS接口設計以及時序約束詳細設計。本文介紹的實例可方便擴展到具有類似接口格式的其他高速數據轉換器設計。

1.概述

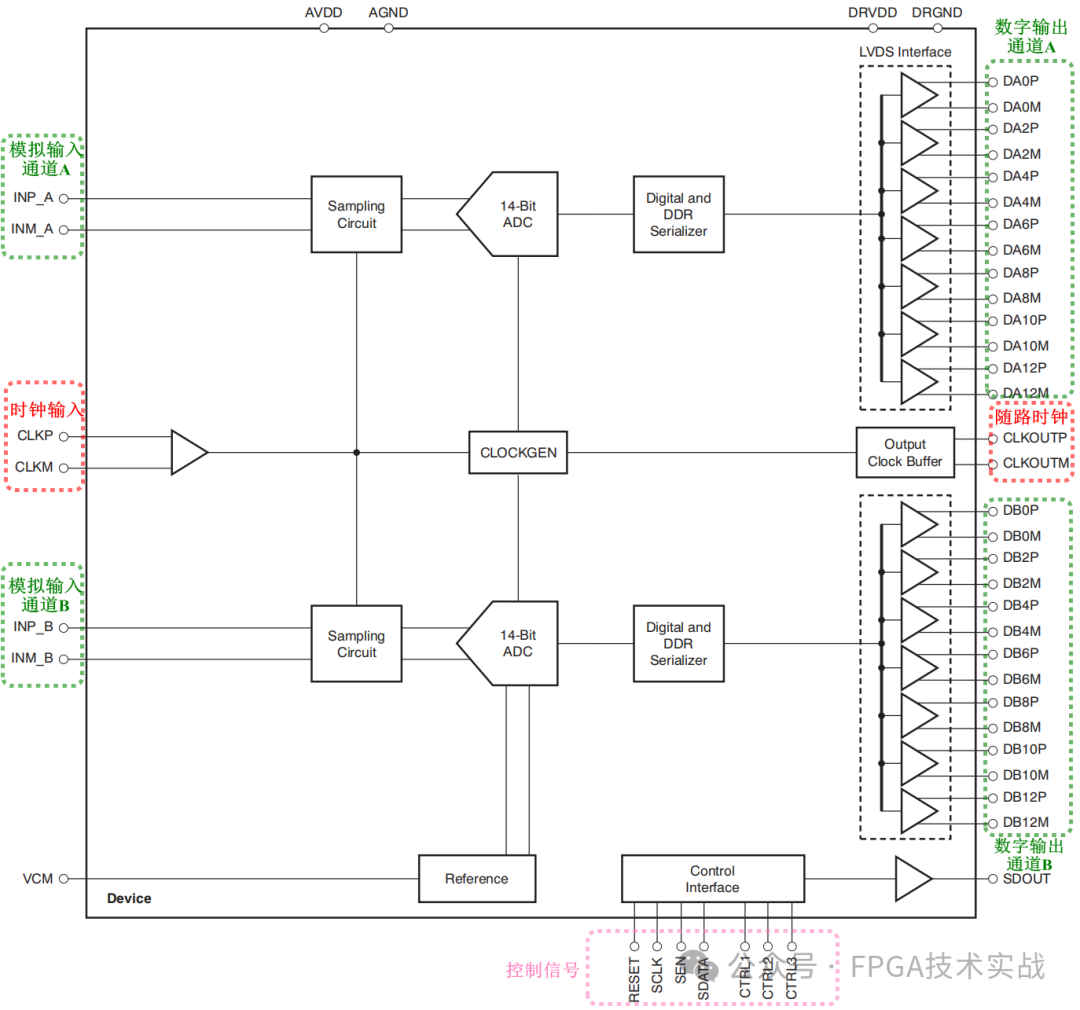

ADS4249是一款雙通道、14位、250MSPS ADC,具有雙總線、字節級數字接口。ADS4249接口示例適用于許多TI高速ADC,包括以下系列:ADS41xx、ADS42xx和ADS62Pxx。ADS4249對外接口如圖1所示。

圖1:ADS4249對外接口

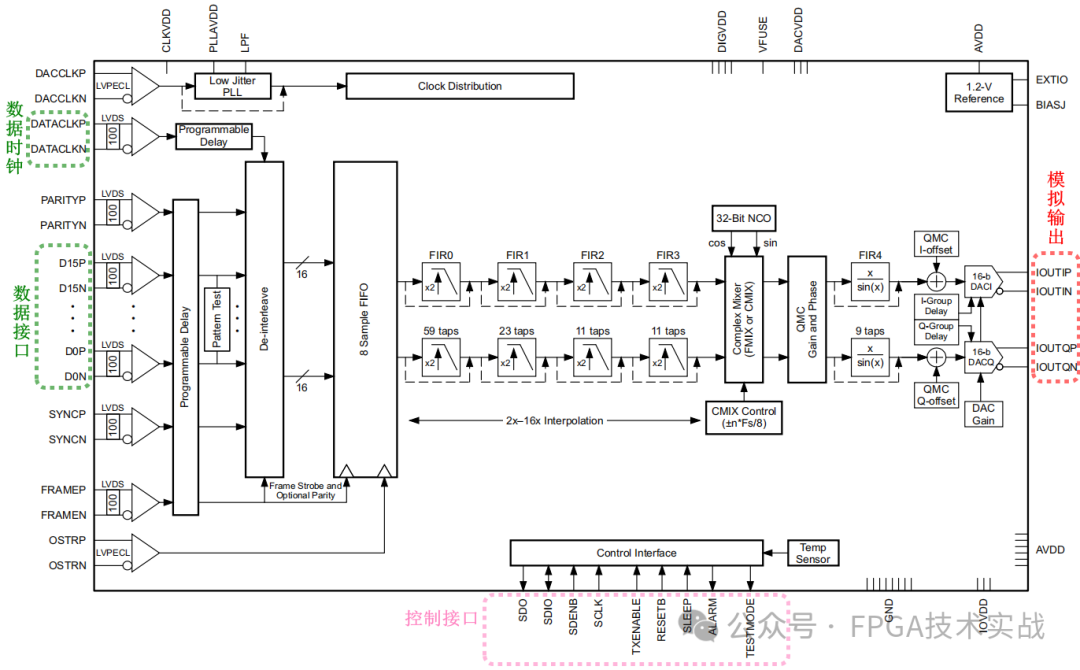

DAC3482是一個雙通道、16位、1.25GSPS DAC,具有單總線采樣數字接口。本文代碼示例的設計數據速率為250MSPS,同樣的概念擴展到涵蓋大多數LVDS、不同數據速率的高速DAC。DAC3482對外接口如圖2所示。

圖2:DAC3482對外接口

2.硬件框圖

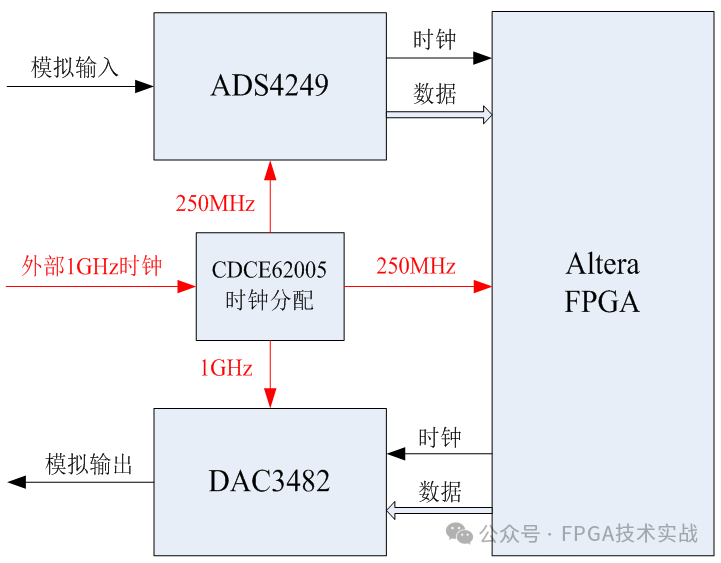

ADS4249及DAC3482硬件連接框圖如圖3所示。

圖3:ADS4249及DAC3482硬件連接框圖

CDCE62005接收外部時鐘1GHz,經分頻后向ADS4249提供250MHz時鐘,ADS4249輸出與數據同步的250 MHz源同步時鐘。

同時,CDCE62005將1GHz時鐘分配給DAC,還將時鐘除以4,向FPGA發送250MHz時鐘,以創建傳輸時鐘域。DAC3482的插值設置為4,數據速率為250MSPS,最終DAC輸出速率為1GSPS。

3. FPGA軟件設計

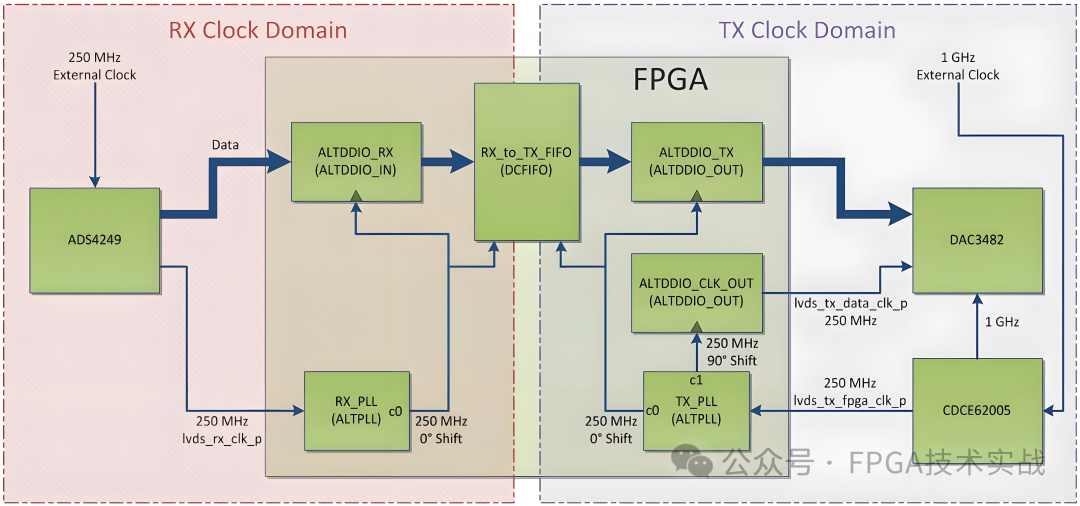

以下部分將詳細分解示例代碼,示例代碼的簡化框圖如下圖4所示。

圖4:FPGA架構和時鐘域框圖

2.1 輸入時鐘和時鐘域

如圖4示例代碼中,有兩個時鐘發送到FPGA,在FPGA內形成兩個時鐘域(接收時鐘域和發送時鐘域)。ADS4249源同步數據時鐘lvds_rx_clk_p為接收域提供250MHz的輸入時鐘。FPGA的發送側從CDCE62005接收250MHz時鐘lvds_tx_fpga_clk_p。

兩個輸入時鐘都被引入FPGA內部鎖相環(ALTPLL),鎖相環產生內部時鐘。

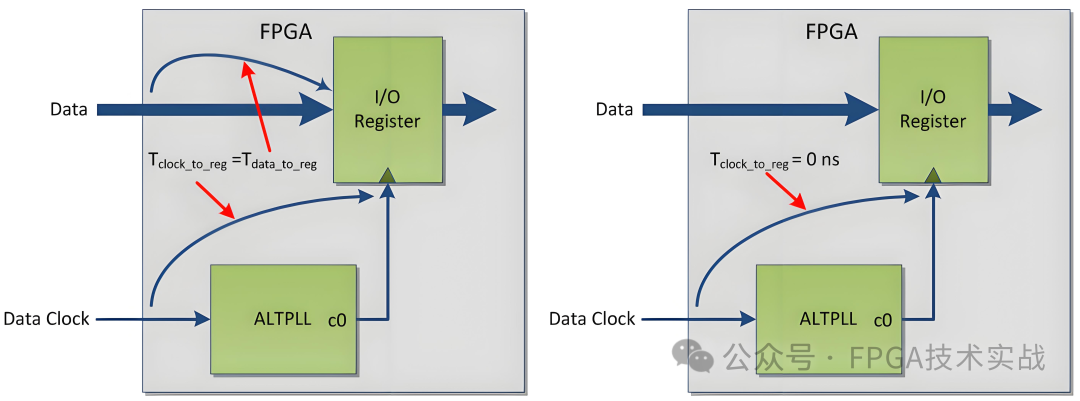

圖5:ALTPLL中的源同步補償與正常補償

在RX側,ADS4249提供中心對齊的源同步數據和時鐘。對于源同步接口,FPGA的目標是保持輸入引腳處的時鐘與數據相位關系在內部I/O寄存器處相同,以保持最大的時序裕度。

因此,RX PLL被設置為使用源同步補償模式和0°相移簡單地重建輸入時鐘。源同步補償模式通過匹配從時鐘輸入引腳到I/O寄存器的延遲和從數據輸入引腳到輸入/輸出寄存器的延遲來保持FPGA內部ADS4249的時鐘和數據之間的相位關系。請注意,FPGA內部不需要時鐘相移,因為ADS4249已經提供了一個中心對齊的數據時鐘,FPGA PLL的源同步補償保持了這種關系。圖5顯示了FPGA中源同步補償的框圖。

在TX側,從DAC3482從CDCE62005接收時鐘,該時鐘沒有與之相關的數據,因此不需要源同步模式,因為沒有數據與時鐘相位關系需要維護。因此,TX側的PLL以0°相移重新創建TX輸入時鐘,但由于沒有與此時鐘相關的數據,因此使用正常補償模式。

正常補償模式補償了全局時鐘網絡從輸入引腳到被計時寄存器的延遲,如圖5所示。0°相移時鐘用于將數據從RX輸出到TX FIFO,并將數據從FPGA輸出到DAC。DAC3482需要中心對齊的數據,因此PLL也用于創建相對于0°相移時鐘具有90°相移的時鐘。90°相移時鐘用于創建TX輸出時鐘,使數據和數據時鐘之間存在90°相位差。這在FPGA和DAC之間創建了一個源同步、中心對齊的接口。

2.2 接口架構

2.2.1 ADC數據輸入架構

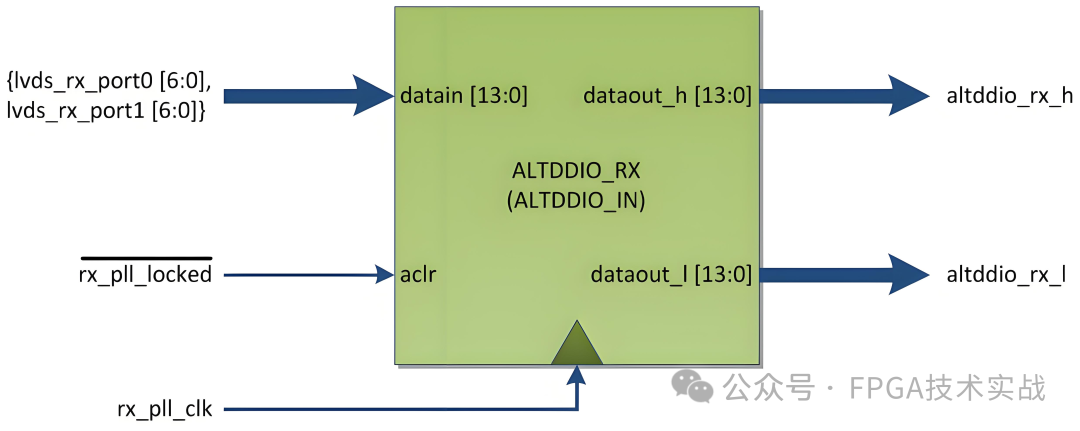

ADC輸入接口由ALTDDIO_IN 函數創建。該塊具有雙倍數據速率(DDR)輸入寄存器,可捕獲輸入時鐘上升沿和下降沿的數據。單數據速率(SDR)數據在輸入時鐘的上升沿從塊中時鐘輸出,其中dataout_l包含在前一個下降沿時鐘輸入的數據,dataout_h包含在當前上升沿時鐘輸出的數據。圖6顯示了ALTDDIO_IN函數的框圖。

圖6:ALTDDIO_IN的ALTDDIO_RX實例框圖

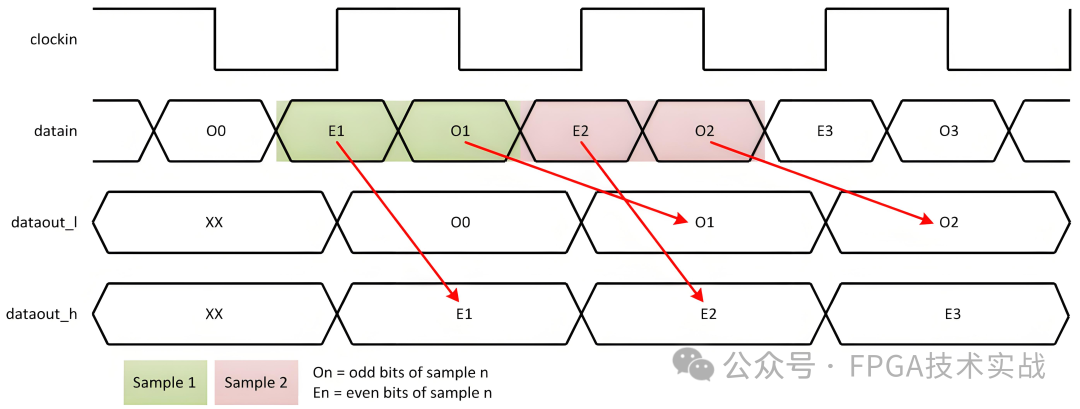

ADS4249的奇數位和偶數位的ALTDDIO_IN函數的默認時序圖如圖7所示。該時序圖假設ADS4249和ALTDDIO_IN函數之間的時鐘沒有相移。該時序圖顯示,在輸入時鐘的上升沿,輸出dataout_l具有前一個樣本(樣本N-1)的奇數位,輸出dataout_h具有當前樣本(樣本N)的偶數位。這意味著每個時鐘周期函數輸出端的奇數位和偶數位不是來自同一ADC樣本。當試圖將DDR數據編譯成單個樣本進行處理時,這會產生問題。問題如圖7所示。

圖7:ALTDDIO_IN默認時序圖

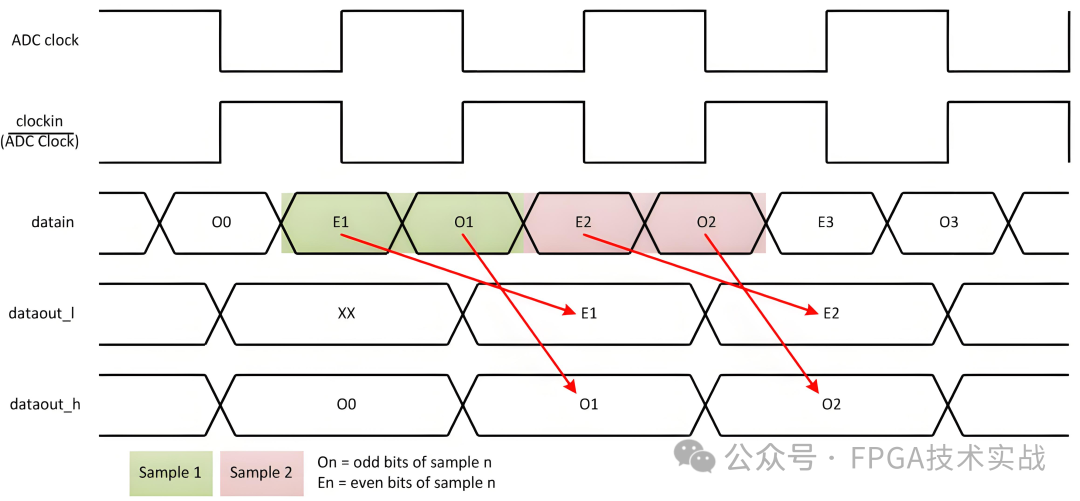

有兩種方法可以解決這個問題:第一種方法是通過在PLL中應用180°相移來反轉輸入時鐘。反相輸入時鐘的時序圖如圖8所示。新的圖表顯示,同一樣本的偶數位和奇數位在輸入時鐘的上升沿上時鐘輸出,偶數位在dataout_l上,奇數位在dataout_h上。請注意,偶數位和奇數位交換了之前默認情況下的輸出,這是示例代碼中使用的方法。

圖8:交換差分時鐘對的ALTDDIO_IN時序圖

請注意,示例代碼中的PLL實現沒有如上所述的180°相移。這種相移實際上是在FPGA外部完成的,通過物理交換電路板上布局上的差分走線P和N,使ADC的正出到達FPGA的負輸入。交換差分走線與反轉信號(或應用180°相移)相同,因此進入FPGA的時鐘已經反轉。因此,FPGA中的0°相移足以為ALTDDIO_in函數提供反相時鐘。如果沒有物理反轉,PLL需要執行相移。

第二種選擇是將dataout_h上的偶數位從上一個采樣延遲一個時鐘周期。這可以通過創建一個寄存器來輕松實現,該寄存器在SDR時鐘的上升沿上對偶數位進行計時。一旦偶數位延遲了一個時鐘周期,匹配的奇數位將在SDR時鐘的下一個上升沿從ALTDDIO_IN塊中出來。然后,這些可以組合在一起形成一個ADC樣本。

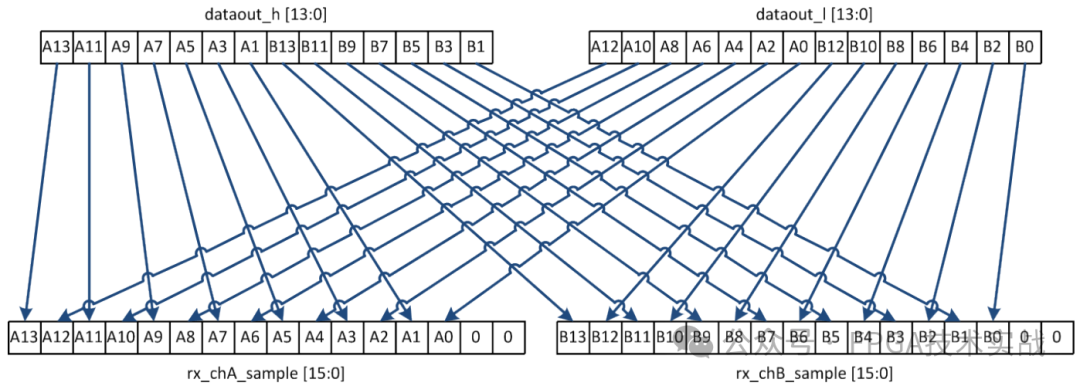

圖9:ALTDDIO_IN函數外ADC位的排列和重新排序

ADS4249使用兩條7位數據總線,每條總線包含一個ADC通道,該通道的偶數位和奇數位交織在一起,因此它們分別在數據時鐘的上升沿和下降沿輸出。示例代碼使用具有14個LVDS輸入對的單個ALTDDIO_IN函數,使得dataout_l和dataout_h每個都包含來自信道A的7位和來自信道B的7位,從而在每個時鐘上升沿上從ALTDDIO_IN函數輸出總共28位。圖9顯示了反轉時鐘情況下這些位的排列。對于信號處理,這些比特需要重新排列為通道A和B的單獨14比特樣本。使用簡單的賦值語句將它們按正確的順序排列。賦值語句的功能如圖9所示。請注意,ADS4249為14位,而DAC3482為16位。在每個14位樣本的末尾填充兩個零,因此使用DAC的14個最高有效位。如果使用延遲方法,偶數位和奇數位將分別位于dataout_h和dataout_l上。

2.2.2 DAC數據輸出架構

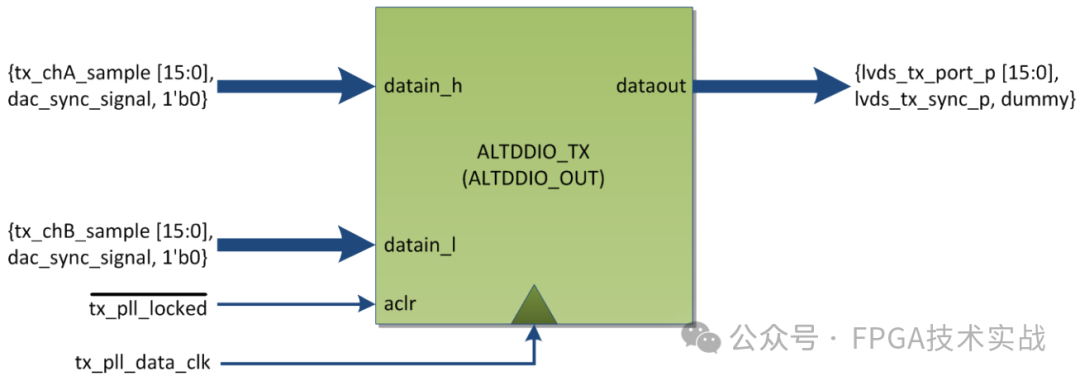

對于DAC,使用了兩個ALTDDIO_OUT 函數。其中一個實例簡單地輸出數據和同步信號,另一個實例創建DDR輸出時鐘。數據輸出ALTDDIO_OUT函數的框圖如圖10所示。

圖10:ALTDDIO_OUT的ALTDDIO_TX實例框圖

datain_h端口接收DAC通道A的采樣,datain_l接收通道B的采樣,使得通道A在時鐘的上升沿輸出,通道B在下降沿輸出。這些樣本來自分隔RX和TX時鐘域的FIFO。DAC同步信號有一個額外的輸入,該信號是通過用去抖動碼推送PUSHBUTTON1生成的,以防止多個同步實例。請注意,最后一個輸入位是零,這是必要的,因為不允許使用17位ALTDDIO_OUT函數。因此,創建了一個18位函數,并使用虛擬位來允許代碼編譯。

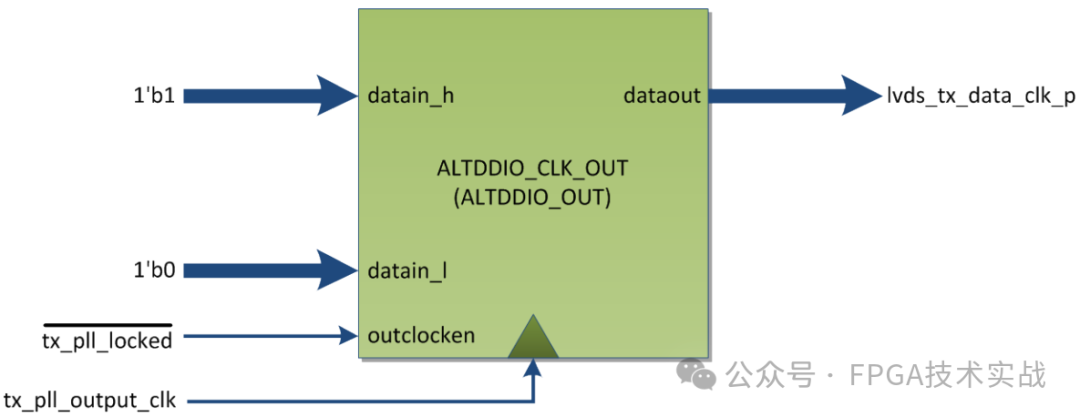

還有一個ALTDDIO_OUT實例,它生成圖11所示的輸出時鐘。ALTDDIO_CLK_OUT僅接收分別在tx_pll_output_CLK的上升沿和下降沿輸出的1和0。該塊的輸出成為傳輸到DAC的數據的數據時鐘。請注意,此塊的時鐘是與數據時鐘相比具有90°相移的PLL時鐘。這將根據DAC的要求創建一個中心對齊的源同步接口。

圖11:ALTDDIO_OUT的ALTDDIO_CLK_OUT實例的框圖

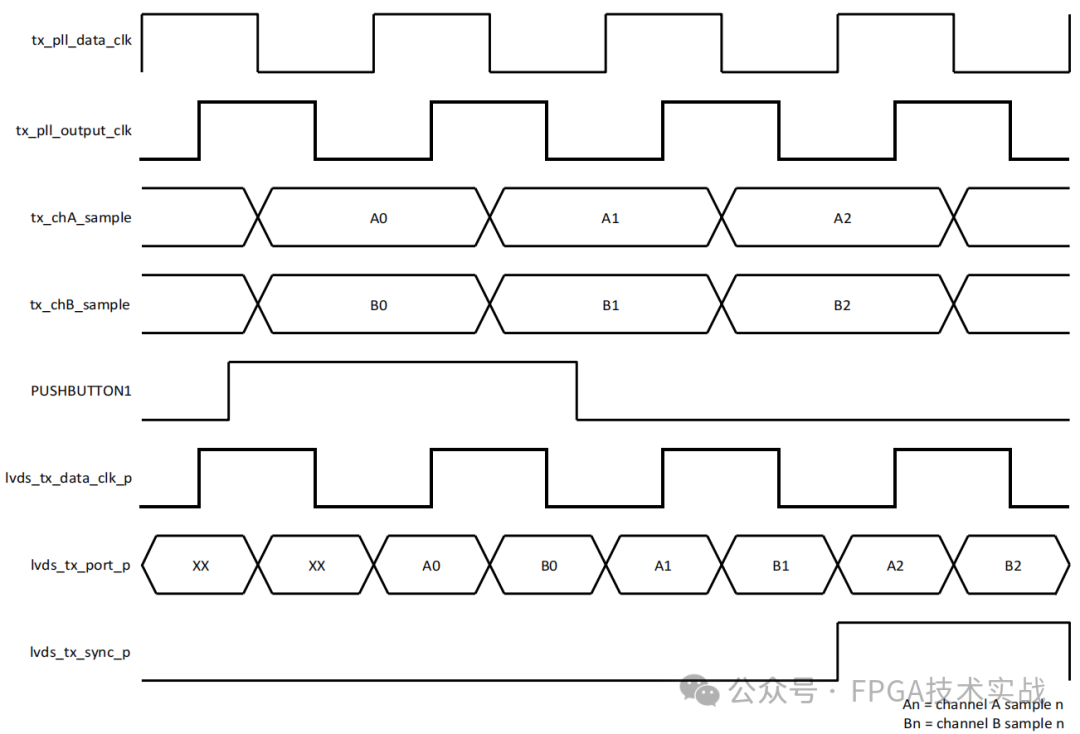

這兩個塊的時序圖如圖12所示,表明tx_pll_output_clk與tx_pll_data_clk相比有90°的相移。數據在tx_pll_data_clk上計時,輸出時鐘由tx_pll_output_clk創建。在圖的底部,很明顯,數據和輸出時鐘形成了一個中心對齊的源同步輸出。輸出時鐘是使用ALTDDIO_OUT塊創建的,而不是直接使用PLL時鐘,因為DDR輸出塊與輸出引腳的延遲比DDR輸出塊的全局時鐘網絡更匹配。這簡化了定時關閉。

圖12:ALTDDIO_TX和ALTDDIO_CLK_OUT的時序圖

2.3 LVDS接口時鐘約束設計

2.3.1 概述

時序約束的目的是描述與FPGA接口的外部設備的數據時鐘偏差。這些約束為代碼綜合提供了FPGA內部時序的有效時鐘到數據偏斜目標。最重要的是要記住,它是正在定義的外部接口。本節僅討論ADC和DAC源同步接口的時序約束。

對于向FPGA傳輸數據的設備,如ADC,時序約束定義了數據和數據時鐘之間可能存在的偏斜變化量。首先定義鎖存和啟動時鐘,其中啟動時鐘表示數據轉換沿,鎖存時鐘表示數據時鐘。時鐘定義設定了數據和時鐘之間的初始理想定時。然后,定義最小和最大延遲,表示數據線的最大可能延遲變化。這些延遲基本上指定了鎖存時鐘周圍的有效數據窗口。

對于從FPGA接收數據的設備,如DAC,時序約束定義了接收器在鎖存時鐘沿前后要求數據有效的最小時間,以便正確捕獲數據。它可以被認為是定義了接收設備的內部路徑可能引入的數據和時鐘之間的延遲范圍。延遲定義了FPGA必須保證數據在鎖存時鐘之前或之后到達的時間量,以滿足所有情況下的定時要求。同樣,首先定義時鐘以給出理想的起點,然后應用延遲來定義接收器捕獲有效數據所需的時間。

2.3.2定義時鐘

設置定時約束的第一步是為RX和TX域定義外部時鐘。對于RX時鐘域,實際FPGA輸入端口處存在的時鐘是ADC輸出的數據時鐘。該時鐘的定義如下面的SDC行所示。假設ADS4249以250MSPS的速度運行,并且時鐘應用于頂級verilog文件中定義的lvds_rx_clk_p輸入端口,則周期設置為4 ns。

create_clock-nameADC_DATA_CLK-period4.00[get_ports lvds_rx_clk_p]接下來,創建一個虛擬時鐘,為ADC輸出的數據定義理想的啟動時鐘。由于ADC是一個中心對齊的接口,因此啟動時鐘需要提前90°,以獲得正確的初始設置和保持時間。如下圖所示,波形參數分別定義了上升沿和下降沿位置,其中250 MHz時鐘的默認值為0 ns和2 ns。將時鐘提前90°相當于使上升沿提前1ns出現,因此-1ns的值應該有效,但是波形參數不能為負值。由于波形參數理解時鐘是周期性的,因此3ns和5ns的值將被理解為-1ns和1ns。

create_clock-name ADC_LAUNCH_CLK -period4.00-waveform {35}

接下來,ADC鎖存時鐘是從PLL輸出手動創建的,如下圖所示,而不是讓工具自動創建。這樣,名稱ADC_LATCH_CLK可以在其他語句中使用,而不是使用較長的自動生成的PLL時鐘名稱。這些時鐘定義必須位于下面提到的derive_pll_clocks語句之前。

create_generated_clock -name ADC_LATCH_CLK -source[get_pins {RX_PLL_inst|altpll_component|auto_generated|pll1|inclk[0]}] [get_pins {RX_PLL_inst|altpll_component|auto_generated|pll1|clk[0]}]添加下面的兩行會自動得出尚未定義的PLL時鐘,并計算時鐘不確定性。

derive_pll_clocks derive_clock_uncertainty

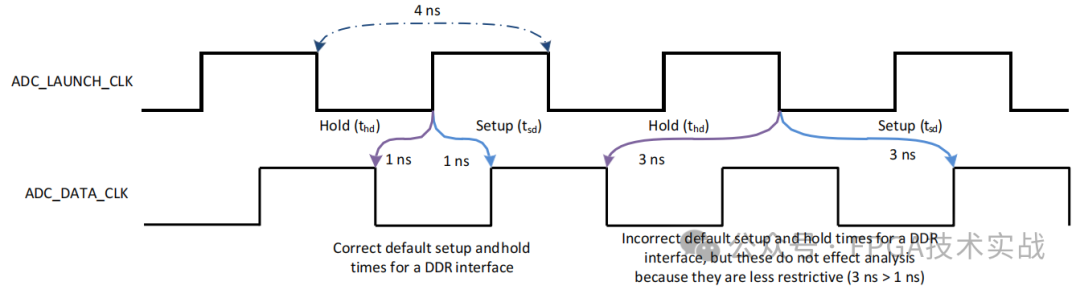

圖13顯示了上述時鐘的默認設置和保持時間。TimeQuest分析了四種可能的默認設置和保持時間:

?上升沿到上升沿

?上升沿到下降沿

?下降沿到上升沿

?下降沿到下降沿

圖13:帶有250 MHz時鐘的ADS4249的默認設置和保持時間

所需的默認設置時間應基于上升沿到上升沿和下降沿到下降沿。所需的默認保持時間應基于上升沿到下降沿和下降沿到上升沿。盡管TimeQuest分析了設置和保持的所有四種情況,但只有兩種最嚴格的情況用于限制時間。四種情況中的兩種如圖13所示。

使用圖13中所示的較短的設置和保持時間是因為它們比較長的設置和保留時間更具限制性。示例代碼中的SDC文件包含ADC鎖存器和啟動時鐘之間的set_false_path語句,該語句告訴TimeQuest忽略這些額外的設置和保持時間,這簡化了分析和定時報告,但它們不是正確分析所必需的。

對于TX側,首先需要添加DAC3482的輸入時鐘,如下所示。該時鐘應用于輸入端口lvds_tx_fpga_clk_p,并用作tx_PLL塊的輸入時鐘。

create_clock-nameTX_FPGA_CLK-period4.00[get_ports lvds_tx_fpga_clk_p]

接下來,DAC啟動時鐘是手動創建的,而不是通過derive_pll_clocks語句,允許使用更方便的時鐘名稱,如下所示。這樣,在其他語句中使用名稱DAC_LAUNCH_CLK來定義PLL輸出時鐘,而不是使用較長的自動生成名稱。這兩個時鐘定義必須位于前面提到的derive_pll_clocks語句之前。

create_generated_clock -name DAC_LAUNCH_CLK

-source[get_pins {TX_PLL_inst|altpll_component|auto_generated|pll1|inclk[0]}]

[get_pins {TX_PLL_inst|altpll_component|auto_generated|pll1|clk[0]}]

接下來,推導上述PLL時鐘和時鐘不確定性,然后定義DAC數據輸出時鐘,如下所示。以下語句定義了FPGA輸出端口的DAC數據時鐘。雖然該時鐘是由ALTDDIO_clock_OUT函數生成的,但時鐘的來源是90°相移PLL時鐘輸出。ALTDDIO_CLOCK_OUT輸出應用于端口lvds_tx_data_clk_p。

create_generated_clock-nameDAC_DATA_CLK

-source[get_pins {TX_PLL_inst|altpll_component|auto_generated|pll1|clk[1]}]

[get_ports lvds_tx_data_clk_p]

DAC_DATA_CLK和DAC_LAUNCH_CLK也有四種可能的默認設置和保持時間。同樣的論點也適用于這里,即只使用兩個最嚴格的設置和保持時間。為這些時鐘添加了set_false_path語句,以簡化分析和報告計時,但它們也是可選的。與ADS4249的情況一樣,TX側的默認設置和保持時間均為1ns,因為它是一個中心對齊的接口。

2.3.3 FPGA輸入時序約束

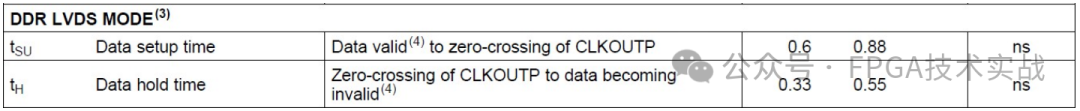

一旦創建了外部時鐘,就必須根據外部設備定義延遲。首先,在RX側,ADS4249的設置和保持時間需要從數據表中刪除。圖14中的摘錄取自ADS4249數據表中的時序要求表。ADC設置和保持時間參數定義了時鐘過零點周圍的數據有效窗口,并表示FPGA可用于滿足時序的時間窗口。數據設置時間表示數據有效的時鐘沿之前的時間,保持時間表示數據無效的時鐘沿之后的時間。左側顯示的每個參數的最小值是最有用的,因為它們在溫度范圍內有效,并考慮了位到位的偏斜。

圖14:ADS4249數據表中的時間要求

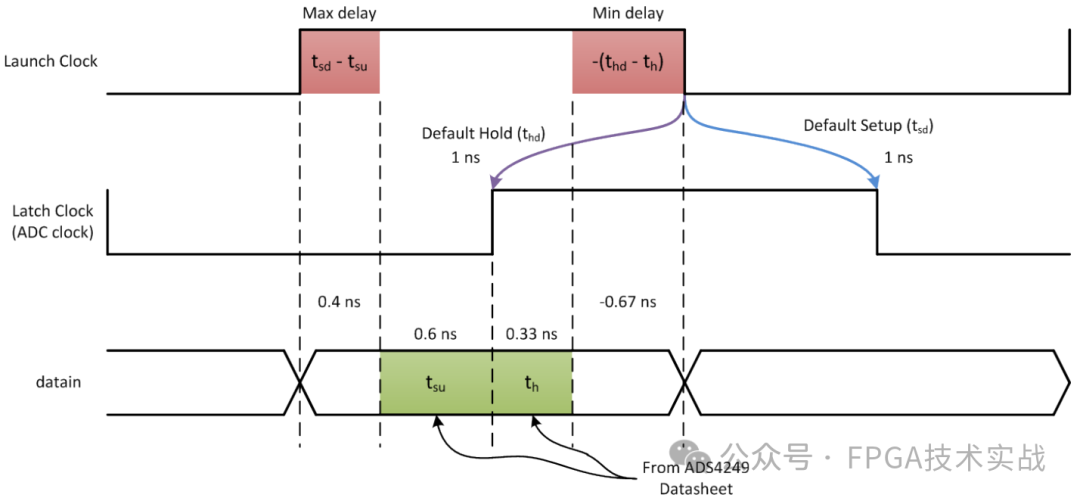

圖15提供了ADC設置和保持時間以及必須定義的輸入延遲的圖形視圖。在圖中,綠色塊表示FPGA允許在內部引入的總偏斜,紅色塊表示ADC可能在數據線上引入的最大和最小延遲。

圖15:SDC輸入時序約束圖

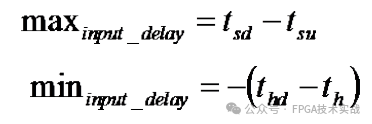

由于ADC建立和保持時間定義了數據時鐘周圍的數據有效窗口,因此很直觀的是,ADC以數據線上的延遲形式消耗了時鐘周期的其余部分。然后,SDC文件中定義的輸入定時延遲指定了ADC可能引入的數據延遲范圍。因此,最小和最大延遲被定義為下面的方程。方程式中使用的變量如圖15所示。

這些方程假設電路板上的數據和時鐘走線匹配良好。如果數據走線比時鐘走線長,則會減少設置時間并增加保持時間,因此最大延遲增加,最小延遲相應減少。如果時鐘走線比數據走線長,則會減少保持時間并增加設置時間,因此最小延遲增加(變得更負),最大延遲相應減少。

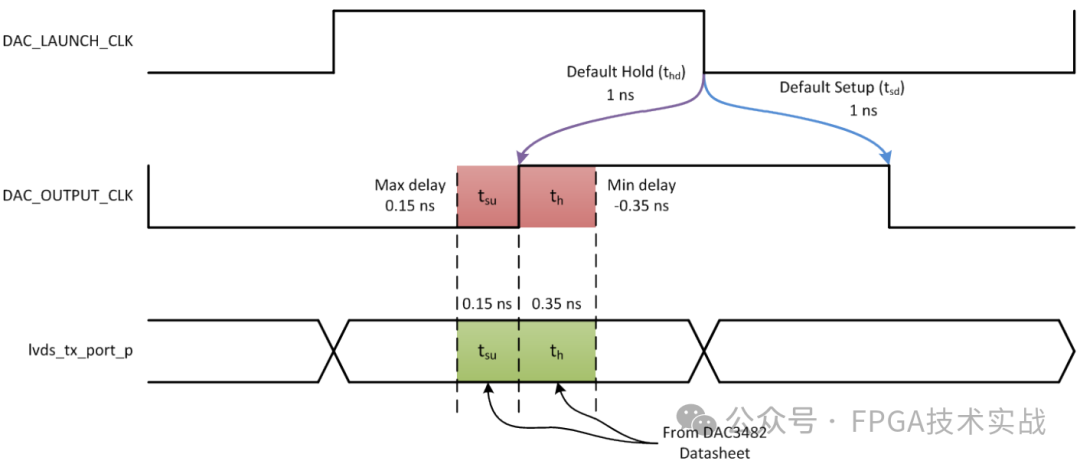

2.3.4 FPGA輸出時序約束

考慮輸出定時延遲的一種簡單方法是將其想象為在到達鎖存寄存器之前定義接收設備內部的數據延遲。這基本上說,延遲指定了接收器需要在鎖存時鐘周圍保持數據恒定的最小時間量,以便數據及時到達鎖存寄存器,以便時鐘成功捕獲數據。知道這一點,DAC的定時延遲非常直接。數據表中列出的DAC設置和保持時間分別指定了DAC在時鐘邊沿之前需要接收數據的時間量和DAC在時鐘沿之后需要數據保持恒定的時間。因此,很簡單,最大輸出延遲就是DAC的設置時間,最小輸出延遲是DAC保持時間的負值。如圖16所示。

圖16:SDC輸出時序約束圖

同樣,這些延遲只有在數據和時鐘線精確匹配的情況下才有效。如果走線之間存在不匹配,則需要考慮延遲。如果數據走線比時鐘走線長,則最大延遲增加,最小延遲相應減少。如果時鐘走線比數據走線長,則最大延遲減小,最小延遲增大。

2.3.5 時序收斂小技巧

如果設計師在時序收斂上遇到問題,可以嘗試一些簡單的方法。首先,RX和TX側的PLL可用于在FPGA內部引入相移,以增加設置或保持時間。通過在鎖存時鐘上添加延遲,默認設置時間增加,默認保持時間減少。在設置時間幾乎沒有松弛但保持時間有很多松弛的情況下,這應該有助于改善設置松弛。或者,可以向鎖存時鐘添加負相移,以增加保持松弛并減少設置松弛。同樣,TX PLL可以在0°啟動時鐘和90°鎖存時鐘之間增加或多或少的相位差,以改善DAC的設置和保持時間。

請注意,更改PLL時鐘相移不會影響SDC定時約束,因為只有內部定時發生了變化,而外部定時保持不變。請記住,SDC文件僅描述了外部接口時序。

這些設備通常具有更大的靈活性。例如,DAC3482允許在不同的建立和保持時間進行編程,有效地在數據時鐘周圍移動所需的數據窗口。這對于采樣率高于250MSPS的時序收斂可能特別有用。ADS4249具有類似的功能,其中上升和下降時鐘沿可以隨時間移動,但不如DAC3482廣泛。

3. ADC接口設計不使用PLL情況

當與許多設備連接時,很容易消耗FPGA的所有PLL。在這種情況下,最好避免將PLL用于接收設備。可以將時鐘引入FPGA,并直接在ALTDDIO_IN塊中使用。需要注意的是,FPGA內不再像使用具有源同步補償的PLL時那樣保持時鐘與數據的關系。因此,FPGA必須匹配時鐘和數據線之間的延遲,以滿足中心對齊接口的必要時序。這應該是可能的,因為FPGA I/O單元具有可調的數據延遲。如果時間約束設置正確,應該能夠匹配時鐘和數據走線之間的延遲。

如果無法滿足時序要求或滿足時序要求的結果很差,則可以使用ADS4249的時鐘偏移功能來移動與數據相比的時鐘沿,以放寬FPGA內部的匹配要求。如果這樣做,則需要更新時序約束以匹配ADC接口的新時序。

來源:本文轉載自FPGA技術實戰公眾號

-

FPGA

+關注

關注

1644文章

21989瀏覽量

615188 -

接口

+關注

關注

33文章

8967瀏覽量

153343 -

adc

+關注

關注

99文章

6658瀏覽量

548502 -

Altera

+關注

關注

37文章

803瀏覽量

155630 -

lvds

+關注

關注

2文章

1119瀏覽量

67201

原文標題:Altera FPGA與高速ADS4249和DAC3482的LVDS接口設計

文章出處:【微信號:FPGA研究院,微信公眾號:FPGA研究院】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

T使用tsw1400evm搭配ads4249來采集模擬數據,如何自己向tsw1400evm燒錄程序呢?

DAC3482存在雜散怎么解決?

DAC3482最小數據輸入速率是為什么是125MSPS?

DAC3482從時鐘發生器出來的FIFO_OSTR信號連入時鐘緩沖器CDCP1803后才輸出到DA中,時鐘緩沖器起什么作用?

DAC3482內部的FIFO作用是什么?

使用DAC3482 fifo同步失敗的原因?怎么處理?

EVM DAC3482無法配置是什么原因導致的?

DAC3482輸出正弦波形出現如下失真和抖動情況,怎么解決?

dac3482寄存器報警始終提示dataclk沒有

dac3482寄存器報警始終提示dataclk沒有,為什么?

在DAC3482中,采用片內混頻器實現上變頻功能需要保證兩路輸入信號的正交性嗎?

雙通道,16位,1.25GSPS數模轉換器DAC3482的詳細資料概述

Altera FPGA和TI的ADS4249和DAC382之間的接口的詳細闡明(免費下載)

ADS4249雙通道、14位、250MSPS超低功耗ADC數據表

DAC3482雙通道、16位、1.25GSPS數模轉換器(DAC)數據表

Altera FPGA與高速ADS4249和DAC3482的LVDS接口設計

Altera FPGA與高速ADS4249和DAC3482的LVDS接口設計

評論