硬件乘法器是現(xiàn)代計算機(jī)中必不可少的一部分,其基礎(chǔ)是加法器結(jié)構(gòu)。

硬件乘法器,其基礎(chǔ)就是加法器結(jié)構(gòu),它已經(jīng)是現(xiàn)代計算機(jī)中必不可少的一部分。[1]乘法器的模型就是基于“移位和相加”的算法。在該算法中,乘法器中每一個比特位都會產(chǎn)生一個局部乘積。第一個局部乘積由乘法器的LSB產(chǎn)生,第二個乘積由乘法器的第二位產(chǎn)生,以此類推。如果相應(yīng)的乘數(shù)比特位是1,那么局部乘積就是被乘數(shù)的值,如果相應(yīng)的乘數(shù)比特位是0,那么局部乘積全為0。每次局部乘積都向左移動一位。

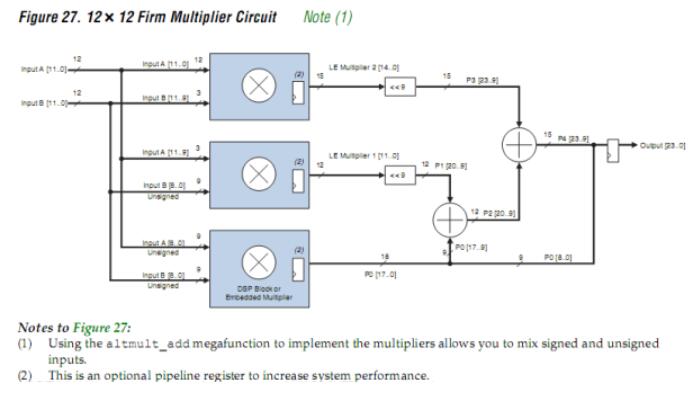

乘法器可以用更普遍的方式來表示。每個輸入,局部乘積數(shù),以及結(jié)果都被賦予了一個邏輯名稱(如A1、A2、B1、B2),而這些名稱在電路原理圖中就作為了信號名稱。在原理圖的乘法例子中比較信號名稱,就可以找到乘法電路的行為特性。

在乘法器電路中,乘數(shù)中的每一位都要和被乘數(shù)的每一位相與,并產(chǎn)生其相應(yīng)的乘積位。這些局部乘積要饋入到全加器的陣列中(合適的時候也可以用半加器),同時加法器向左移位并表示出乘法結(jié)果。最后得到的乘積項在CLA電路中相加。注意,某些全加器電路會將信號帶入到進(jìn)位輸入端(用于替代鄰近位的進(jìn)位)。這就是一種全加器電路的應(yīng)用;全加器將其輸入端的任何三個比特相加。

隨著乘數(shù)和被乘數(shù)位數(shù)的增加,乘法器電路中的加法器位樹也要相應(yīng)的增加。通過研究CLA電路的特性,也可以在乘法器中開發(fā)出更快的加法陣列。

電路結(jié)構(gòu)

從理論上講,兩個二進(jìn)制N位操作數(shù)相乘,乘積的總寬度為2N,因此需要一個寬度為2N的移位寄存器和加法器。但在實際執(zhí)行過程中,一是每個部分積的寬度和移位相加的有效寬度都為N位,從資源的利用率角度考慮,僅需N位寬度的加法器即可;二是按照先移位再相加的原理,兩個N位操作數(shù)則需要2N個時鐘周期才能完成整個運算,在此考慮將移位和相加兩個運算步驟合并,從速度上就可在N個時鐘周期內(nèi)完成。

根據(jù)上述分析,8位移位相加型硬件乘法器應(yīng)包括16位鎖存器、8位移位寄存器、8位乘法器、8位加法器等4個組成部分。具體電路結(jié)構(gòu)如圖1所示。

鎖存器發(fā)揮著鎖存的作用,用于鎖存部分和。

移位寄存器則具備移位作用,當(dāng)加載信號有效時乘數(shù)將加載于8位右位寄存器,隨著時鐘上升沿的到來,乘數(shù)即由低位開始逐位移出。

乘法器功能類似一個特殊的與門。有兩個輸入端口,一個端口用于輸入8位并行操作數(shù)(被乘數(shù)),另一個端口在時鐘信號控制下輸入由移位寄存逐步移出的串行操作數(shù),并將這兩個操作數(shù)進(jìn)行與運算。

加法器用于將本次時鐘脈沖控制下得到的8位部分積與鎖存于鎖存器高8位的前一個時鐘脈沖下得到的部分和相加。

-

硬件乘法器

+關(guān)注

關(guān)注

0文章

5瀏覽量

2663

原文標(biāo)題:硬件乘法器

文章出處:【微信號:ALIFPGA,微信公眾號:FPGA極客空間】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

查表式硬件乘法器

AVR的硬件乘法器8X8的嗎?

硬件乘法器的相關(guān)資料分享

MSP430F5系列16位超低功耗單片機(jī)模塊原理10

MSP430教程Chapt12-硬件乘法器

硬件乘法器原理_硬件乘法器電路結(jié)構(gòu)

加法器結(jié)構(gòu)和硬件乘法器的基礎(chǔ)使用工程文件免費下載

MSP430X1XX系列硬件乘法器,比較器,flash講解

硬件乘法器是什么?

硬件乘法器是什么?

評論