文章來源:半導體與物理

原文作者:jjfly686

本文簡單介紹了體硅FinFET和SOI FinFET之間的結(jié)構(gòu)差異與工藝差異。

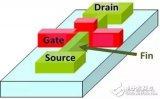

在半導體制造領(lǐng)域,晶體管結(jié)構(gòu)的選擇如同建筑中的地基設(shè)計,直接決定了芯片的性能上限與能效邊界。當制程節(jié)點推進到22nm以下時,傳統(tǒng)平面晶體管已無法滿足需求,鰭式場效應(yīng)晶體管(FinFET) 以其三維立體結(jié)構(gòu)成為行業(yè)主流。然而在FinFET陣營內(nèi)部,一場關(guān)于“地基材料”的技術(shù)路線競爭悄然展開——這便是Bulk Silicon(體硅) 與SOI(絕緣體上硅) 兩大技術(shù)的對決。這場對決不僅關(guān)乎性能極限的突破,更牽動著芯片成本與可靠性的微妙平衡,成為半導體行業(yè)持續(xù)演進的關(guān)鍵戰(zhàn)場。

結(jié)構(gòu)差異:從物理基礎(chǔ)看技術(shù)分野

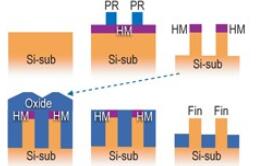

Bulk Silicon FinFET:深槽隔離的工程杰作

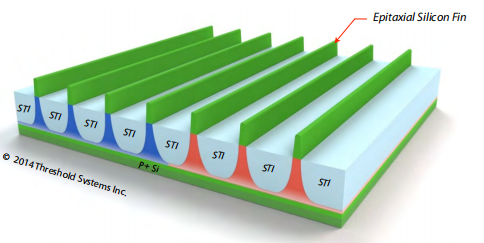

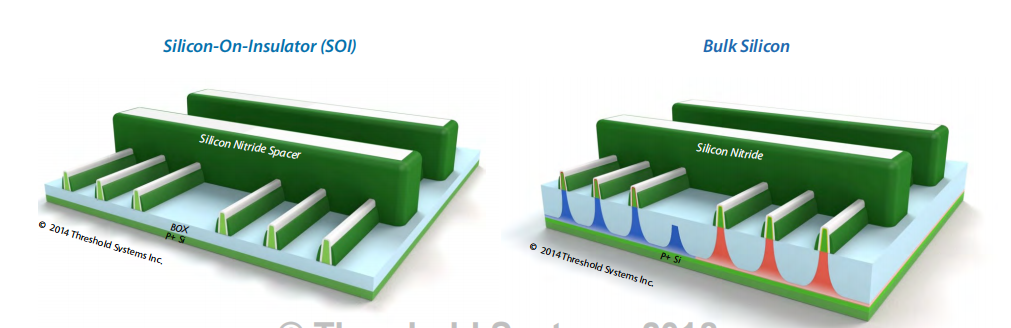

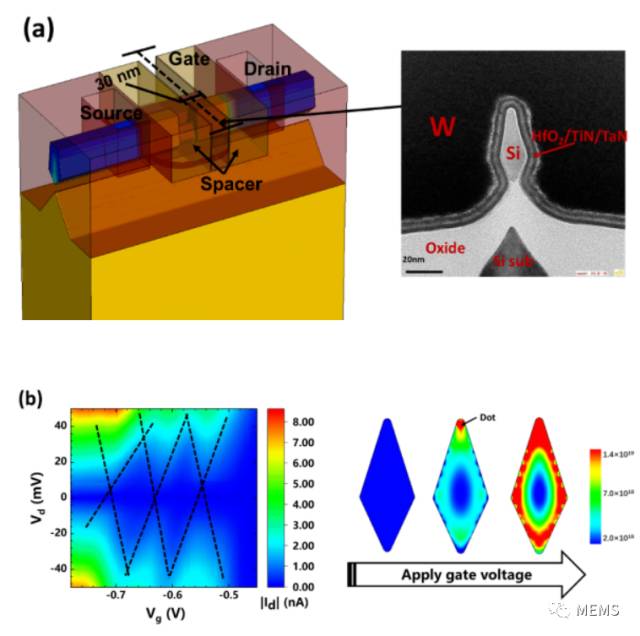

Bulk Silicon FinFET基于常規(guī)硅晶圓制造,其核心挑戰(zhàn)在于如何在導電的硅襯底上實現(xiàn)相鄰晶體管間的有效隔離。為實現(xiàn)這一目標,工程師們開發(fā)了淺溝槽隔離(STI) 技術(shù):通過等離子刻蝕在硅襯底上挖出深達數(shù)百納米的溝槽;填充二氧化硅(SiO?) 或氮化硅(Si?N?) 作為絕緣材料;在隔離區(qū)域之間形成垂直硅鰭(典型高度30-50nm,寬度5-10nm);柵極從三面包裹硅鰭,增強溝道控制能力。

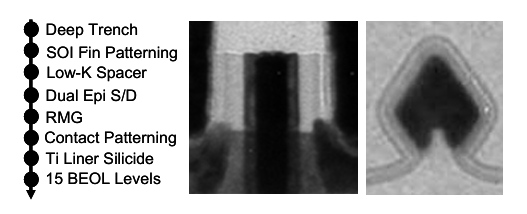

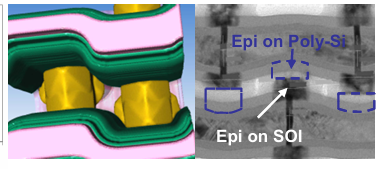

這一結(jié)構(gòu)的復雜性在截面圖中顯露無遺:硅鰭底部與襯底直接相連,需要通過精密摻雜在鰭基形成隔離層,防止漏電流向襯底擴散。隨著鰭高度的增加,摻雜均勻性控制成為難點,可能引發(fā)隨機摻雜漲落(RDF) 導致的閾值電壓波動。

SOI FinFET:天然絕緣的優(yōu)雅設(shè)計

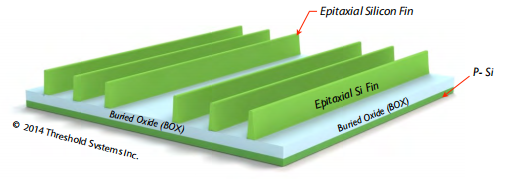

SOI FinFET則構(gòu)建在特殊的三層晶圓上:頂層硅(~10nm):用于刻蝕形成晶體管鰭片;埋氧層(BOX)(~25nm):二氧化硅絕緣層,隔絕襯底;基底硅:僅起機械支撐作用。

這種結(jié)構(gòu)帶來了革命性簡化:無需STI刻蝕:埋氧層自然隔離相鄰器件;消除鰭基摻雜:BOX層阻擋垂直漏電路徑;硅鰭全耗盡:超薄頂層硅確保柵極完全控制溝道。

從電子顯微鏡圖像可見,SOI FinFET的硅鰭如精致的雕塑般矗立在光滑的氧化層上,與Bulk Silicon中復雜的隔離結(jié)構(gòu)形成鮮明對比。

| 襯底材料 | 單層硅晶圓 | 硅/二氧化硅/硅復合晶圓 |

| 隔離方式 | 淺溝槽隔離(STI) | 埋氧層(BOX)天然隔離 |

| 硅鰭連接 | 與襯底直接相連 | 通過BOX層與襯底絕緣 |

| 鰭高 | 30-50nm | 20-40nm |

| 關(guān)鍵摻雜區(qū) | 鰭基防漏電摻雜層 | 無需特殊摻雜 |

| 特性 | Bulk Silicon FinFET | SOI FinFET |

|---|

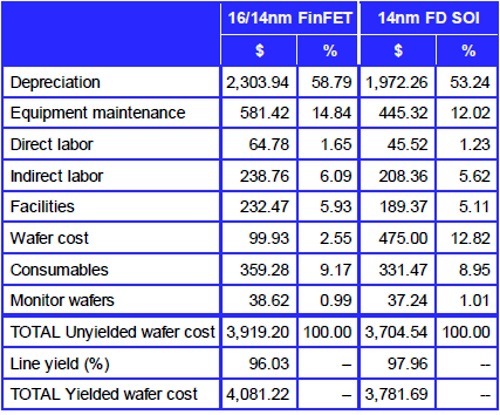

工藝復雜度:從制造流程看成本控制

Bulk Silicon FinFET:繁瑣但成熟的前端工藝

Bulk Silicon FinFET的制造前端包含多個高精度步驟:

1、深槽刻蝕:反應(yīng)離子刻蝕(RIE)形成STI溝槽,深寬比達5:1以上;

2、隔離填充:原子層沉積(ALD)氮化硅+二氧化硅填充溝槽;

3、化學機械拋光(CMP):去除多余隔離材料,實現(xiàn)全局平坦化;

4、鰭基注入:傾斜離子注入形成P/N阱與防穿通摻雜層;

5、硅鰭刻蝕:多重曝光光刻+刻蝕定義鰭陣列;

這些步驟不僅增加5-7道光罩,更引入摻雜均勻性和刻蝕深寬比等控制難點。特別是鰭基注入環(huán)節(jié),需精確控制摻雜輪廓以平衡泄漏與性能,退火過程易導致雜質(zhì)擴散,影響閾值電壓穩(wěn)定性。

SOI FinFET:簡化的前端流程

SOI工藝大幅簡化前端制程:

跳過STI:BOX層已實現(xiàn)天然隔離,僅需定義有源區(qū)圖形;

省略鰭基注入:埋氧層阻斷漏電,無需復雜摻雜工程;

直接鰭刻蝕:在超薄頂層硅上一步形成全耗盡硅鰭;

這種簡化使SOI FinFET的前端工藝步驟減少約30%,顯著降低成本。

-

半導體

+關(guān)注

關(guān)注

335文章

28919瀏覽量

238188 -

晶體管

+關(guān)注

關(guān)注

77文章

10020瀏覽量

141754 -

FinFET

+關(guān)注

關(guān)注

12文章

257瀏覽量

91194

原文標題:FinFET技術(shù)

文章出處:【微信號:bdtdsj,微信公眾號:中科院半導體所】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

半導體廠商產(chǎn)能布局 FinFET與FD-SOI工藝大PK

幫你看懂已經(jīng)全面攻占iPhone的FinFET

判斷FinFET、FD-SOI與平面半導體制程的市場版圖還早

詳解先進的半導體工藝之FinFET

FD-SOI(全耗盡型絕緣層上硅)

請問FinFET在系統(tǒng)級意味著什么?

請問一下finfet都用什么PR工具?

SOI和體硅集成電路工藝平臺互補問題的探討

FD-SOI元件與FinFET接近實用化的不斷發(fā)布

什么是FinFET?FinFET的工作原理是什么?

FD SOI生態(tài)系統(tǒng)逐步完善 與FinFET勢均力敵

FinFET到了歷史的盡頭?

基于主流的體硅高κ/金屬柵FinFET工藝,提出了一種利用拐角效應(yīng)

體硅FinFET和SOI FinFET的差異

體硅FinFET和SOI FinFET的差異

評論