內核SPI Slave軟件簡介

SPI主從之間傳輸通常遵循特定協議,如SPI Nor 兼容 JEDEC SDFP 協議,瑞芯微RK SPI slave 作為設備端傳輸也應遵循特定的協議,由于協議無范式,所以RK提供自定義的傳輸協議和設備驅動以供客戶參考。

Linux SPI slave驅動框架限制:使用傳輸隊列,雖然隊列喚醒后的線程優先級較高,但受調度影響不能完全保證實時性。

瑞芯微RK SPI slavemode限制:每次傳輸需重新發起SPI控制器配置,因此為確保SPImaster能夠獲知RK SPI slave完成傳輸配置從而發起數據傳輸,RKSPIslave端需增加side-band信號做ready狀態位。

本文基于

觸覺智能RK3506星閃開發板

演示SPI Slave從設備開發,其配套RK3506核心板(3核A7+M0多核異構),100%全國產,峰值功耗低至0.65W。

瑞芯微RK SPI slave 傳輸協議

- RK SPI Slave 傳輸基本流程

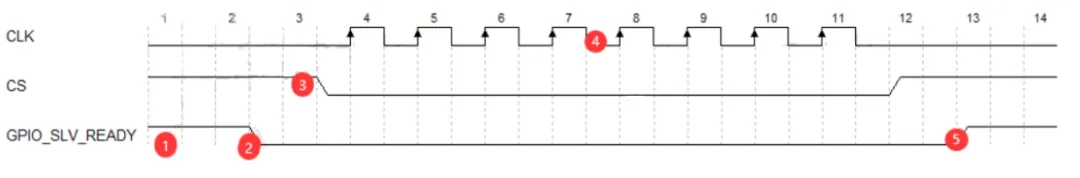

數據傳輸要求指定ready-gpios來通知SPI master分為5個部分:

(1)Slave 主動發起 spi_syncstep(2)Slave ready,使能 GPIO_SlV_READY 信號(3)master 確認 Slave ready 后發起傳輸(4)Slave 接收來自 master 發出的足夠的 clk 后完成傳輸(5)Slave idle,釋放 GPIO_SlV_READY 信號

、

- 定義兩種包類型

包括ctrl packet:2B cmd,2B addr(RK slave 定義的 application buffer 偏移地址),4B data(通常用于指定之后 data 包的傳輸長度)和data packet。

- 定義兩種傳輸類型

ctrl 傳輸(僅包含 1 ctrl packet),以及data 傳輸(包含1 ctrl packet 和 1 data packet 的兩筆 SPI 傳輸)。

- spidev_rkslv 支持 SPI_OBJ_APP_RAM_SIZE 長度的 application buffer 用于緩存傳輸數據,SPI master發起的 data 傳輸 1 ctrl packet 2B addr 指向該緩存偏移地址

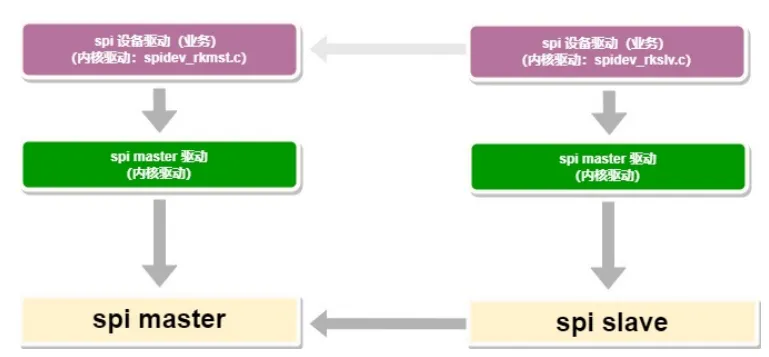

- 設備驅動

驅動源碼:

drivers/spi/spidev-rkslv.c drivers/spi/spidev-rkmst.c

源碼簡介:

static int spidev_rkslv_ctrl_receiver_thread(void *p) //建立線 程,線程內重復發起傳輸 { while (1) spidev_rkslv_xfer(spidev); drivers/spi/spidev-rkmst.c: 實現業務 } static int spidev_rkslv_xfer(struct spidev_rkslv_data *spidev) //傳輸入口 { spidev_slv_read(spidev, spidev->ctrlbuf, SPI_OBJ_CTRL_MSG_SIZE); //1 ctrl packet,獲取并解析傳輸類型 switch (ctrl->cmd) { //1 data packet,根據傳輸類型,定義 data packet 并完成收發 case SPI_OBJ_CTRL_CMD_INIT: /* to-do */ case SPI_OBJ_CTRL_CMD_READ: /* to-do */ case SPI_OBJ_CTRL_CMD_WRITE: /* to-do */ case SPI_OBJ_CTRL_CMD_DUPLEX: /* to-do */ } } static const struct file_operations spidev_rkslv_misc_fops = {} //注冊 misc device 測試接口

drivers/spi/spidev-rkmst.c說明:

static int spidev_rkmst_xfer(struct spidev_rkmst_data *spidev, void *tx, void *rx, u16 addr, u32 len) //傳輸入口 { spidev_rkmst_ctrl(spidev, cmd, addr, len); //1 ctrl packet,定義傳輸類型 switch (cmd) { //1 data packet,根據傳輸類型,定義 data packet 并完成收發 case SPI_OBJ_CTRL_CMD_READ: /* to-do */ case SPI_OBJ_CTRL_CMD_WRITE: /* to-do */ case SPI_OBJ_CTRL_CMD_DUPLEX: /* to-do */ } } static const struct file_operations spidev_rkmst_misc_fops = {} //注冊 misc device 測試接口

- 業務實現形式

SPI Slave 測試設備配置

- SPI master 發起單包數據傳輸測 :

echocmd addr length > /dev/spidev_rkmst_misc

說明:cmd :支持 read/write/duplex;addr:為對端 slave application buffer 偏移,單位 Bytes,僅支持 10 進制輸入;length:為 data packet 長度,單位 Bytes,僅支持 10 進制輸入;

實例如下:

echo write 128 128 > /dev/spidev_rkmst_misc echo read 128 128 > /dev/spidev_rkmst_misc echo duplex 128 128 > /dev/spidev_rkmst_misc

- SPI master 發起自動化測試 :

echoautotest length loops compare > /dev/spidev_rkmst_misc

說明:autotest:固定輸入,先測試全雙工數據傳輸,再測試讀寫數據傳輸,并輸出速率結果;測試默認使用對端 slave application buffer 偏移地址 0;

length:為 data packet 長度,單位 Bytes,僅支持 10 進制輸入;loops:設定壓測循環次數;

compare:1 - 開啟數據校驗;0 - 關閉數據校驗(支持特定場景,如持續輸出數據進行信號測試);

實例如下:

echoautotest1024641> /dev/spidev_rkmst_misc

- SPI master 發起自動化測試 :

echo appmem 0 256 > ./dev/spidev_rkslv_misc #打印 application buffer 數據 echo verbose 1 > ./dev/spidev_rkslv_misc #開啟傳輸傳輸過程 debug log,echo verbose 0 關閉打印

SPI Slave常見問題

- SPI 無信號

調試前確認驅動有跑起來;確保 SPI 4個引腳的IOMUX配置無誤;

確認TX 引腳有正常的波形,CLK有正常的 CLOCK 信號,CS信號有拉低;

如果clk頻率較高,可以考慮提高驅動強度來改善信號;

如何簡單判斷SPI DMA 是否使能,串口打印如無以下關鍵字,則DMA 使能成功:

[ 0.457137]Failedtorequest TX DMA channel [ 0.457237] Failed to request RX DMA channel

- 延時采樣時鐘配置方案

對于 SPI io 速率較高的情形,正常 SPI mode 可能依舊無法匹配外接器件輸出延時,RK SPI master read 可能無法采到有效數據,需要啟用 SPI rsd 邏輯來延遲采樣時鐘。

- SPI 傳輸方式說明

(1)默認傳輸模式

master mode 支持 IRQ、DMA 和 CPU 傳輸,slave mode 支持 IRQ 和 DMA 傳輸,默認都為 IRQ/DMA 組合傳輸方式:

當傳輸長度 < fifo 深度時,使用 IRQ 傳輸,默認使用 4.19 及以上內核版本的SOC,fifo 深度為64;

當傳輸長度 >= fifo 深度時,使用DMA傳輸;

(2)修改傳輸模式

master mode支持:

默認IRQ/DMA 組合傳輸方式;

參考 ”關閉 DMA 支持,僅支持 IRQ 傳輸;“ 說明,關閉 DMA,配置后僅支持IRQ 傳輸;

參考”rockchip,poll-only“ 說明,配置后僅支持CPU傳輸;

slave mode 不支持修改傳輸模式。

(3)IRQ傳輸特性

當數據 < fifo 深度時,一次傳觸發 1 個中斷,當數據 >= fifo 深度且使用 IRQ 傳輸時,fifo 水線設置為半 fifo,通常為 32 item,一次傳輸大致上觸發 items / 32 次中斷。

(4)DMA 傳輸特性

不觸發 spi 控制器中斷,使用 DMA 傳輸 finished call back 回調

- SPI 傳輸速率及 CPU 占用率高優化方向

通常 SPI 傳輸速率慢、IO 高負載下 CPU 占用率高的原因是因為:SPI 傳輸粒度小,且傳輸次數多,頻繁發起傳輸從而涉及較多的調度。建議優化方向:

1. 開啟 auto runtime,延時設置為 500ms,具體值以實測為準,修改點為 dts 節點添加rockchip,autosuspend-delay-ms 屬性;

2. 降低 CPU 負載:改用 IRQ 傳輸,相對 DMA 可能會有優勢,補丁參考 “改為 IRQ 傳輸” 小節;

3. 降低 CPU 負載:如為 DMA 傳輸,可修改 TX DMA 水線來降低 CPU 在 DMA 回調函數中等待 fifo傳輸完成的時間,補丁參考 “修改 SPI 水線。

-

瑞芯微

+關注

關注

25文章

560瀏覽量

52298 -

觸覺智能

+關注

關注

1文章

55瀏覽量

549 -

RK3506

+關注

關注

0文章

35瀏覽量

80

發布評論請先 登錄

【技術簡析】觸覺智能RK3506 Linux星閃網關開發板有什么奧妙?

瑞芯微RK3506開發板必備之LVGL應用開發手冊,深圳觸覺智能出品

米爾基于瑞芯微RK3506核心板開發板

瑞芯微RK3506開發板必備攻略之Qt應用開發手冊(下),觸覺智能工控嵌入式方案商

瑞芯微RK3506核心板/開發板SPI Slave從設備開發攻略

瑞芯微RK3506核心板/開發板SPI Slave從設備開發攻略

評論