1Versal IO介紹

1.1IO的劃分和分布

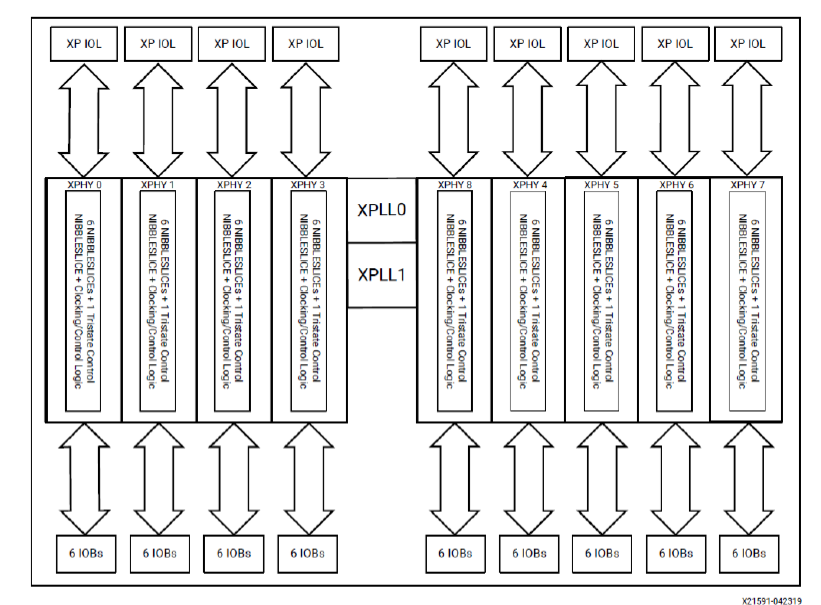

7nm Versal系列相對于16nm Ultrascale plus系列,IO做了升級,U+系列的HPIO在Versal升級為XPIO。Versal系列每一個XPIO bank包含54個IO管腳,其中包含9個nibbles,每個nibbles包含6個IO;每個bank包含2個XPLL、1個DPLL和1個MMCM時鐘資源。

1.2IO feature

XPIO支持0.6-1.5v電平,最高速率支持4.22gbps,支持3.2g mipi dphy,支持DDR4/Lpddr4硬核控制器,部分器件支持10g mipi cphy/DDR5/LPDDR5。

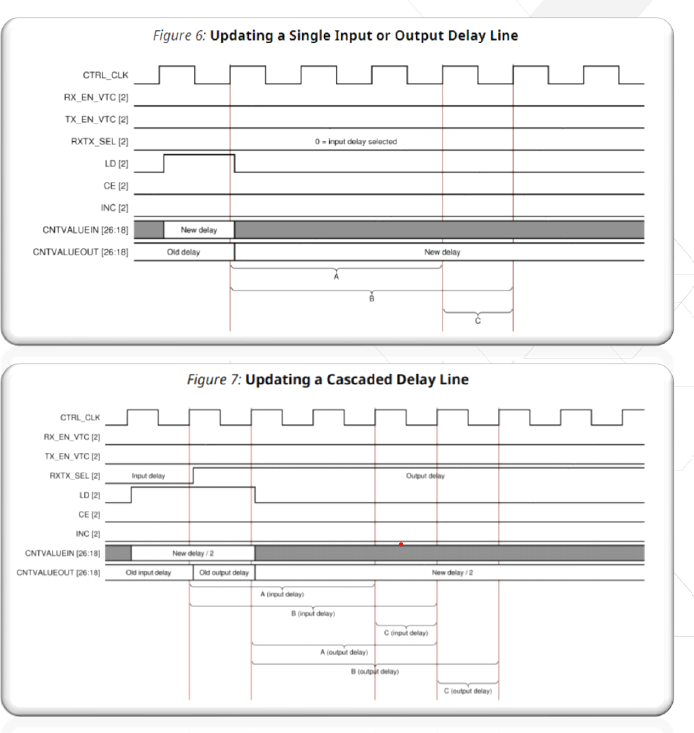

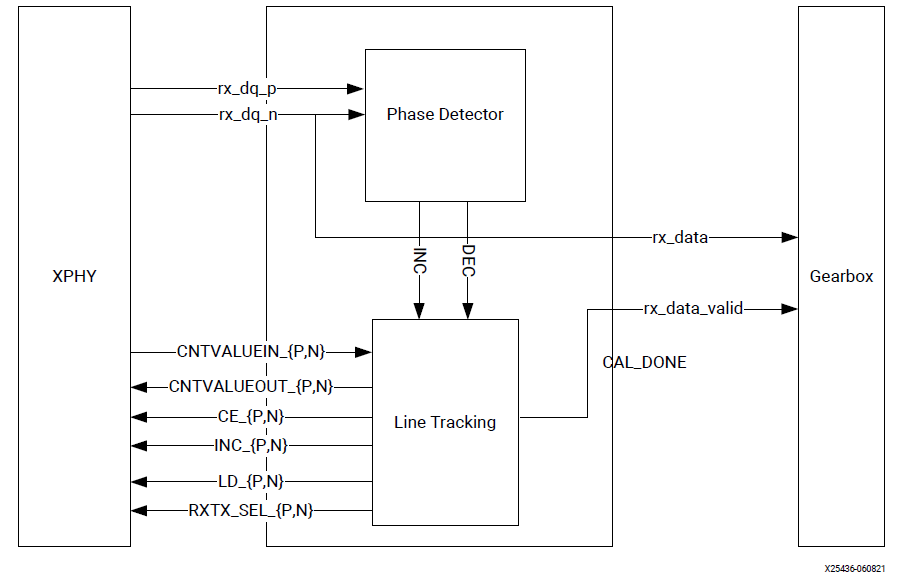

XPHY的IO delays 625 ps(512taps),tap精度約為1.22-4ps,級聯后io delay最高達到1250ps;Delay值通過下圖所示的XPHY接口完成更新,若需要獲取delay信息,建議在變化之后4個時鐘周期之后讀取更新的值,避開不穩定的狀態。

2與U+系列的差異

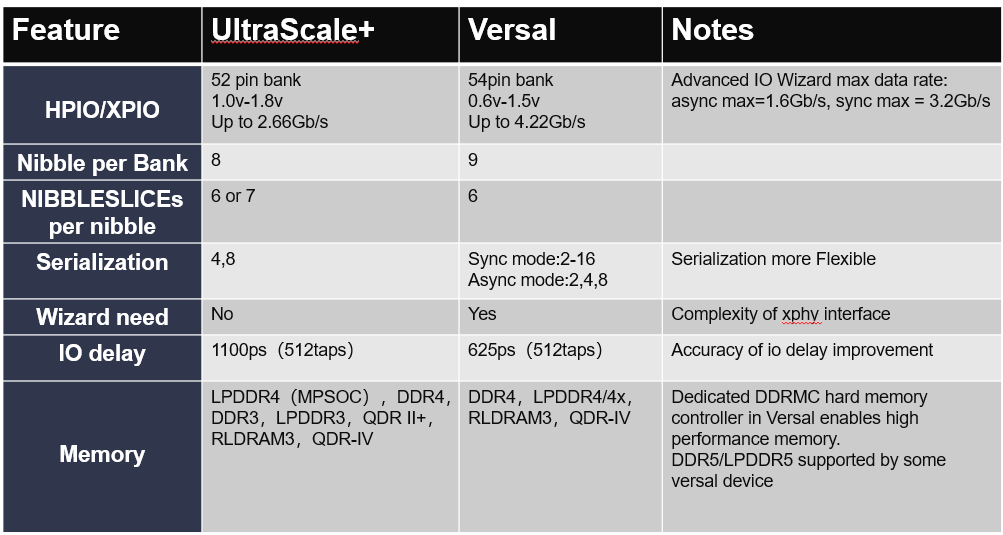

XPIO性能與U+系列select io相比有較大的提升,延遲精度,串化因子等方面都有明顯的改善和提升;二者對比如下圖所示:

除了IO性能的提升,其他主要的變化包括:

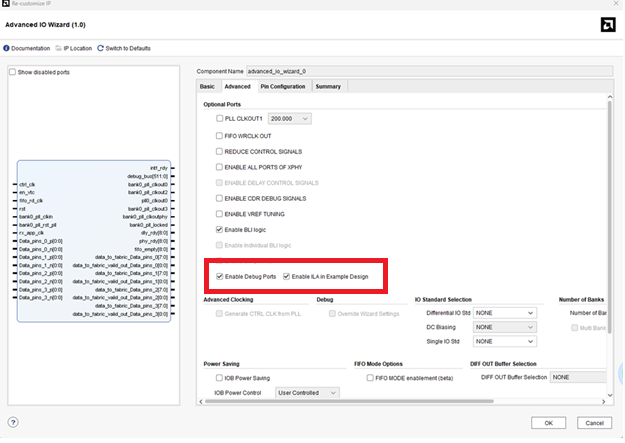

1. IP wizard由High speed SelectIo wizard改為advanced io wizard;

2. Versal系列不再支持hdl only 的設計方式for XPHY XPIO,因為XPHY互聯接口非常復雜,因此用戶需要基于advanced io wizard完成設計;

3. 支持同步和異步模式,同步模式下最高支持3.2g,異步模式下最高1.6g;

4. 建議通過advanced io planner自動分配io。

3異步模式的設計架構和運行機制

3.1異步模式的架構

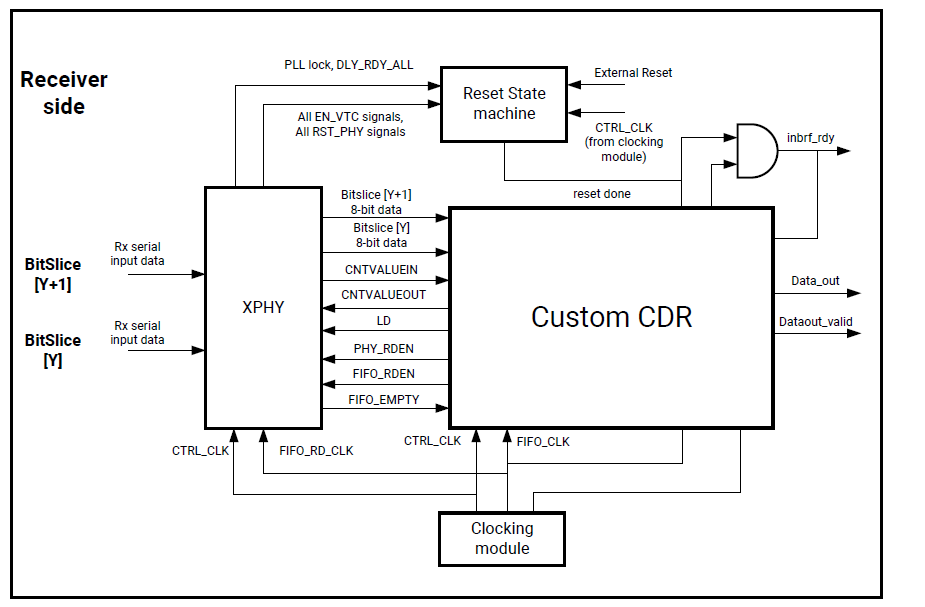

在異步模式下沒有隨路時鐘,需要通過CDR完成數據的恢復和采集。

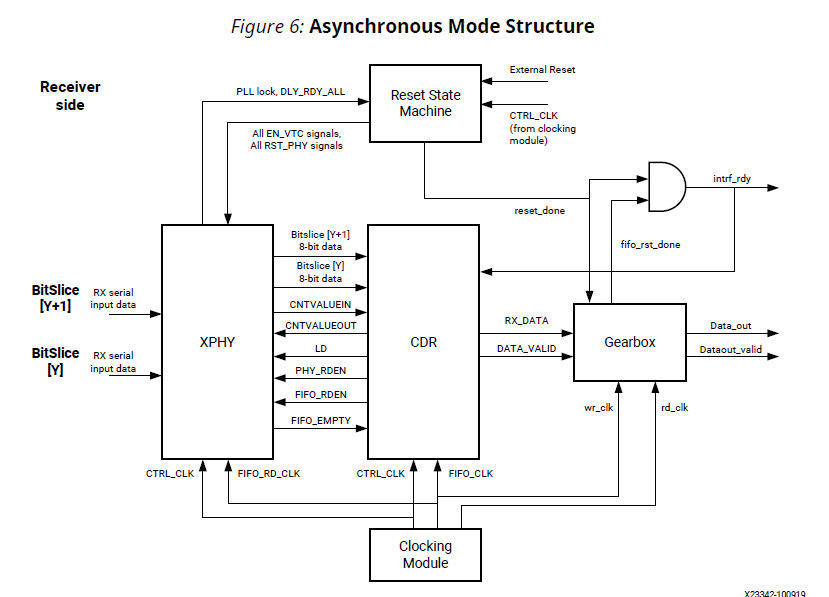

整體架構如下圖所示,數據經XPHY接入,在CDR模塊完成phase detector,delay line tracking,將找到的delay信息配置到XPHY,當delay不斷收斂,CDR模塊輸出RX_DATA和DATA_VALID給到下一級gearbox模塊,在gearbox完成位寬轉換并輸出有效數據data_out/data_valid。

IP支持兩種CDR模式的數據采集:CDR with ppm difference,CDR with Zero ppm;兩種模式下CDR的機制沒有大的差別,下文以CDR with ppm difference模式為例進行說明。

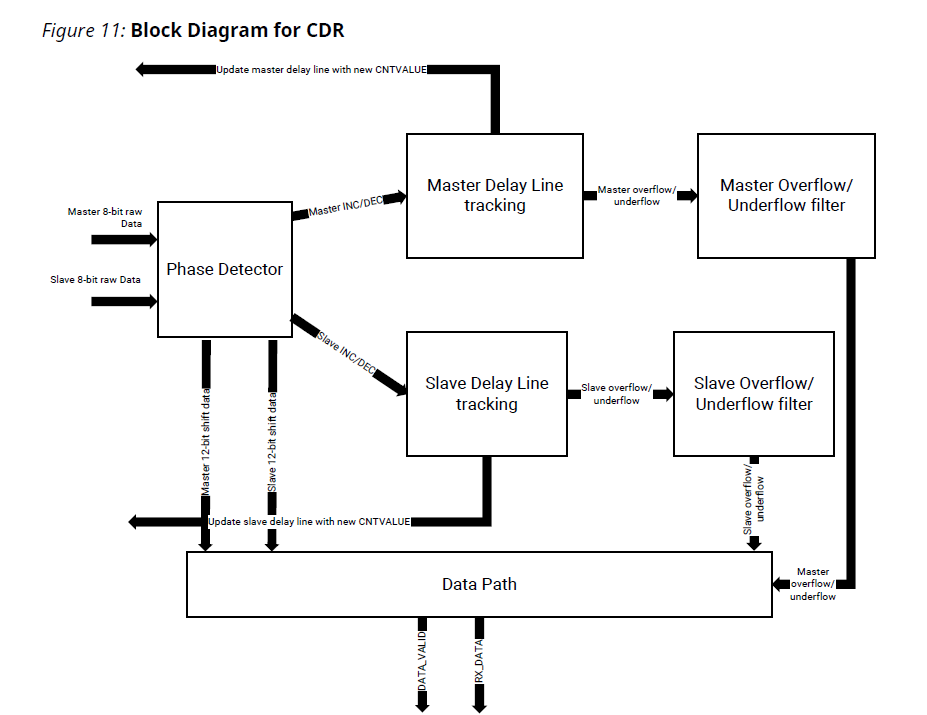

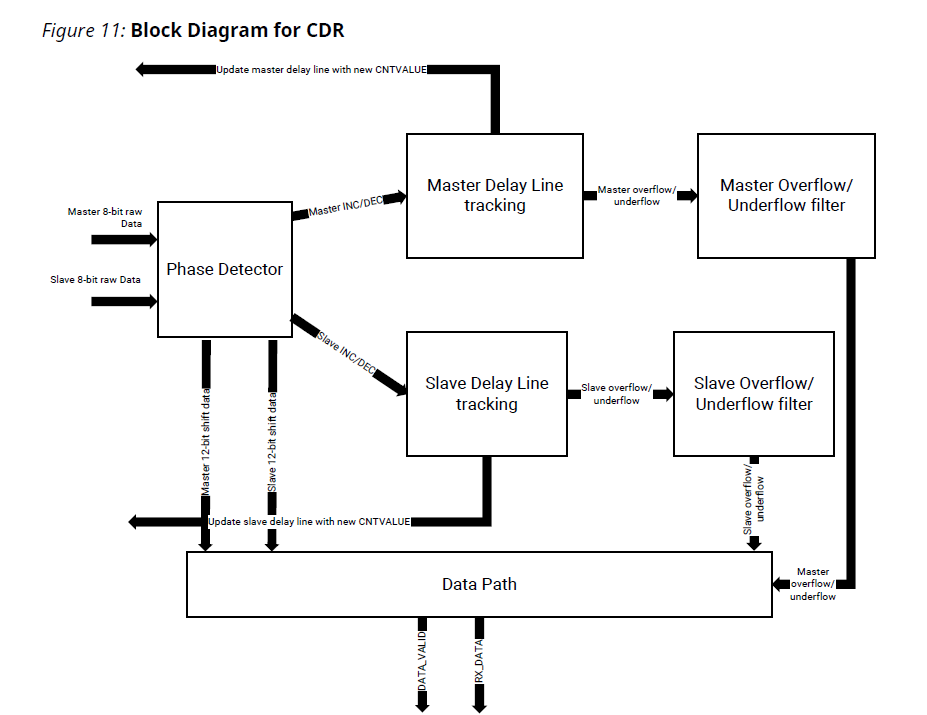

3.2異步模式下CDR架構

CDR的目的是確保UI采樣始終處于異步信號數據的中心位置。UI的采樣需要與數據速率相同頻率的時鐘完成。如SGMII數據速率為1250MBps,則RX和TX鎖相環時鐘頻率應為1250MHz。在CDR with ppm difference情況下,系統要求本地時鐘與數據速率原本的時鐘ppm差不超過100ppm。

CDR主要包含以下四大模塊:

Phase detector

Delay line tracking

Datapath

1 Phase detector

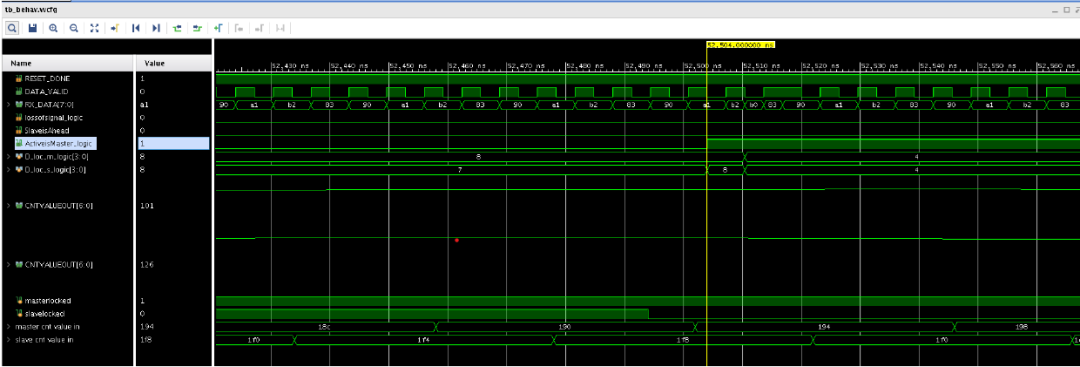

Phase detector擁有master delay line和slave delayline兩套延遲線檢測機制,兩套機制同時工作,互為補充,將最大程度保證CDR能成功鎖定。

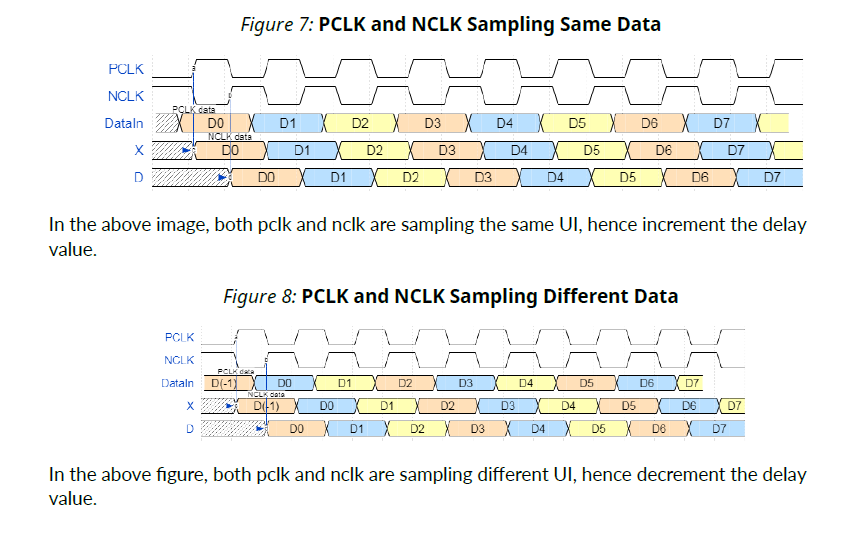

主延遲線和從延遲線對于每個UI,分別取兩個樣本,送入alexander pangpang鑒相電路,根據獲取的數據信息,選擇增加或減少延遲。

當差分時鐘的p端和n端上升沿采到同一個UI sample,next step增加延時;當p端和n端上升沿采到不同UI sample,next step減少延時。

2 delay line tracking

延遲值在phase dectector模塊中不斷變化,定期更新到delay line tracking模塊中;在delay line tracking模塊中,我們會不斷跟蹤延遲線的變化情況。

經過不斷的統計和分析,一旦我們認為從PHY接收到D樣本位于UI的中心則當前的延遲線和bitslice被鎖定,若一直沒有達到UI的中心位置,將會一直調整delay line直到達到邊界。到達邊界,就會產生overflow和underflow信號。

因此,overflow和underflow在調試中,具有很強的指導意義,我們可以通過overflow和underflow信號,判斷CDR是否達到鎖定狀態。

3 underflow overlow filter

該模塊負責正確選擇數據并提供給輸出。一旦兩個延遲線都被鎖定,它們自然相隔?個UI,當鎖定發生,延遲較少的延遲線,將成為active bitslice,數據將從該延遲線輸出,另外一條延遲線將成為備選的monitor bitslice。

當active bitslice發生overflow或underflow時,會自動切換到monitor bitslice獲取有效數據,而此時,如果monitor bitslice也發生overflow或underflow,兩套機制都無法鎖定的情況下,CDR會真正失鎖,系統將無法采集到正確的數據。

4 CustomCDR模式

在異步模式下,如果IP自帶的CDR無法滿足使用需求,客戶也可以考慮使能customCDR,參考example design去完成自定義的CDR,取得更大的靈活性;在customCDR模式下,我們完整開放XPHY的延遲配置接口,客戶可以根據自己的需求靈活設計自定義的CDR模塊。

4advanced io planner

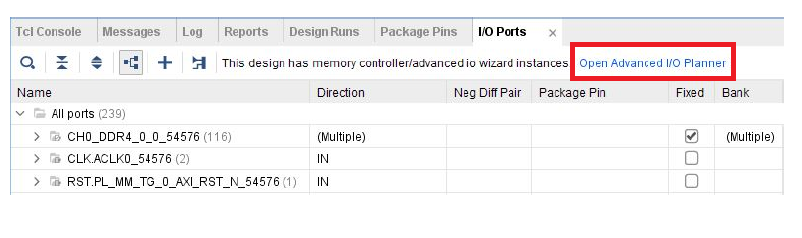

為了更合理的利用XPHY的資源,AMD建議通過advanced io planner來規劃IO分配,工具是基于集中式硬件規則盡可能的優化安排的。

工程經過綜合之后,點擊紅色框位置,激活advaned I/O Planner

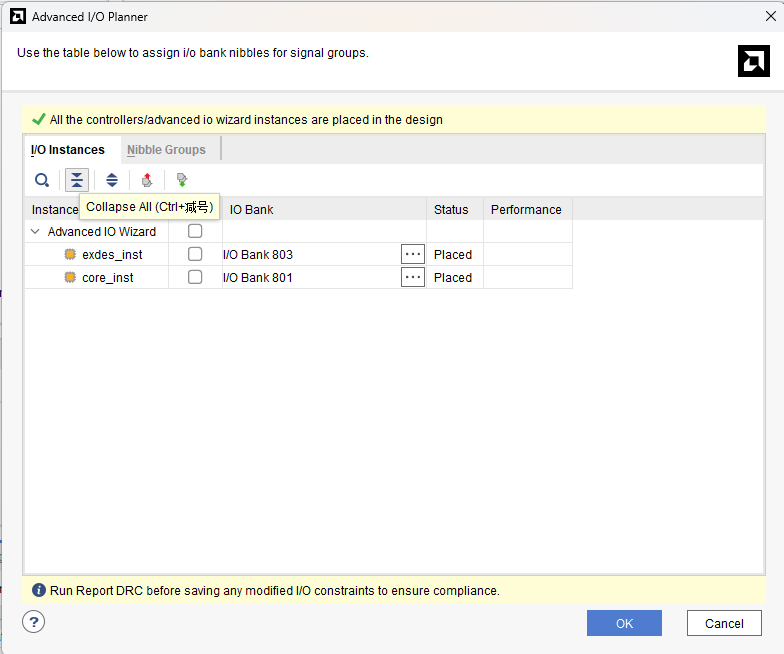

用戶可以選擇自動分配,也可以手動進行調整,在IO instances下面工具已經完成自動分配

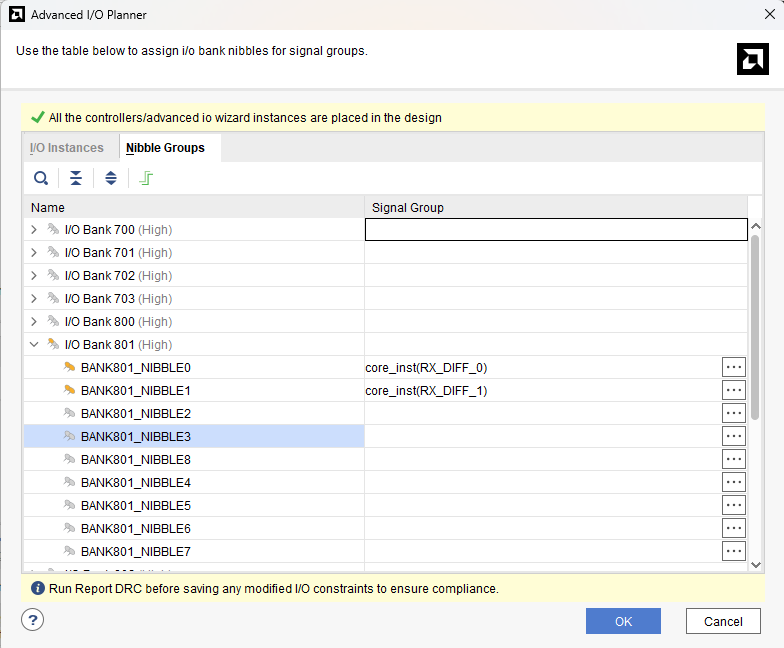

若需要手動調整,在nibble group菜單下面,手動選擇你需要放置的nibble

5調試要點

IP調試過程中的幾點經驗總結如下:

1. advanced io wizard IP無法輸出有效數據,data valid不能正常拉高:請檢查本地時鐘與源端時鐘的ppm差,不能大于100ppm;

2. 當采集到的數據出現錯誤或者位移,可以使能enable debug port,觀察是否有出現overflow和underflow的情況,是否存在master delay line和slave delay line切換或者失去鎖定的痕跡,幫助確認CDR的鎖定狀態。

關于安富利

安富利是全球領先的技術分銷商和解決方案提供商,在過去一個多世紀里一直秉持初心,致力于滿足客戶不斷變化的需求。通過遍布全球的專業化和區域化業務覆蓋,安富利可在產品生命周期的每個階段為客戶和供應商提供支持。安富利能夠幫助各種類型的公司適應不斷變化的市場環境,在產品開發過程中加快設計和供應速度。安富利在整個技術價值鏈中處于中心位置,這種獨特的地位和視角讓其成為了值得信賴的合作伙伴,能夠幫助客戶解決復雜的設計和供應鏈難題,從而更快地實現營收。

-

時鐘

+關注

關注

11文章

1896瀏覽量

133162 -

Advanced

+關注

關注

1文章

35瀏覽量

23515 -

UltraScale

+關注

關注

0文章

122瀏覽量

31892 -

異步模式

+關注

關注

0文章

2瀏覽量

687

原文標題:AMD技術干貨|Advanced IO wizard異步模式

文章出處:【微信號:AvnetAsia,微信公眾號:安富利】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

異步IO是什么

《Linux設備驅動開發詳解》第9章、Linux設備驅動中的異步通知與異步IO

一文看懂異步傳輸模式atm的特點

一文詳解Advanced IO wizard異步模式

一文詳解Advanced IO wizard異步模式

評論