差分晶振在高速 FPGA 設(shè)計(jì)中具有非常重要的應(yīng)用,尤其是在對時(shí)鐘精度、抗干擾能力、信號(hào)完整性要求高的系統(tǒng)中,比如:

· 高速串行接口(PCIe、SFP+/QSFP、10G Ethernet、DDR4/DDR5)

· 多通道數(shù)據(jù)采集系

· 高速通信系統(tǒng)(SerDes)

· 精確同步系統(tǒng)(時(shí)間戳、ADC/DAC 驅(qū)動(dòng))

一、什么是差分晶振?

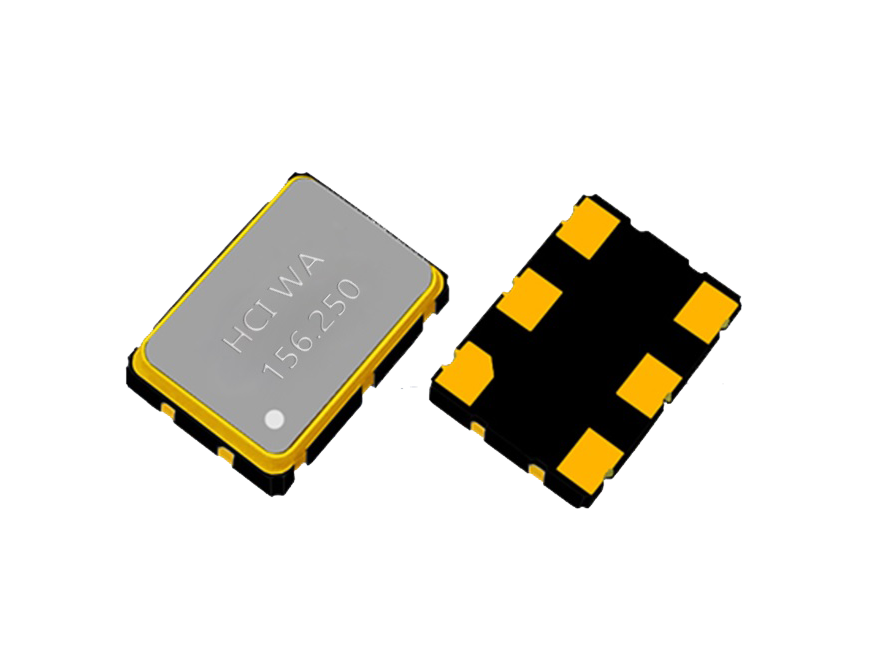

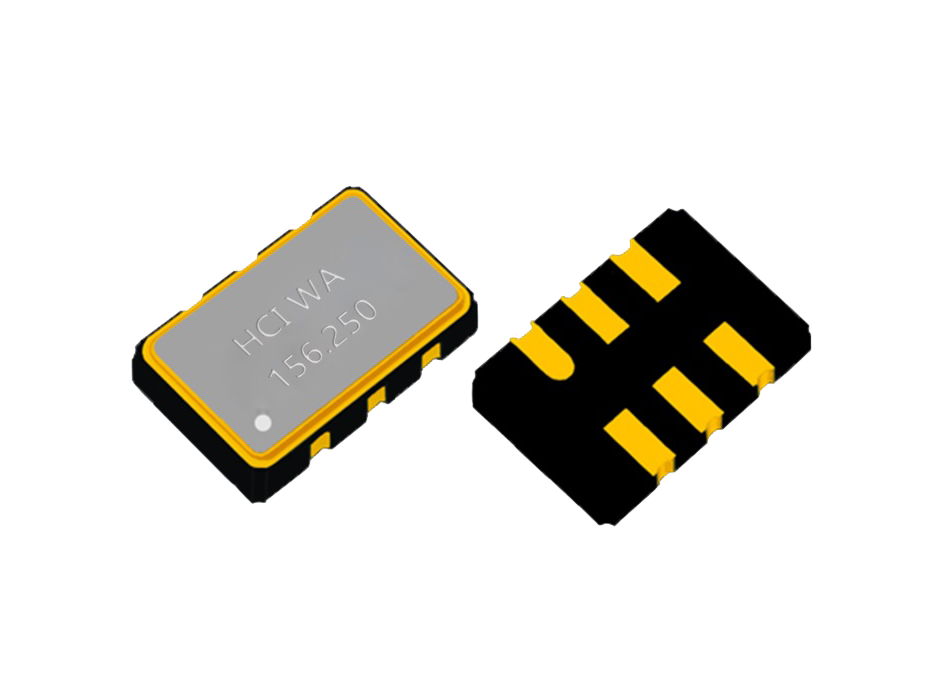

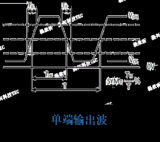

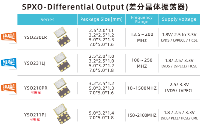

差分晶振(Differential Oscillator)是一種輸出差分信號(hào)(如 LVDS、LVPECL、HCSL)的有源晶體振蕩器,其輸出兩個(gè)互為反相的時(shí)鐘信號(hào)(CLK+ 和 CLK?)。它不同于傳統(tǒng)的單端晶振(如 CMOS 輸出的 Oscillator)。

二、差分信號(hào)的優(yōu)勢:

| 特性 | 差分信號(hào) | 單端信號(hào) |

|---|---|---|

| 抗干擾能力 | 強(qiáng)(共模噪聲抵消) | 弱 |

| 信號(hào)完整性 | 好,易于傳輸高速信號(hào) | 差 |

| 驅(qū)動(dòng)能力 | 高,適合遠(yuǎn)距離/高速傳輸 | 低 |

| 抖動(dòng)性能 | 更低 | 相對較高 |

三、差分晶振在高速 FPGA 上的應(yīng)用

1. 作為高速接口參考時(shí)鐘

PCIe、10G/25G Ethernet、SATA 等高速接口必須使用差分參考時(shí)鐘;

通常使用 100 MHz 或 156.25 MHz 差分晶振(如 HCSL/LVDS 輸出);

FPGA 內(nèi)部的 GTX/GTH/GTP 等高速收發(fā)器模塊(Transceivers) 需要這些差分參考時(shí)鐘。

典型連接:

差分晶振 → FPGA GTREFCLK0/1 (高速收發(fā)器參考時(shí)鐘引腳)

2. 時(shí)鐘樹的核心時(shí)鐘源

多通道高速系統(tǒng)中,使用差分晶振驅(qū)動(dòng)一個(gè)時(shí)鐘分配芯片(如 SI5341/AD9528),再輸出多個(gè)同步時(shí)鐘;

適用于多 ADC、DAC、FPGA 通信時(shí)鐘對齊。

結(jié)構(gòu)示意:

差分晶振 → 時(shí)鐘管理芯片 (如 PLL / Fanout Buffer)

↓

多個(gè)同步時(shí)鐘→ FPGA/ADC/DAC

3. 驅(qū)動(dòng) FPGA 內(nèi)部 PLL/MMCM

差分晶振可用于提供高品質(zhì)時(shí)鐘輸入(如通過 IBUFDS 接口進(jìn)入 FPGA),再由內(nèi)部 PLL/MMCM 輸出系統(tǒng)各模塊時(shí)鐘;提升時(shí)鐘質(zhì)量,降低整體系統(tǒng)時(shí)鐘抖動(dòng)。

常見差分輸出類型與 FPGA 兼容性

| 輸出類型 | 典型應(yīng)用 | FPGA 接口兼容性 |

|---|---|---|

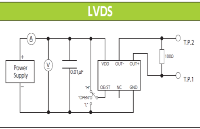

| LVDS | 通用差分晶振輸出類型 | 所有主流FPGA 支持(GTX/GTH 輸入) |

| HCSL | PCIe、服務(wù)器主板用 | 直接支持(如Xilinx PCIe IP 核) |

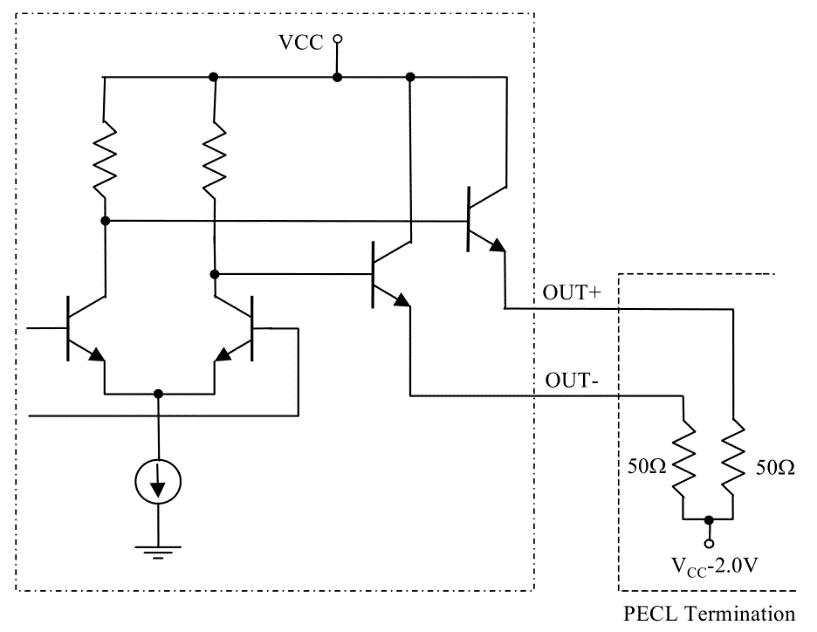

| LVPECL | 高頻、高擺幅應(yīng)用 | 需要外部終端匹配和偏置電阻 |

| CML | 超高速鏈路(>10 Gbps) | 高端FPGA 收發(fā)器支持 |

? 建議根據(jù) FPGA 廠商推薦使用匹配的差分輸出類型。

四、差分晶振選型建議

| 參數(shù) | 建議值 |

|---|---|

| 頻率穩(wěn)定度 | ±25 ppm 或更優(yōu) |

| 相位抖動(dòng)(12kHz–20MHz) | < 1ps RMS(高速接口要求) |

| 輸出類型 | LVDS/HCSL 優(yōu)先,取決于 FPGA 兼容性 |

| 負(fù)載能力 | 驅(qū)動(dòng)能力≥ 15pF 或與時(shí)鐘芯片匹配 |

| 溫度范圍 | 工業(yè)級(jí)(-40°C ~ +85°C)或更寬 |

優(yōu)先選擇協(xié)議推薦頻率:

PCIe:100 MHz;

SFP+/10G Ethernet:156.25 MHz;

25G/40G Ethernet:312.5 MHz;

JESD204B/C:250 MHz、312.5 MHz、625 MHz 等。

參考 FPGA 官方文檔推薦時(shí)鐘范圍;

抖動(dòng)指標(biāo)要低:

特別重要于 PCIe、JESD204C、10G/25G Ethernet。

五、差分晶振在高速 FPGA 上的常用頻率

| 頻率(MHz) | 應(yīng)用場景 | 備注 |

|---|---|---|

| 100 MHz | PCIe Gen1/Gen2;通用高速邏輯系統(tǒng) | 非常常見,支持HCSL/LVDS |

| 125 MHz | Gigabit Ethernet(千兆網(wǎng)) | 適用于GMII、SGMII 等接口 |

| 156.25 MHz | 10G Ethernet(10GBASE-R/XAUI)、SFP+、QSFP、CEI 接口等 | 高速串行通信標(biāo)準(zhǔn)頻率 |

| 200 MHz | DDR4 時(shí)鐘、多速率收發(fā)器參考頻率 | 通常用于倍頻生成更高時(shí)鐘 |

| 212.5 MHz | JESD204B/C 數(shù)據(jù)轉(zhuǎn)換鏈路 | 高頻采集通信接口標(biāo)準(zhǔn)頻率 |

| 250 MHz | 高速ADC/DAC 系統(tǒng)、部分 JESD204C 系統(tǒng) | 抖動(dòng)要求更嚴(yán)格 |

| 312.5 MHz | 25G Ethernet(25GBASE-R)、高速光通信系統(tǒng) | 差分輸出常為CML/LVPECL |

| 322.265625 MHz | CPRI(6.144 Gbps)參考時(shí)鐘 | 通信基站FPGA 用 |

| 644.53125 MHz | CPRI(12.288 Gbps)、JESD204C 高速鏈路 | 極高速接口,需要極低抖動(dòng)晶振 |

| Others(用戶自定義) | 特定頻率輸入給PLL,再生成目標(biāo)頻率 | 需確認(rèn)PLL 支持倍頻因子 |

? 具體型號(hào)建議聯(lián)系杭晶銷售或技術(shù)工程師推薦使用匹配的差分輸出類型。

六、總結(jié)

| 項(xiàng)目 | 差分晶振的優(yōu)勢 |

|---|---|

| 精度 | 抖動(dòng)低,頻率穩(wěn)定 |

| 抗干擾 | 強(qiáng),共模噪聲抑制好 |

| 速度 | 支持GHz 級(jí)高速傳輸 |

| 應(yīng)用 | PCIe、SFP、DDR4/5、ADC、DAC、同步系統(tǒng)等 |

差分晶振在現(xiàn)代高速 FPGA 系統(tǒng)中幾乎是標(biāo)配,是確保系統(tǒng)高速通信與同步性能的關(guān)鍵器件。

如果你有具體的 FPGA 型號(hào) (如 Xilinx Zynq Ultrascale+、Intel Stratix 10)、差分晶振型號(hào),或通信接口需求(如 PCIe Gen3/SFP+),蘇州杭晶可以幫你推薦最合適的時(shí)鐘配置方案與原理圖連接設(shè)計(jì)。

審核編輯 黃宇

-

FPGA

+關(guān)注

關(guān)注

1645文章

22034瀏覽量

617958 -

晶振

+關(guān)注

關(guān)注

35文章

3254瀏覽量

70053 -

差分晶振

+關(guān)注

關(guān)注

0文章

146瀏覽量

722

發(fā)布評(píng)論請先 登錄

一探究竟差分晶振

MG7050EAN存儲(chǔ)器6G應(yīng)用晶振,X1M0004110020,EPSON差分晶振

0.6ps抖動(dòng)!高速通信時(shí)鐘黑科技,可編程差分晶振,1天交付!#電路知識(shí) #差分信號(hào) #差分晶振 #電工

愛普生差分晶振SG2520EGN(X1G005881)在高速光模塊通信中的應(yīng)用

愛普生差分晶振SG2016EHN(X1G006141)在高速通信網(wǎng)絡(luò)中的應(yīng)用

YXC晶振有哪些型號(hào),適用于ai領(lǐng)域? #差分晶振 #YXC晶振 #YXC #揚(yáng)興科技

CDCLVP1208RHDR的差分輸入管腳外接差分晶振,需要區(qū)分差分晶振時(shí)鐘的P和N嗎?

愛普生(EPSON) 差分晶振(SPXO)

差分晶振電氣參數(shù)簡介

愛普生SG7050VAN 212.5MHz差分晶振高速數(shù)字信號(hào)處理器理想之選

YXC揚(yáng)興差分可編程晶振,頻點(diǎn)10MHZ,頻差±50ppm,LVDS輸出,應(yīng)用于AI服務(wù)器

差分晶振在高速 FPGA 上的應(yīng)用

差分晶振在高速 FPGA 上的應(yīng)用

評(píng)論